REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

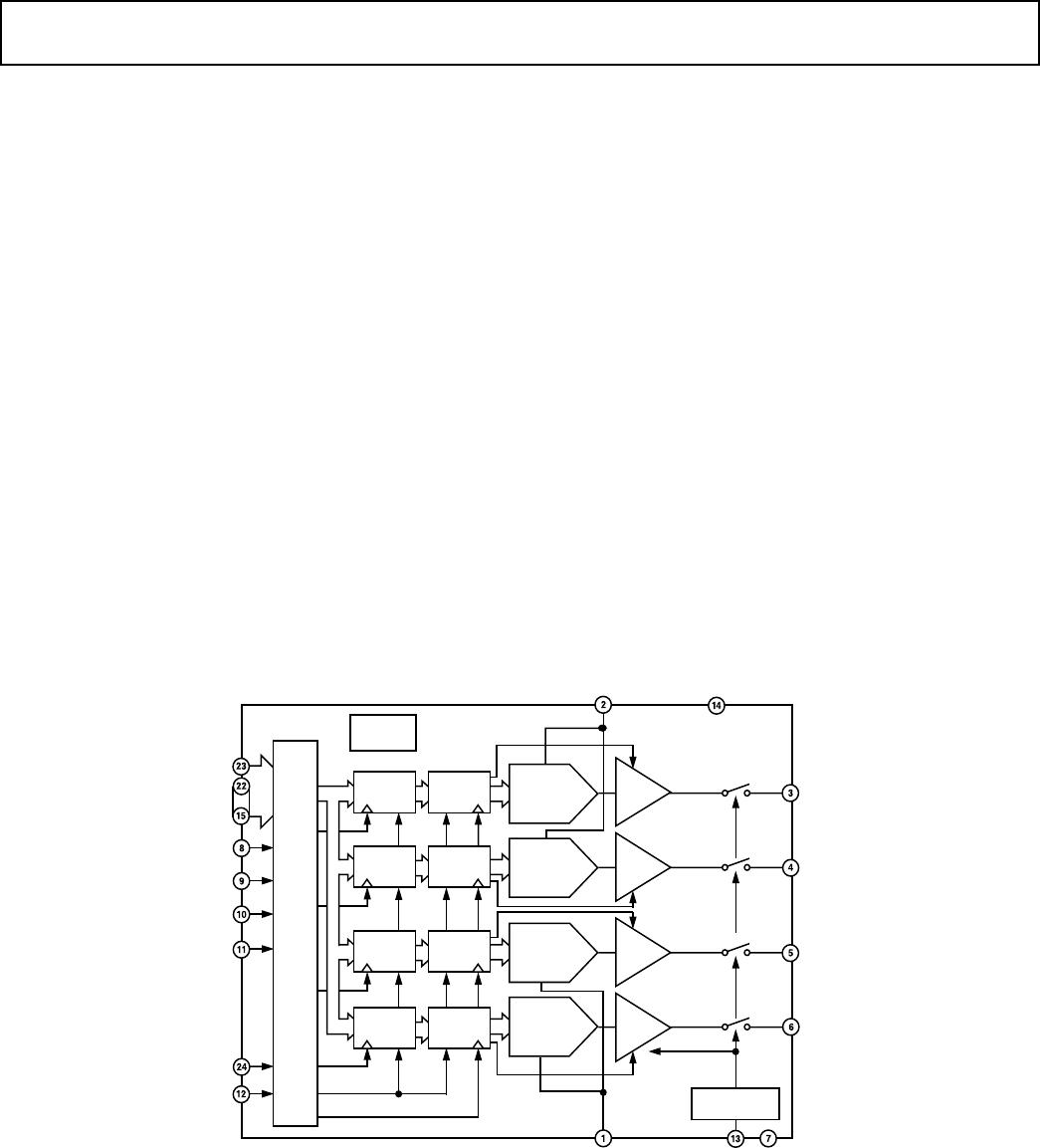

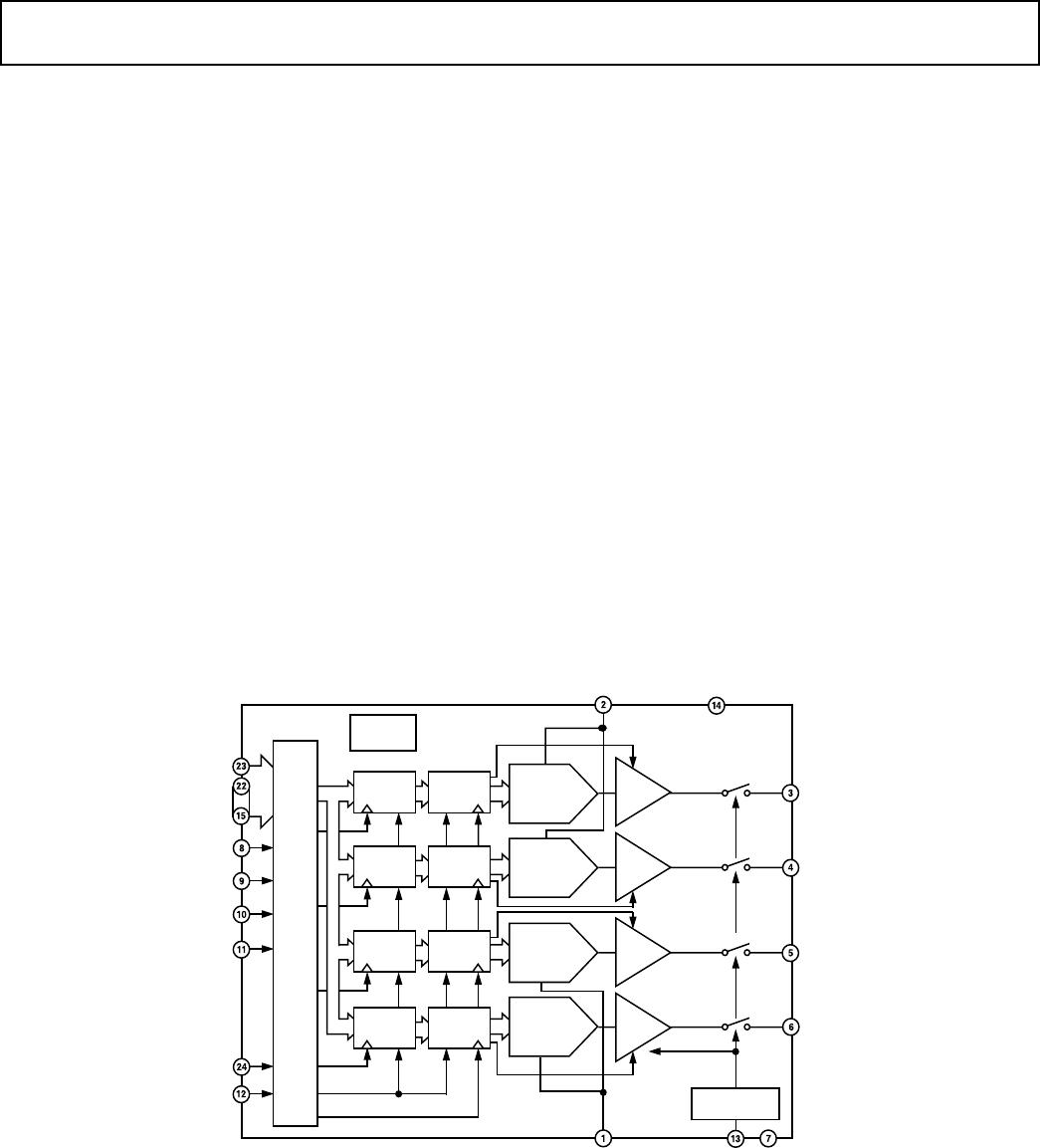

AD5334/AD5335/AD5336/AD5344*

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

2.5 V to 5.5 V, 500 A, Parallel Interface

Quad Voltage-Output 8-/10-/12-Bit DACs

AD5334 FUNCTIONAL BLOCK DIAGRAM

(Other Diagrams Inside)

V

OUT

A

BUFFER

GND

AD5334

V

OUT

B

BUFFER

V

OUT

C

BUFFER

V

OUT

D

BUFFER

POWER-ON

RESET

TO ALL DACS

AND BUFFERS

POWER-DOWN

LOGIC

PD

DAC

REGISTER

8-BIT

DAC

8-BIT

DAC

INPUT

REGISTER

V

REF

C/D

INTER-

FACE

LOGIC

V

DD

V

REF

A/B

GAIN

DB

7

DB

0

CS

WR

A0

A1

CLR

LDAC

.

.

.

DAC

REGISTER

INPUT

REGISTER

DAC

REGISTER

INPUT

REGISTER

DAC

REGISTER

INPUT

REGISTER

8-BIT

DAC

8-BIT

DAC

8-BIT

DAC

FEATURES

AD5334: Quad 8-Bit DAC in 24-Lead TSSOP

AD5335: Quad 10-Bit DAC in 24-Lead TSSOP

AD5336: Quad 10-Bit DAC in 28-Lead TSSOP

AD5344: Quad 12-Bit DAC in 28-Lead TSSOP

Low Power Operation: 500 A @ 3 V, 600 A @ 5 V

Power-Down to 80 nA @ 3 V, 200 nA @ 5 V via PD Pin

2.5 V to 5.5 V Power Supply

Double-Buffered Input Logic

Guaranteed Monotonic by Design Over All Codes

Output Range: 0–V

REF

or 0–2 V

REF

Power-On Reset to Zero Volts

Simultaneous Update of DAC Outputs via LDAC Pin

Asynchronous CLR Facility

Low Power Parallel Data Interface

On-Chip Rail-to-Rail Output Buffer Amplifiers

Temperature Range: –40ⴗC to +105ⴗC

APPLICATIONS

Portable Battery-Powered Instruments

Digital Gain and Offset Adjustment

Programmable Voltage and Current Sources

Programmable Attenuators

Industrial Process Control

GENERAL DESCRIPTION

The AD5334/AD5335/AD5336/AD5344 are quad 8-, 10-, and

12-bit DACs. They operate from a 2.5 V to 5.5 V supply con-

suming just 500 µA at 3 V, and feature a power-down mode that

further reduces the current to 80 nA. These devices incorporate

an on-chip output buffer that can drive the output to both sup-

ply rails.

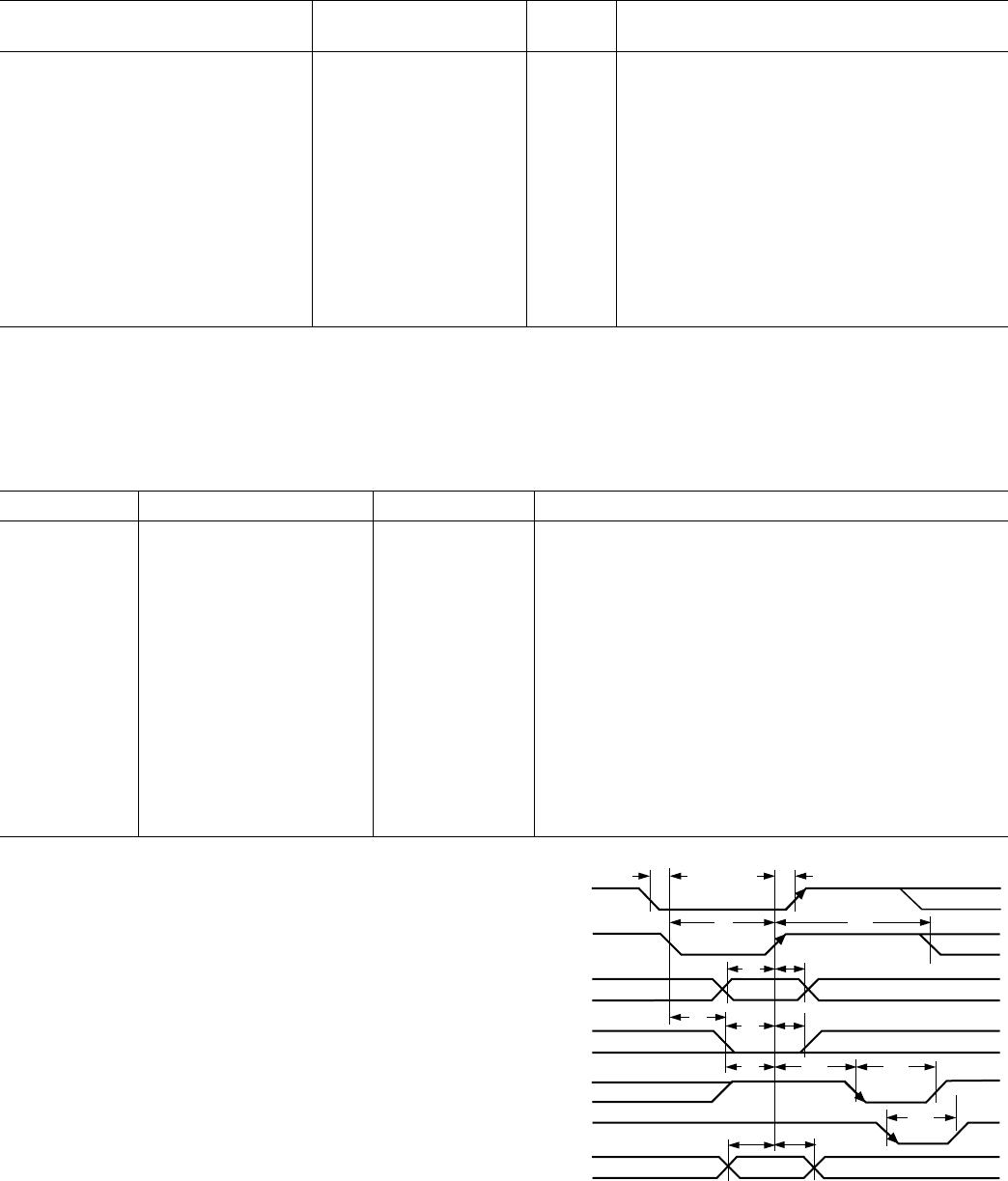

The AD5334/AD5335/AD5336/AD5344 have a parallel interface.

CS selects the device and data is loaded into the input registers

on the rising edge of WR.

The GAIN pin on the AD5334 and AD5336 allows the output

range to be set at 0 V to V

REF

or 0 V to 2 × V

REF

.

Input data to the DACs is double-buffered, allowing simultaneous

update of multiple DACs in a system using the LDAC pin.

On the AD5334, AD5335 and AD5336 an asynchronous CLR

input is also provided. This resets the contents of the Input

Register and the DAC Register to all zeros. These devices also

incorporate a power-on-reset circuit that ensures that the DAC

output powers on to 0 V and remains there until valid data is

written to the device.

The AD5334/AD5335/AD5336/AD5344 are available in Thin

Shrink Small Outline Packages (TSSOP).

*Protected by U.S. Patent Number 5,969,657