Document Number: 001-65659 Rev. *I Page 15 of 26

Pin Configuration Options

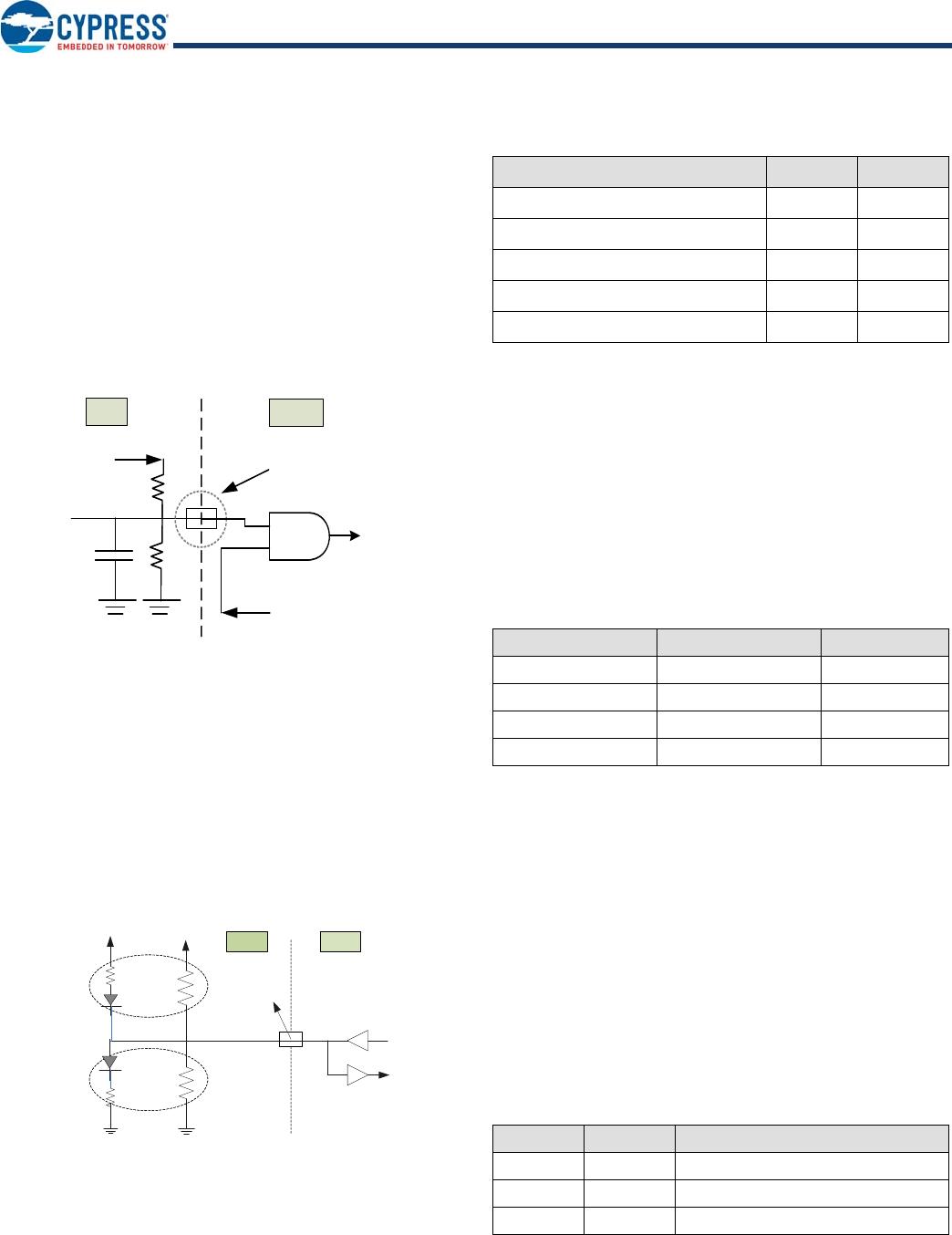

Power ON Reset

The power on reset can be triggered by external reset or internal

circuitry. The internal reset is initiated, when there is an unstable

power event for silicon’s internal core power (3.3 V ± 10%). The

internal reset is released 2.7 µs ± 1.2% after supply reaches

power good voltage (2.5 V to 2.8 V). The external reset pin,

continuously senses the voltage level (5 V) on the upstream

VBUS as shown in the figure. In the event of USB plug/unplug or

drop in voltage, the external reset is triggered. This reset trigger

can be configured using the resistors R1 and R2. Cypress

recommends that the reset time applied in external reset circuit

should be longer than that of the internal reset time.

Gang/Individual Power Switching Mode

A single pin is used to set individual / gang mode as well as

output the suspend flag. This is done to reduce the pin count.

The individual or gang mode is decided within 20 µs after power

on reset. It has a setup time of 1ns. 50 to 60ms after reset, this

pin is changed to output mode. CY7C65642 outputs the suspend

flag, once it is globally suspended. Pull-down resistor of greater

than 100K is needed for Individual mode and a pull-up resistor

greater than 100K is needed for Gang mode. Figure below

shows the suspend LED indicator schematics. The polarity of

LED must be followed, otherwise the suspend current will be

over the spec limitation (2.5 mA).

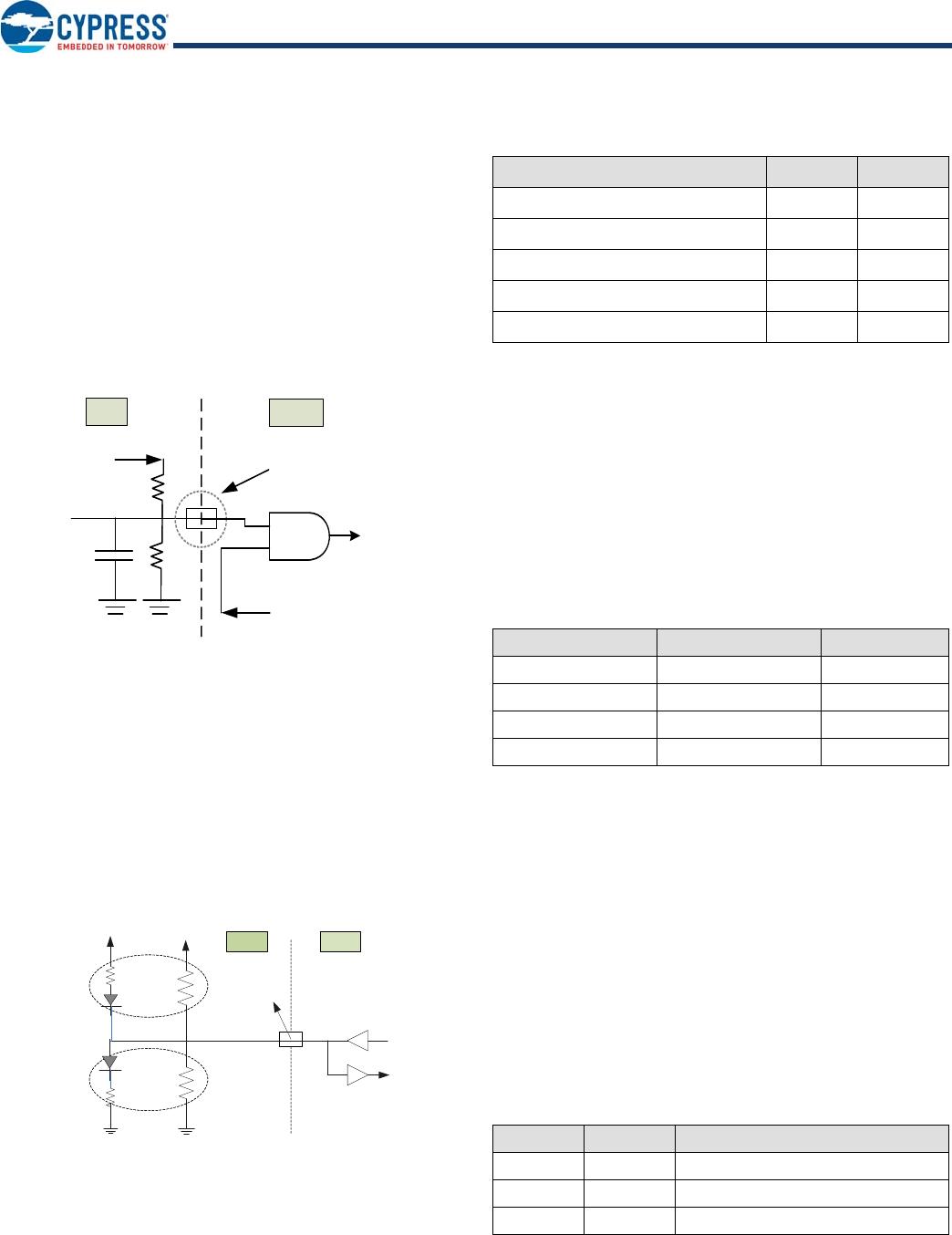

Power Switch Enable Pin Polarity

The pin polarity is set active-high by pin-strapping the

PWR_PIN_POL pin to 1 and Active-Low by pin-strapping the

PWR_PIN_POL pin to 0. Thus, both kinds of power switches

are supported. This feature is not supported in 28-pin QFN

package.

Port Number Configuration

In addition to the EEPROM configuration, as described

above, configuring the hub for 2/3/4 ports is also supported

using pin-strapping SET_PORT_NUM1 and

SET_PORT_NUM2, as shown in following table.Pin strapping

option is not supported in the 28-pin QFN package.

Non Removable Ports Configuration

In embedded systems, downstream ports that are always

connected inside the system, can be set as non-removable

(always connected) ports, by pin-strapping the corresponding

FIXED_PORT# pins 1~4 to High, before power on reset. At POR,

if the pin is pull high, the corresponding port is set to

non-removable. This is not supported in the 28-pin QFN

package.

Reference Clock Configuration

This hub can support, optional 27/48-MHz clock source. When

on-board 27/48-MHz clock is present, then using this feature,

system integrator can further reduce the BOM cost by eliminating

the external crystal. This is available through GPIO pin

configuration shown below. This is not supported in the 28-pin

QFN package.

Global

Reset#

Int. 3.3V power-good

detection circuit input

(USB PHY reset)

Ext. VBUS power-good

detection circuit input

(Pin"RESET#")

VBUS

(External 5V)

R1

R2

INT

EXT

PCB

Silicon

0 : INDIVIDUAL MODE

1: GANG MODE

SUSPEND OUT

VDD (3.3V)

SUSPEND

INDICATOR

VDD (3.3V)

100K

100K

GANG/SUSPEND

SiliconPCB

GANG MODE

INDIVIDUAL MODE

Table 1. Features supported in 48-pin and 28-pin packages

Supported Features 48-pin 28-pin

Port number configuration Yes No

Non-removable port configuration Yes No

Reference clock configuration Yes No

Power switch enable polarity Yes No

LED Indicator Yes No

SET_PORT_NUM2 SET_PORT_NUM1 # Ports

1 1 1 (Port 1)

1 0 2 (Port 1/2)

0 1 3 (Port 1/2/3)

0 0 4 (All ports)

SEL48 SEL27 Clock Source

0 1 48-MHz OSC-in

1 0 27-MHz OSC-in

1 1 12-MHz X’tal/OSC-in