Data Sheet AD7873

Rev. F | Page 19 of 28

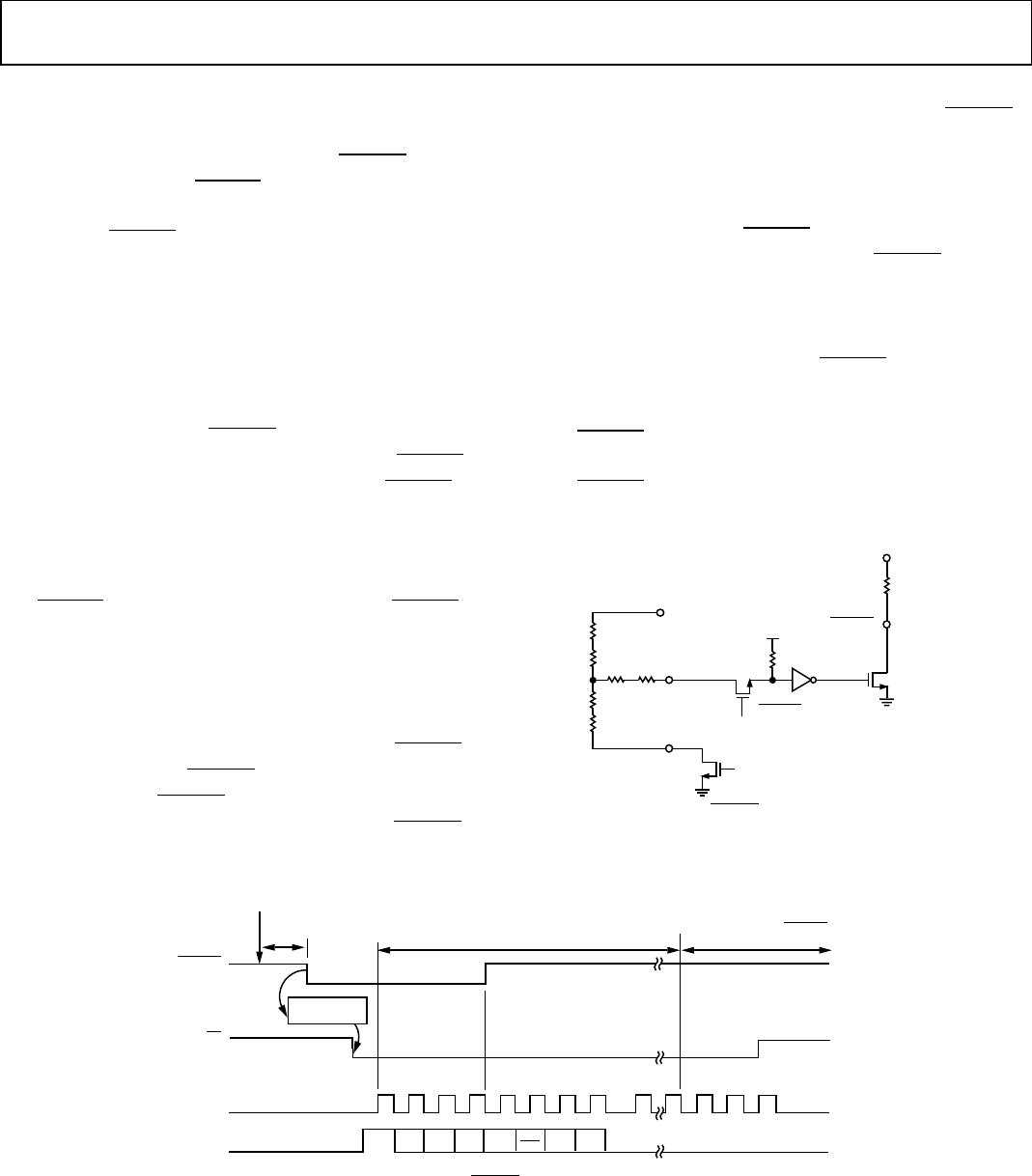

CONTROL REGISTER

The control word provided to the ADC via the DIN pin is

shown in Tabl e 7. This provides the conversion start, channel

addressing, ADC conversion resolution, configuration, and

power-down of the AD7873. Table 7 provides detailed

information on the order and description of these control bits

within the control word.

Initiate START

The first bit, the S bit, must always be set to 1 to initiate the start

of the control word. The AD7873 ignores any inputs on the

DIN line until the start bit is detected.

Channel Addressing

The next three bits in the control register, A2, A1, and A0, select

the active input channel(s) of the input multiplexer (see Table 6

and Figure 26), touch screen drivers, and the reference inputs.

Mode

The MODE bit sets the resolution of the analog-to-digital

converter. With a 0 in this bit, the following conversion has

12 bits of resolution. With a 1 in this bit, the following

conversion has eight bits of resolution.

SER/

DFR

The SER/

DFR

bit controls the reference mode, set to either

single-ended or differential when a 1 or a 0 is written to this bit,

respectively. The differential mode is also referred to as the

ratiometric conversion mode. This mode is optimum for

X-position, Y-position, and pressure-touch measurements. The

reference is derived from the voltage at the switch drivers,

which is almost the same as the voltage to the touch screen. In

this case, a separate reference voltage is not needed because the

reference voltage to the ADC is the voltage across the touch

screen. In single-ended mode, the reference voltage to the

converter is always the difference between the V

REF

and GND

pins. See Table 6 and Figure 26 through Figure 29 for further

information.

If X-position, Y-position, and pressure touch are measured in

single-ended mode, an external reference voltage or +V

CC

is

required for maximum dynamic range. The internal reference

can be used for these single-ended measurements; however, a

loss in dynamic range is incurred. If an external reference is

used, the AD7873 should also be powered from the external

reference. Because the supply current required by the device is

so low, a precision reference can be used as the supply source to

the AD7873. It might also be necessary to power the touch

screen from the reference, which can require 5 mA to 10 mA. A

REF19x voltage reference can source up to 30 mA, and, as such,

could supply both the ADC and the touch screen. Care must be

taken, however, to ensure that the input voltage applied to the

ADC does not exceed the reference voltage and therefore the

supply voltage. See the Absolute Maximum Ratings section.

Note that the differential mode can only be used for X-position,

Y-position, and pressure touch measurements. All other

measurements require single-ended mode.

PD0 and PD1

The power management options are selected by programming

the power management bits, PD0 and PD1, in the control

register. Table 8 summarizes the options available and the

internal reference voltage configurations. The internal reference

can be turned on or off independent of the analog-to-digital

converter, allowing power saving between conversions using the

power management options. On power-up, PD0 defaults to 0,

while PD1 defaults to 1.

LSB

S A2 A1 A0 MODE SER/DFR PD1 PD0

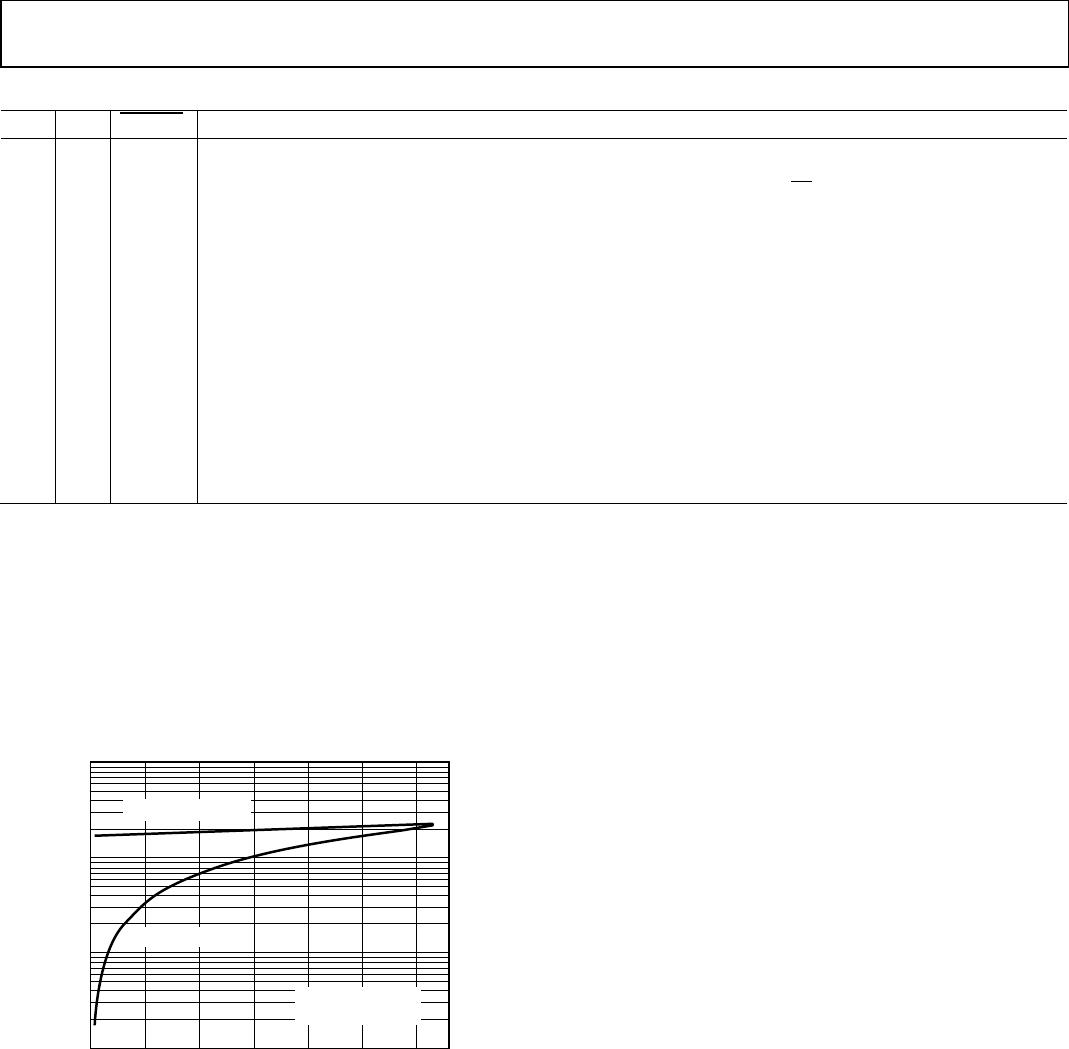

Table 7. Control Register Bit Function Description

Bit No. Mnemonic Comment

7 S

Start Bit. The control word starts with the first high bit on DIN. A new control word can start every 15th DCLK cycle

when in the 12-bit conversion mode or every 11th DCLK cycle when in 8-bit conversion mode.

6 to 4 A2 to A0

Channel Select Bits. These three address bits along with the SER/DFR bit control the setting of the multiplexer

input, switches, and reference inputs, as detailed in Table 6.

3 MODE

12-Bit/8-Bit Conversion Select Bit. This bit controls the resolution of the following conversion. With a 0 in this bit,

the conversion has 12-bit resolution or, with a 1 in this bit, 8-bit resolution.

2

SER/

DFR Single-Ended/Differential Reference Select Bit. Together with Bit A2 to Bit A0, this bit controls the setting of the

multiplexer input, switches, and reference inputs as described in Table 6.

Power Management Bits. These two bits decode the power-down mode of the AD7873 as shown in Table 8.