Data Sheet AD7873

Rev. F | Page 7 of 28

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

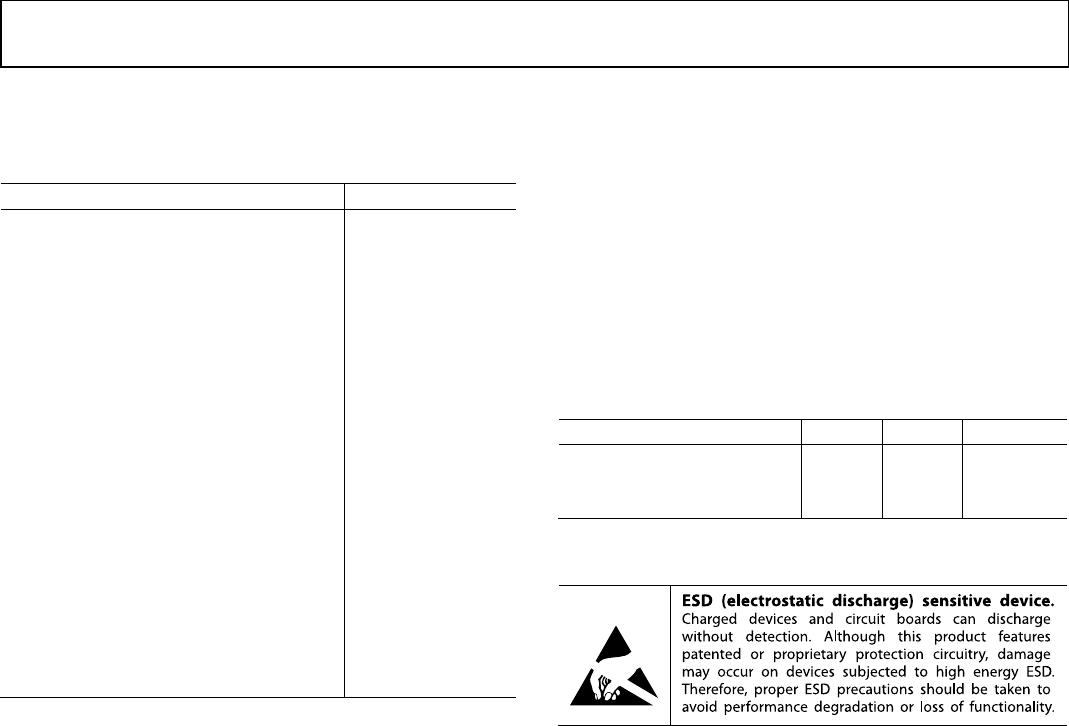

Figure 3. LFCSP Pin Configuration

Figure 4. QSOP/TSSOP Pin Configuration

Table 5. Pin Function Descriptions

Pin No.

Mnemonic

Description

LFCSP

QSOP/

TSSOP

3, 10 1, 10 +V

CC

Power Supply Input. The +V

CC

range for the AD7873 is from 2.2 V to 5.25 V. Both +V

CC

pins should be

connected directly together.

11 2 X+ X+ Position Input. ADC Input Channel 1.

12 3 Y+ Y+ Position Input. ADC Input Channel 2.

13 4 X– X– Position Input.

14 5 Y– Y– Position Input. ADC Input Channel 3.

15 6 GND

Analog Ground. Ground reference point for all circuitry on the AD7873. All analog input signals

and any external reference signals should be referred to this GND voltage.

16 7 V

BAT

Battery Monitor Input. ADC Input Channel 4.

1 8 AUX Auxiliary Input. ADC Input Channel 5.

2 9 V

REF

Reference Output for the AD7873. Alternatively, an external reference can be applied to this input.

The voltage range for the external reference is 1.0 V to +V

CC

. For specified performance, it is 2.5 V on

the AD7873. The internal 2.5 V reference is available on this pin for use external to the device. The

reference output must be buffered before it is applied elsewhere in a system. A 0.1 µF capacitor is

recommended between this pin and GND to reduce system noise effects.

4 11

PENIRQ

Pen Interrupt. CMOS logic open-drain output (requires 10 kΩ to 100 kΩ pull-up resistor externally).

5 12 DOUT

Data Out. Logic output. The conversion result from the AD7873 is provided on this output as a

serial data stream. The bits are clocked out on the falling edge of the DCLK input. This output is

high impedance when

CS is high.

6 13 BUSY

BUSY Output. Logic output. This output is high impedance when

CS is high.

7 14 DIN

Data In. Logic Input. Data to be written to the AD7873 control register is provided on this input and

is clocked into the register on the rising edge of DCLK (see the Control Register section).

8 15

CS Chip Select Input. Active low logic input. This input provides the dual function of initiating

conversions on the AD7873 and enabling the serial input/output register.

9 16 DCLK

External Clock Input. Logic input. DCLK provides the serial clock for accessing data from the part.

This clock input is also used as the clock source for the AD7873 conversion process.

N/A

1

EPAD

Exposed Pad. The exposed pad is not connected internally. For increased reliability of the solder

joints and maximum thermal capability, it is recommended that the pad be soldered to the ground

plane.

1

N/A = not applicable.

AUX

V

REF

+V

CC

PENIRQ

X+

Y+

+V

CC

DCLK

DOUT

BUSY

DIN

CS

GND

V

BAT

Y–

X–

02164-003

12

11

10

1

3

4

9

2

6

5

7

8

16

15

14

13

NOTES

1. THE EXPOSED PAD IS NOT CONNECTED INTERNALLY.

FOR INCREASED RELIABILITY OF THE SOLDER JOINTS

AND MAXIMUM THERMAL CAPABILITY, IT IS

RECOMMENDED THAT THE PAD BE SOLDERED

TO GROUND PLANE.

AD7873

TOP VIEW

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

X+

Y+

X–

V

BAT

GND

Y–

+V

CC

CS

DIN

BUSY

+V

CC

AUX V

REF

PENIRQ

DOUT

DCLK

AD7873

TOP VIEW

(Not to Scale)

02164-004