AD7873 Data Sheet

Rev. F | Page 4 of 28

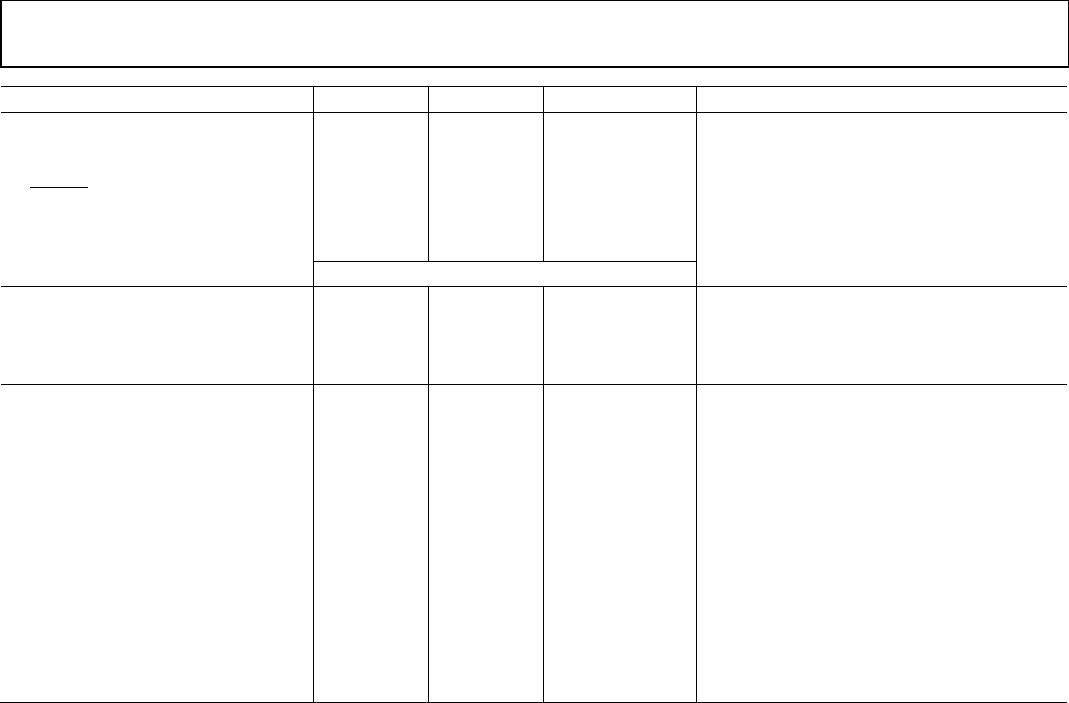

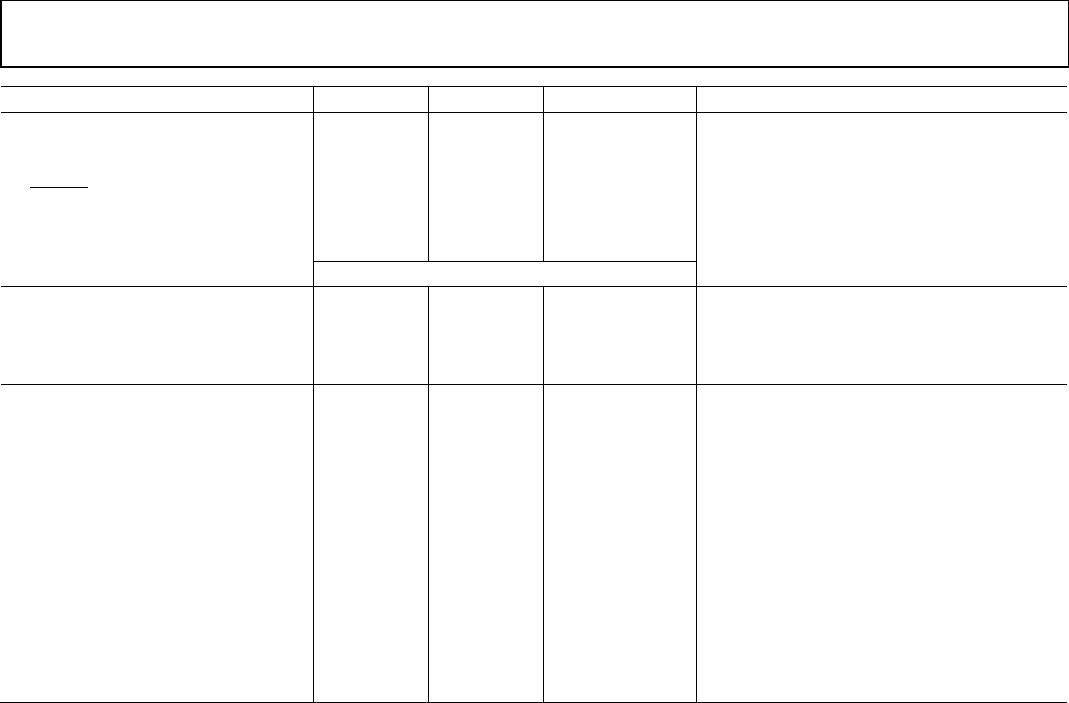

Parameter AD7873A

1

AD7873B

1

Unit Test Conditions/Comments

LOGIC OUTPUTS

Output High Voltage, V

OH

V

CC

– 0.2 V

CC

– 0.2 V min I

SOURCE

= 250 µA; V

CC

= 2.2 V to 5.25 V

Output Low Voltage, V

OL

0.4 0.4 V max I

SINK

= 250 µA

PENIRQ Output Low Voltage, V

OL

0.4 0.4 V max 100 kΩ pull-up; I

SINK

= 250 µA

Floating-State Leakage Current ±10 ±10 µA max

Floating-State Output Capacitance

5

10 10 pF max

Output Coding Straight (Natural) Binary

CONVERSION RATE

Conversion Time 12 12 DCLK cycles max

Track-and-Hold Acquisition Time 3 3 DCLK cycles min

POWER REQUIREMENTS

+V

CC

(Specified Performance) 2.7/3.6 2.7/3.6 V min/max Functional from 2.2 V to 5.25 V

CC

6

CC

Normal Mode (f

SAMPLE

= 125 kSPS) 380 380 µA max Internal reference off, V

CC

= 3.6 V, 240 µA typ

670 670 µA typ Internal reference on, V

CC

= 3.6 V

Normal Mode (f

SAMPLE

= 12.5 kSPS) 170 170 µA typ Internal reference off, V

CC

= 2.7 V, f

DCLK

= 200 kHz

Normal Mode (Static) 150 150 µA typ Internal reference off, V

CC

= 3.6 V

580 580 µA typ Internal reference on, V

CC

= 3.6 V

Shutdown Mode (Static) 1 1 µA max 200 nA typ

Power Dissipation

6

Normal Mode (f

SAMPLE

= 125 kSPS) 1.368 1.368 mW max Internal reference off, V

CC

= 3.6 V

2.412 2.412 mW typ Internal reference on, V

CC

= 3.6 V

Shutdown 3.6 3.6 µW max V

CC

= 3.6 V

1

Temperature range as follows: A, B Versions: –40°C to +85°C.

2

See the Terminology section.

3

Difference between TEMP0 and TEMP1 measurement. No calibration necessary.

4

Temperature drift is –2.1 mV/°C.

5

Sample tested @ 25°C to ensure compliance.

6

See the Power vs. Throughput Rate section.