AD7873 Data Sheet

Rev. F | Page 22 of 28

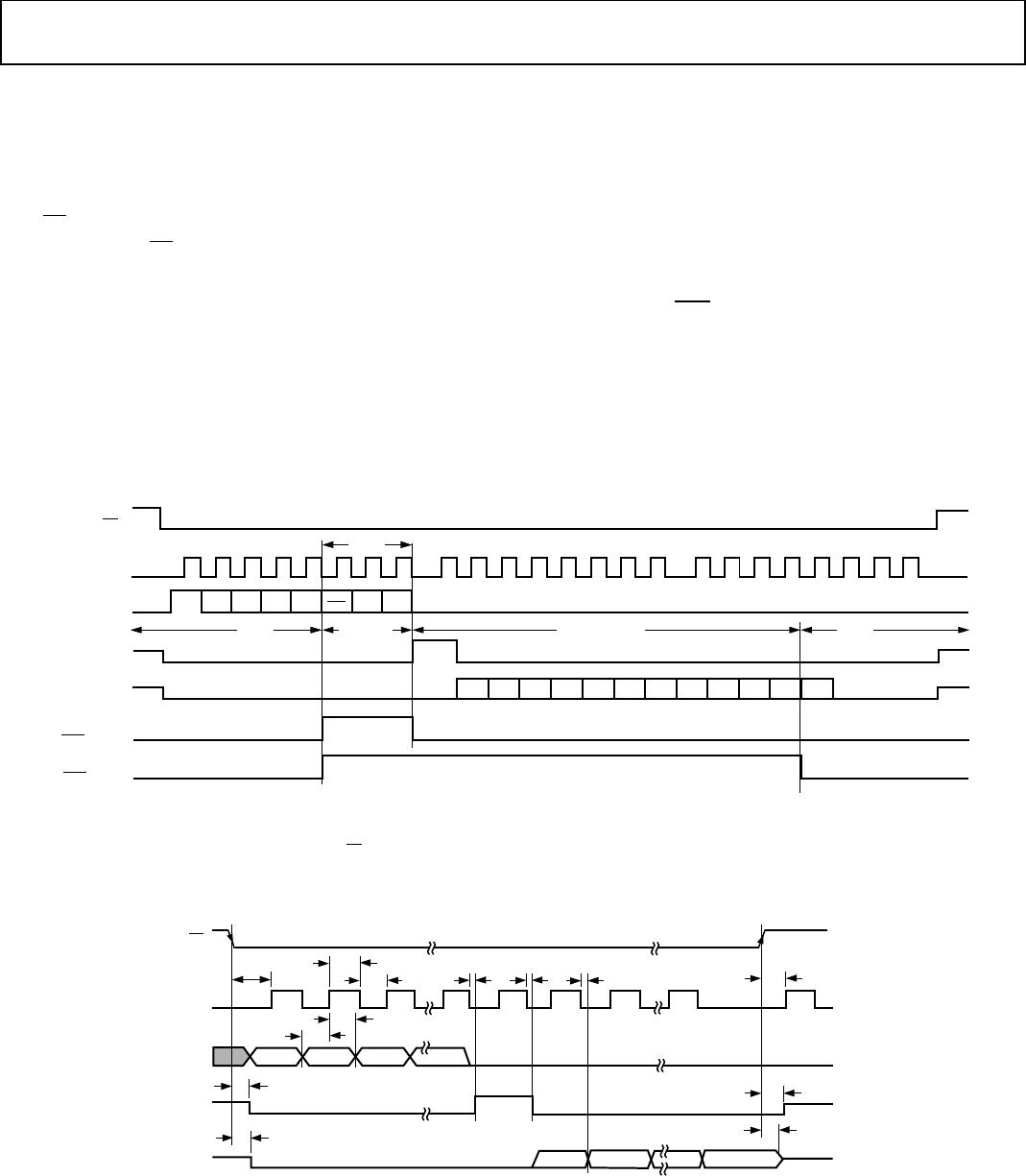

16 Clocks per Cycle

The control bits for the next conversion can be overlapped with

the current conversion to allow for a conversion every 16 DCLK

cycles, as shown in Figure 38. This timing diagram also allows

the possibility of communication with other serial peripherals

between each byte (eight DCLKs) transfer between the

processor and the converter. However, the conversion must

complete within a short enough time frame to avoid capacitive

droop effects that could distort the conversion result. It should

also be noted that the AD7873 is fully powered while other

serial communications are taking place between byte transfers.

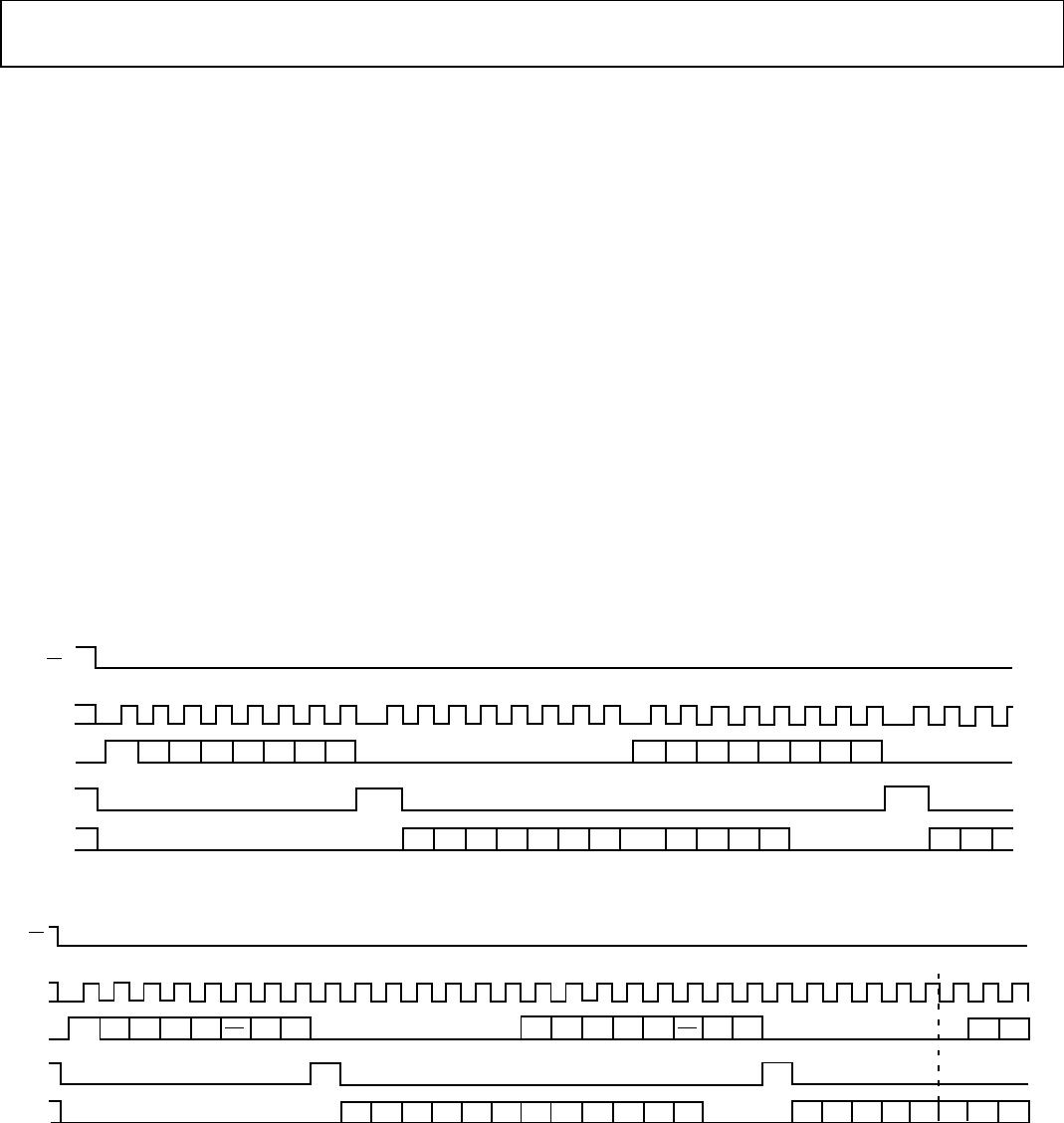

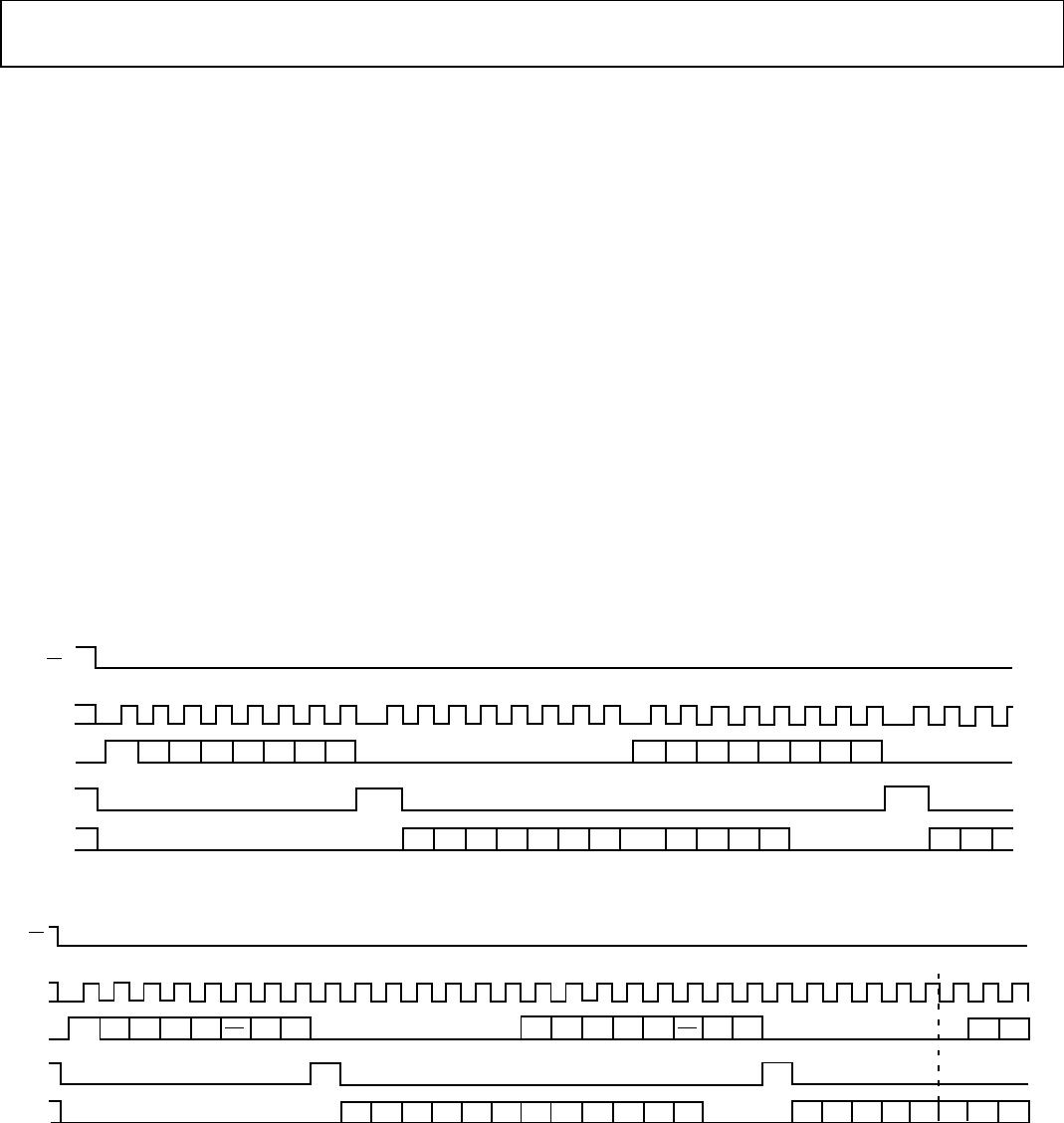

15 Clocks per Cycle

Figure 39 shows the fastest way to clock the AD7873. This

scheme does not work with most microcontrollers or DSPs

because they are not capable of generating a 15 clock cycle per

serial transfer. However, some DSPs allow the number of clocks

per cycle to be programmed. This method can also be used with

FPGAs (field programmable gate arrays) or ASICs (application

specific integrated circuits). As in the 16 clocks per cycle case,

the control bits for the next conversion are overlapped with the

current conversion to allow a conversion every 15 DCLK cycles

using 12 DCLKs to perform the conversion and 3 DCLKs to

acquire the analog input. This effectively increases the

throughput rate of the AD7873 beyond that used for the

specifications that are tested using 16 DCLKs per cycle, and

DCLK = 2 MHz.

8-Bit Conversion

The AD7873 can be set up to operate in an 8-bit mode rather

than a 12-bit mode by setting the MODE bit in the control

register to 1. This mode allows a faster throughput rate to be

achieved, assuming 8-bit resolution is sufficient. When using 8-bit

mode, a conversion is complete four clock cycles earlier than in

12-bit mode. This can be used with serial interfaces that provide

12 clock transfers, or two conversions can be completed with

three 8-clock transfers. The throughput rate increases by 25% as

a result of the shorter conversion cycle, but the conversion itself

can occur at a faster clock rate because the internal settling time

of the AD7873 is not as critical, because settling to eight bits is

all that is required. The clock rate can be as much as 50% faster.

The faster clock rate and fewer clock cycles combine to provide

double the conversion rate.

Figure 38. Conversion Timing, 16 DCLKs per Cycle, 8-Bit Bus Interface. No DCLK delay required with dedicated serial port.

Figure 39. Conversion Timing, 15 DCLKs per Cycle, Maximum Throughput Rate

DCLK

DIN

BUSY

DOUT

CS

1

S S

11 10 9 8 7 6 5 4 3 2 1 0 11 10 9

1 1

1

8 8

8

CONTROL BITS CONTROL BITS

02164-038

CS

DCLK

DIN

BUSY

DOUT

S A2 PD1 PD0A1 A0

MODE

SER/

DFR

MODE

SER/

DFR

1

11 10 9 8 7 6 5 4 3 2 1 0 11 10 9 8 7 6 5 4

15 1 15

1

S A2 S A2A1 PD1 PD0A0

02164-039