ICS813252CKI-02 REVISION A AUGUST 4, 2016 7 ©2016 Integrated Device Technology, Inc.

ICS813252I-02 Data Sheet VCXO JITTER ATTENUATOR & FEMTOCLOCK

®

MULTIPLIER

TABLE 4C. DIFFERENTIAL DC CHARACTERISTICS, V

CC

= V

CCO

= V

CCX

= 3.3V±5%, V

EE

= 0V, TA = -40°C TO 85°C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

V

OH

Output High Voltage; NOTE 1 V

CCO

- 1.4 V

CCO

- 0.9 V

V

OL

Output Low Voltage; NOTE 1 V

CCO

- 2.0 V

CCO

- 1.7 V

V

SWING

Peak-to-Peak Output Voltage Swing 0.6 1.0 V

NOTE 1: Outputs terminated with 50Ω to V

CCO

- 2V.

TABLE 4D. LVPECL DC CHARACTERISTICS, V

CC

= V

CCO

= V

CCX

= 3.3V±5%, V

EE

= 0V, TA = -40°C TO 85°C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

I

IH

Input High Current

CLK0/nCLK0,

CLK1/nCLK1

V

IN

= V

CC

= 3.465V 150 µA

I

IL

Input Low Current

CLK0, CLK1 V

IN

= 0V, V

CC

= 3.465V -5 µA

nCLK0, nCLK1 V

IN

= 0V, V

CC

= 3.465V -150 µA

V

PP

Peak-to-Peak Input Voltage; NOTE 1 0.15 1.3

V

V

CMR

Common Mode Input Voltage; NOTE 1, 2 V

EE

+ 0.5 V

CC

- 0.85

V

NOTE 1: V

IL

should not be less than -0.3V.

NOTE 2: Common mode voltage is defi ned as V

IH

.

TABLE 5. AC CHARACTERISTICS, V

CC

= V

CCO

= V

CCX

= 3.3V±5%, V

EE

= 0V, TA = -40°C TO 85°C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

f

IN

Input Frequency 0.008 155.52 MHz

f

OUT

Output Frequency 25 312.5 MHz

t

jit(Ø)

RMS Phase Jitter (Random);

NOTE 1

125MHz f

OUT

, 25MHz crystal Inte-

gration Range:

10kHz – 20MHz

1.3 ps

t

jit(acc)

Accumulated Jitter, RMS;

NOTE 2

125MHz

fOUT

, 25MHz crystal, 20K

Cycles

10 ps

t

jit(pk-pk) Peak-to-Peak Jitter 100K Random Cycles 35 ps

t

sk(o) Output Skew; NOTE 2, 3 75 ps

odc Output Duty Cycle 45 55 %

t

R

/ t

F

Output Rise/Fall Time 20% to 80% 200 700 ps

t

LOCK

PLL Lock Time 175 ms

NOTE: Characterized with outputs at the same frequency using the loop fi lter components for the mid loop bandwidth.

NOTE: Electrical parameters are guaranteed over the specifi ed ambient operating temperature range, which is established

when the device is mounted in a test socket with maintained transverse airfl ow greater than 500 lfpm. The device will meet

specifi cations after thermal equilibrium has been reached under these conditions.

Refer to VCXO-PLL Loop Bandwidth Selection Table.

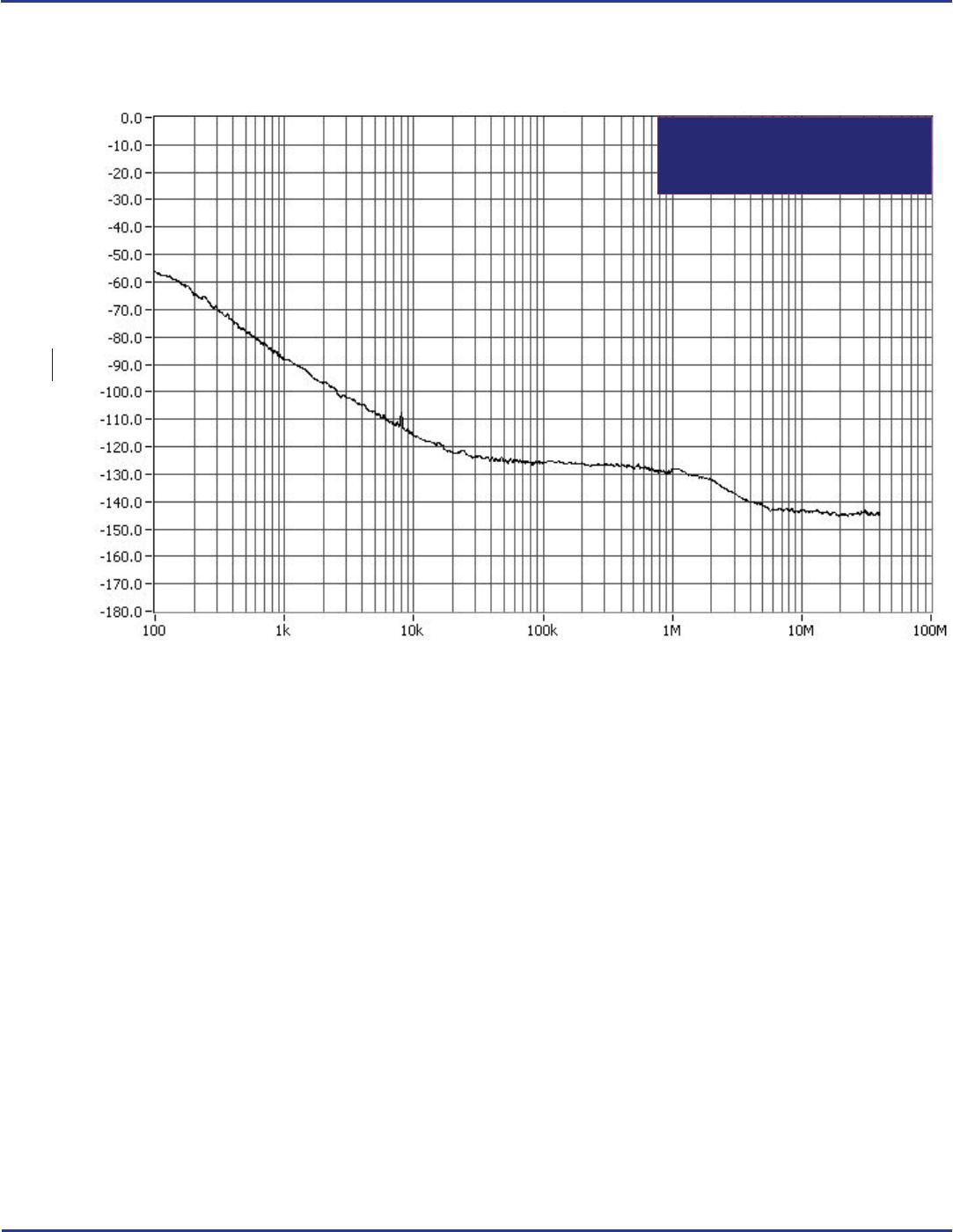

NOTE 1: Please refer to the Phase Noise Plot.

NOTE 2: This parameter is defi ned in accordance with JEDEC Standard 65.

NOTE 3: Defi ned as skew between outputs at the same supply voltage and with equal load condtions.

Measured at the output differential cross points.