LTC3612

19

3612fc

For more information www.linear.com/LTC3612

AVP Mode

Fast load transient response, limited board space and low

cost are typical requirements of microprocessor power

supplies. A microprocessor has typical full load step with

very fast slew rate. The voltage at the microprocessor must

be held to about ±0.1V of nominal in spite of these load

current steps. Since the control loop cannot respond this

fast, the output capacitors must supply the load current

until the control loop can respond.

Normally, several capacitors in parallel are required to

meet microprocessor transient requirements. Capacitor

ESR and ESL primarily determine the amount of droop or

overshoot in the output voltage.

Consider the LTC3612 without AVP with a bank of tantalum

output capacitors. If a load step with very fast slew rate

occurs, the voltage excursion will be seen in both direc

-

tions, for full load to minimum load transient and for the

minimum load to full load transient.

If the ITH pin is tied to SV

IN

, the active voltage position-

ing (AVP) mode and internal compensation are selected.

AVP mode intentionally compromises load regulation by

reducing the gain of the feedback cir

cuit, resulting in an

output voltage that varies with load current. When the load

current suddenly increases, the output voltage starts from

a level slightly higher than nominal so the output voltage

can droop more and stay within the specified voltage

range. When the load current suddenly decreases the

output voltage starts at a level lower than nominal so the

output voltage can have more overshoot and stay within

the specified voltage range (see Figures 3 and 4).

applicaTions inForMaTion

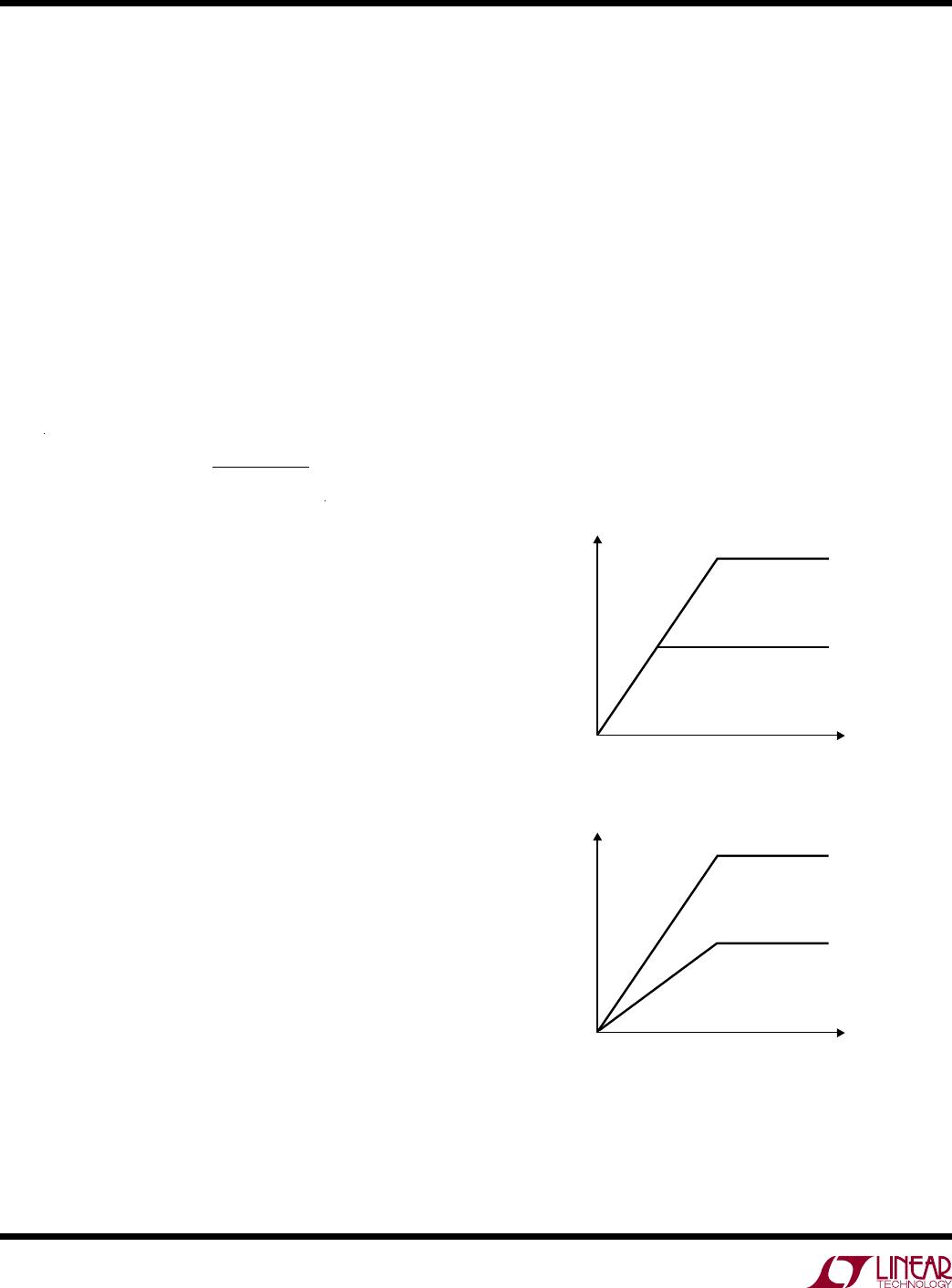

Figure 4. Load Step Transient Forced Continuous Mode

with AVP Mode

The benefit is a lower peak-to-peak output voltage deviation

for a given load step without having to increase the output

filter capacitance. Alternatively, the output voltage filter

capacitance can be reduced while maintaining the same

peak to peak transient response. Due to the reduced loop

gain in AVP mode, no external compensation is required.

DDR Mode

The LTC3612 can both source and sink current if the MODE

pin is configured to forced continuous mode.

Current sinking is typically limited to 1.5A, for 1MHz

frequency and a 1µH inductor, but can be lower at higher

frequencies and low output voltages. If higher ripple current

can be tolerated, smaller inductor values can increase the

sink current limit. See the Typical Performance Charac

-

teristics curves for more information.

In addition, tying the DDR pin to SV

IN

, lower external

reference voltage and tracking output voltage between

channels are possible. See the Output Voltage Tracking

and External Reference Input sections.

Soft-Start

The RUN pin provides a means to shut down the LTC3612.

Tying the RUN pin to SGND places the LTC3612 in a low

quiescent current shutdown state (I

Q

< 1µA).

The LTC3612 is enabled by pulling the RUN pin high. How-

ever, the applied voltage must not exceed SV

IN

. In some

applications, the RUN signal is generated within another

power domain and is driven high while the SV

IN

and PV

IN

is still 0V. In this case, it’s required to limit the current into

Figure 3. Load Step Transient Forced Continuous Mode

(AVP Inactive)

V

OUT

200mV/DIV

I

L

1A/DIV

50µs/DIV

3612 F03

V

IN

= 3.3V

V

OUT

= 1.8V

I

LOAD

= 100mA TO 3A

V

MODE

= 1.5V

COMPENSATION FIGURE 1

OUT

100mV/DIV

I

L

1A/DIV

50µs/DIV

3612 F04

V

IN

= 3.3V

V

OUT

= 1.8V

I

LOAD

= 100mA TO 3A

V

MODE

= 1.5V

V

ITH

= 3.3V

OUTPUT CAPACITOR VALUE FIGURE 1