values shown. The package design targets are provided for reference, system signal sim-

ulations should not use these values but use the Micron package model.

3. It is assumed that Lpkg can be approximated as Lpkg = Z

O

× Td.

4. It is assumed that Cpkg can be approximated as Cpkg = Td/Z

O

.

5. Package-only impedance (Zpkg) is calculated based on the Lpkg and Cpkg total for a

given pin where: Zpkg (total per pin) = SQRT (Lpkg/Cpkg).

6. Z

IO

and Td

IO

apply to DQ, DM, DQS_c, DQS_t, TDQS_t, and TDQS_c.

7. Package-only delay (Tpkg) is calculated based on Lpkg and Cpkg total for a given pin

where: Tdpkg (total per pin) = SQRT (Lpkg × Cpkg).

8. Absolute value of ZIO (DQS_t), ZIO (DQS_c) for impedance (Z) or absolute value of TdIO

(DQS_t), TdIO (DQS_c) for delay (Td).

9. Z

I CTRL

and Td

I CTRL

apply to ODT, CS_n, and CKE.

10. Z

I ADD CMD

and Td

I ADD CMD

apply to A[17:0], BA[1:0], BG[1:0], RAS_n CAS_n, and WE_n.

11. Absolute value of ZCK_t, ZCK_c for impedance (Z) or absolute value of TdCK_t, TdCK_c

for delay (Td).

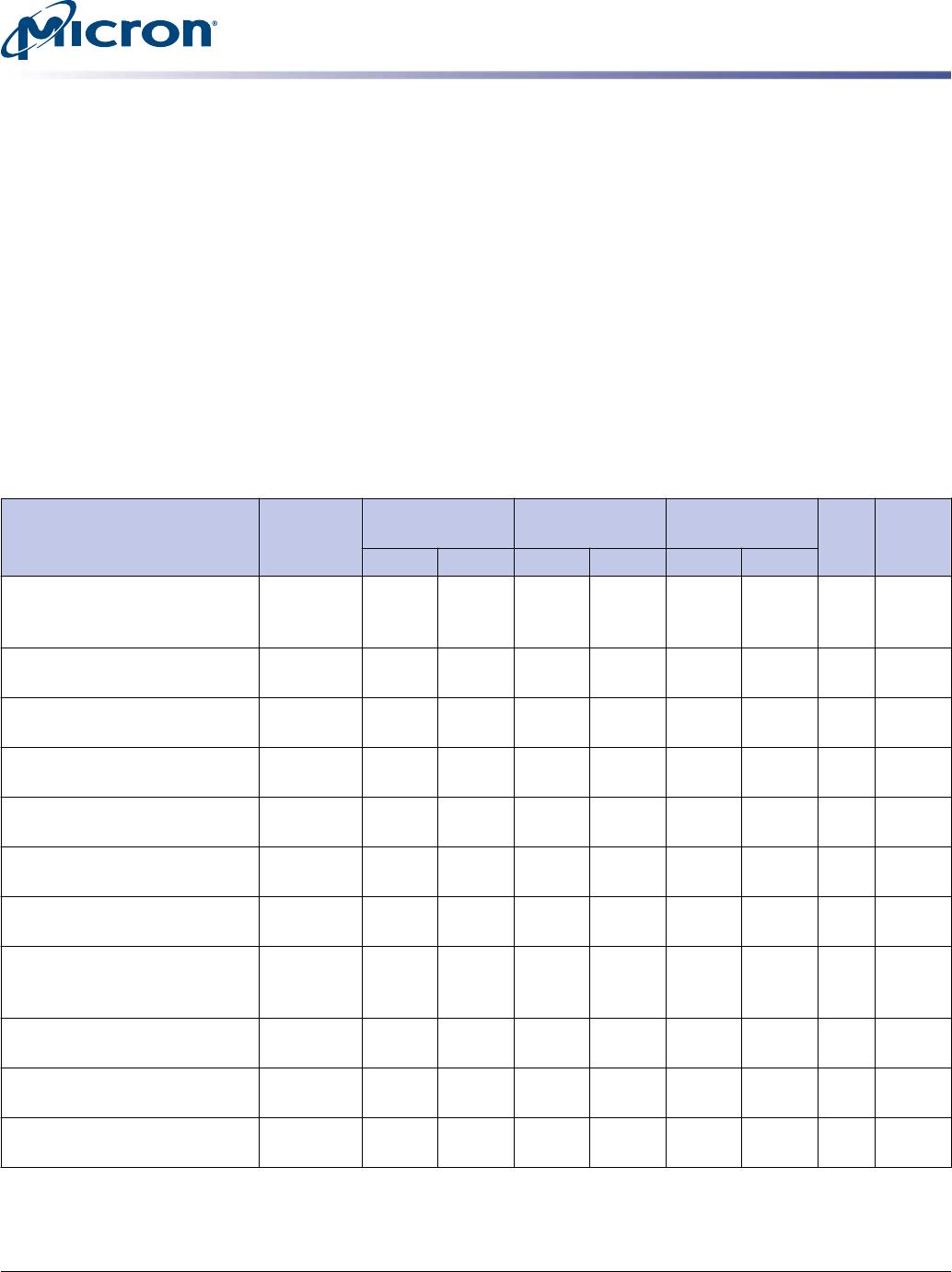

Table 7: Pad Input/Output Capacitance

Parameter Symbol

DDR4-1600,

-1866, -2133

DDR4-2400,

-2666 DDR4-2933

Unit NotesMin Max Min Max Min Max

Input/output capacitance: DQ,

DM, DQS_t, DQS_c, TDQS_t,

TDQS_c

C

IO

1.8 2.8 1.8 2.8 1.8 2.8 pF 1, 2, 3

Input capacitance: CK_t and

CK_c

C

CK

2.1 2.9 2.1 2.9 2.1 2.9 pF 1, 2, 3, 4

Input capacitance delta: CK_t

and CK_c

C

DCK

0 0.05 0 0.05 0 0.05 pF 1, 2, 3, 5

Input/output capacitance delta:

DQS_t and DQS_c

C

DDQS

0 0.05 0 0.05 0 0.05 pF 1, 3

Input capacitance: CTRL, ADD,

CMD input-only pins

C

I

1.6 2.6 1.6 2.6 1.6 2.6 pF 1, 3, 6

Input capacitance delta: All

CTRL input-only pins

C

DI_CTRL

–0 .9 0.9 –0 .9 0.9 –0 .9 0.9 pF 1, 3, 7

Input capacitance delta: All

ADD/CMD input-only pins

C

DI_ADD_CMD

–0 .9 0.9 –0 .9 0.9 –0 .9 0.9 pF 1, 3, 8, 9

Input/output capacitance delta:

DQ, DM, DQS_t, DQS_c, TDQS_t,

TDQS_c

C

DIO

–0.16 0.16 –0.16 0.16 –0.16 0.16 pF 1, 2, 10,

11

Input/output capacitance:

ALERT pin

C

ALERT

1.1 2.3 1.1 2.3 1.1 2.3 pF 1, 3

Input/output capacitance: ZQ

pin

C

ZQ

– 3.7 – 3.7 – 3.7 pF 1, 3, 12

Input/output capacitance: TEN

pin

C

TEN

0.2 2.3 0.2 2.3 0.2 2.3 pF 1, 3, 13

Notes:

1. Although the DM, TDQS_t, and TDQS_c pins have different functions, the loading

matches DQ and DQS.

16Gb: x16 TwinDie Single Rank DDR4 SDRAM

DRAM Package Electrical Specifications

CCMTD-1725822587-9947

16gb_x16_1cs_TwinDie.pdf - Rev. G 06/18 EN

11

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.