LT3582/LT3582-5/LT3582-12

14

3582512fb

OTP2/REG2: Data in address 02h confi gures the output

voltage sequencing, sets a fi ne voltage adjust for V

OUTP

,

and determines if further OTP programming is permitted or

not. Proper uses of the bits in address 02h are discussed

in the following sections.

Setting the Output Voltages (V

P

, V

PLUS

and V

N

Bits)

The LT3582 series contains two resistor dividers which are

programmable in the LT3582, to set the output voltages.

The positive output voltage V

OUTP

is adjustable in 25mV

steps by setting the V

P

bits in REG0/OTP0 in addition to

the V

PLUS

bit in REG2/OTP2.

V

OUTP

= 3.2V + (V

P

• 50mV) + (V

PLUS

• 25mV)

where:

V

P

= an integer value from 0 to 191

V

PLUS

= 0 or 1

The V

OUTN

voltage is adjustable in –50mV steps by setting

the V

N

bits in REG1/OTP1.

V

OUTN

= –1.2V – (V

N

• 50mV)

where:

V

N

= an integer value from 0 to 255

Dynamically Changing the Output Voltage (LT3582 Only):

After output regulation has been reached, it’s possible to

change the output voltages by writing new values to the

V

N

or V

P

bits. When reducing the magnitude of an out-

put voltage, it will decay at a rate dependent on the load

current and capacitance. Confi guring a large increase in

magnitude of an output voltage can cause a large increase

in switch current to charge the output capacitor. Before

reconfi guring the outputs, consider forcing a soft-start

by asserting the SWOFF bit before writing the new V

P

or

V

N

codes. Subsequently clearing SWOFF initiates the new

soft-start sequence.

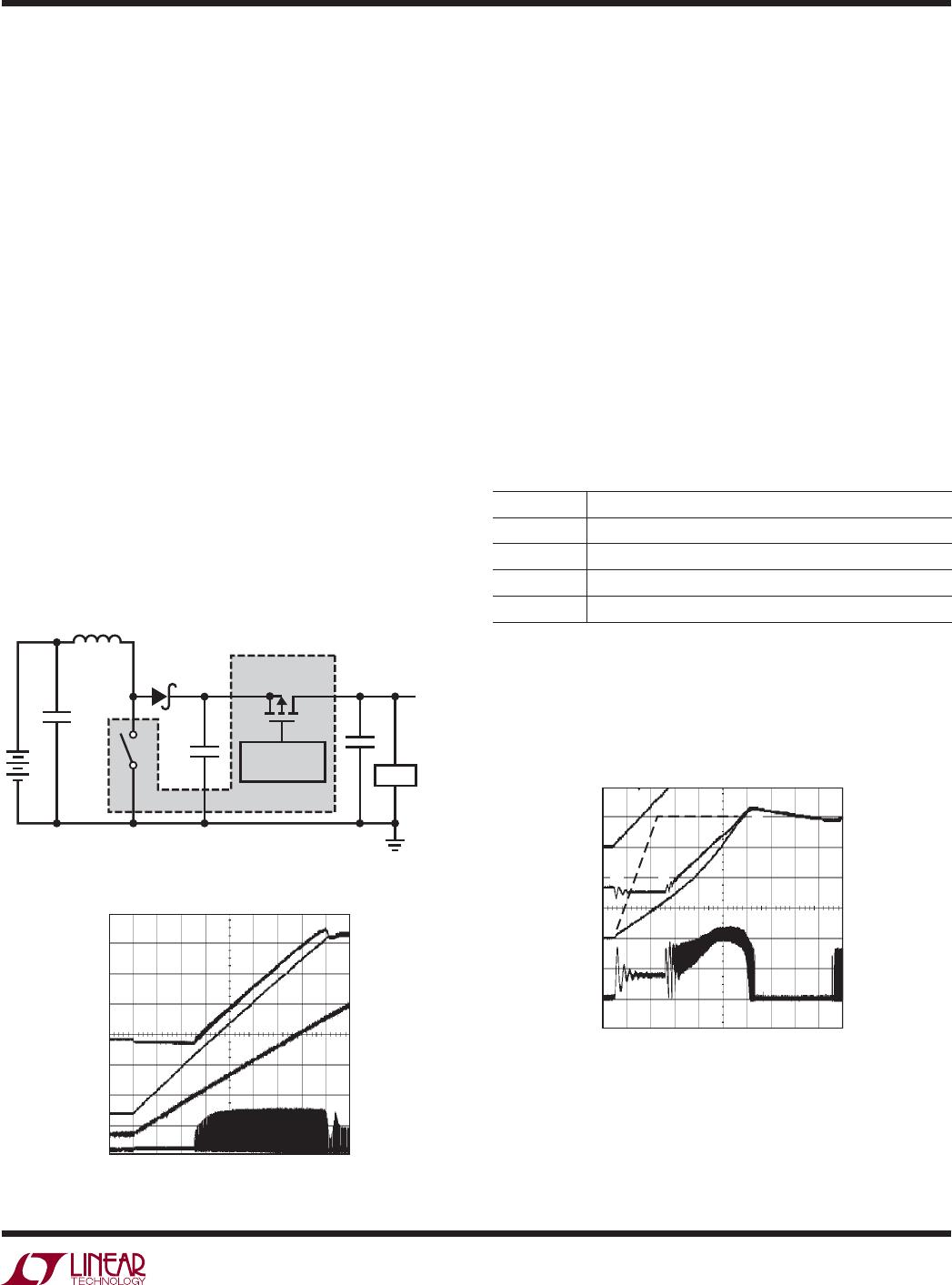

Soft-Start/Output Voltage Ramping (IRMP Bits)

The LT3582 series contains soft-start circuitry to control the

output voltage ramp rates, therefore limiting peak switch

currents during start-up. High switch currents are inherent

in switching regulators during start-up since the feedback

loop is saturated due to V

OUT

being far from its fi nal value.

The regulator tries to charge the output capacitor as quickly

as possible which results in large currents.

Capacitors must be connected from RAMPP and RAMPN

to ground for soft-start. During shutdown or when the

SWOFF bit is set, the RAMP capacitors are discharged

to ground. After SHDN rises or SWOFF is cleared, the

capacitors are charged by programmable (LT3582 only)

currents, thus creating linear voltage ramps. The V

OUT

voltages ramp in proportion to their respective RAMP

voltages according to:

V

OUT

_RAMP _RATE =

V

OUT

0.8V

⎛

⎝

⎜

⎞

⎠

⎟

•

I

RAMP

C

RAMP

⎛

⎝

⎜

⎞

⎠

⎟

Volts / Sec

Proportionality Constant

RAMP pin ramp rate (V/Sec)

where:

I

RAMP

= RAMP pin charging current set by IRMP

bits (1A, 2A, 4A or 8A for LT3582,

1µA for LT3582-5/LT3582-12)

C

RAMP

= External RAMP pin capacitor (Farads)

V

OUT

= Output voltage during regulation

For example, selecting I

RAMP

= 1A, C

RAMP

= 10nF and

V

OUTP

= 12V results in a power-up ramp rate of 1.5Volt/ms

(see Figure 6).

Ramp rates less than 1-10V/ms generally result in good

start-up characteristics. The outputs should linearly follow

the RAMPx voltages with no distortions. Figure 7 shows

an excessive start-up ramp rate of ~120V/ms in which

APPLICATIONS INFORMATION