LT3582/LT3582-5/LT3582-12

8

3582512fb

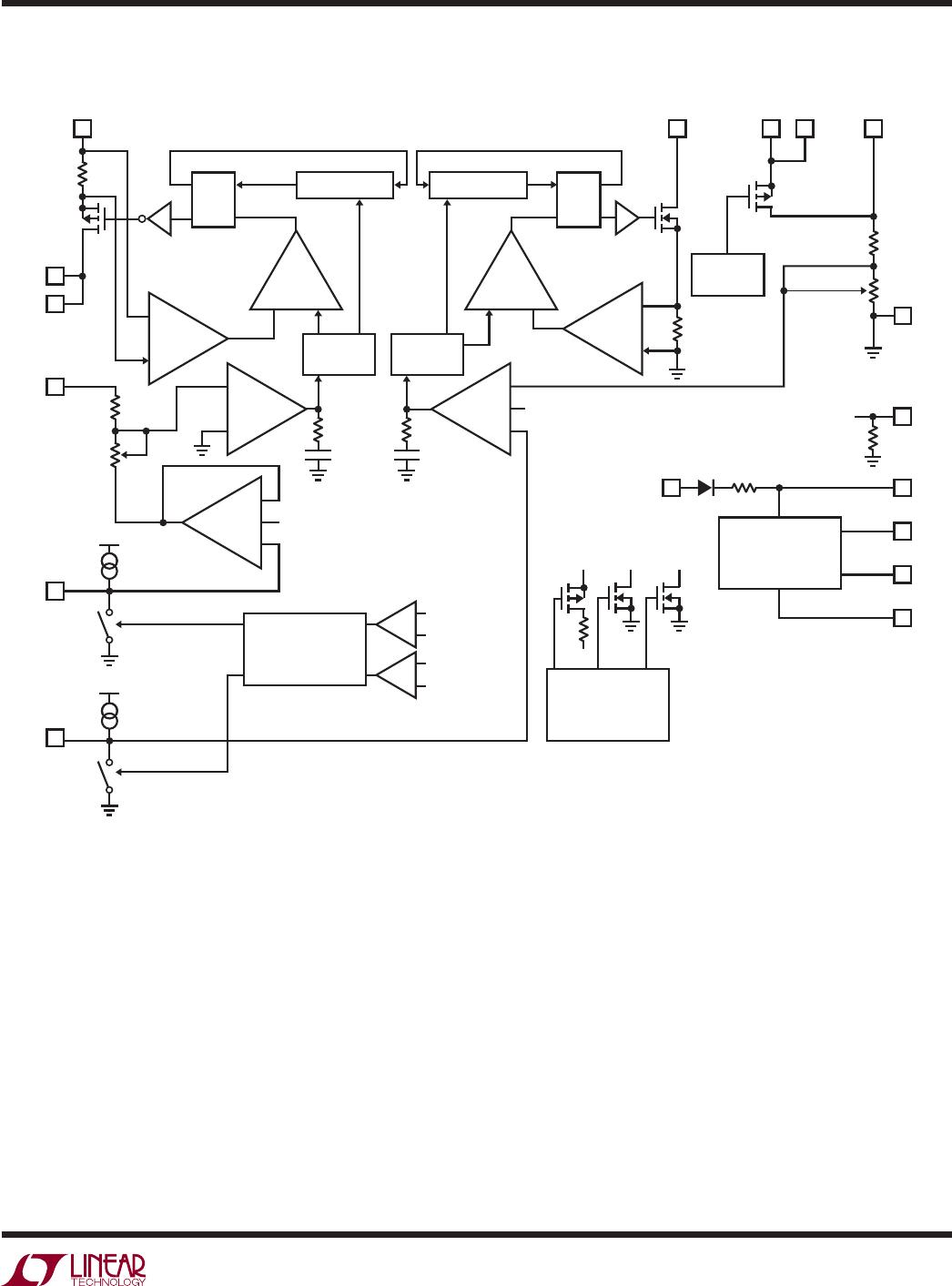

PIN FUNCTIONS

CA (Pin 1): I

2

C Address Select Pin. Tie this pin to V

IN

to set

the 7-bit address to 0110 001. Tie to GND for 1000 101.

V

OUTN

(Pin 2): Negative Output Voltage Pin. When the con-

verter is operating, this pin is regulated to the programmed

negative output voltage. Place a ceramic capacitor from

this pin to GND.

SWN (Pins 3, 4): Negative Switching Node for the In-

verting Converter. This is the drain of the internal PMOS

power switch. Connect one end of the Inverting inductor

to these pins. Keep the trace area on these pins as small

as possible.

V

IN

(Pin 5): Input Supply Pin and Source of the PMOS

Power Switch. This pin must be bypassed locally with a

ceramic capacitor. The operating voltage range of this pin

is 2.55V to 5.5V.

RAMPN (Pin 6): Soft-Start Ramp Pin for the Inverting

Converter. Place a capacitor from this pin to GND. A

programmable current of 1A to 8A (LT3582) or 1µA

(LT3582-5/LT3582-12) charges this pin during start-up,

limiting the ramp rate of V

OUTN

. This pin is discharged to

GND during shutdown.

RAMPP (Pin 7): Soft-Start Ramp Pin for the Boost Convert-

er. Place a capacitor from this pin to GND. A programmable

current of 1A to 8A (LT3582) or 1µA (LT3582-5/LT3582-12)

charges this pin during start-up, limiting the ramp rate of

V

OUTP

. This pin is discharged to GND in shutdown.

SHDN (Pin 8): Shutdown Pin. Drive this pin to 1.1V or

higher to enable the part. Drive to 0.3V or lower to shut

down. Includes an integrated 222k pull-down resistor.

V

OUTP

(Pin 9): Output of the Boost Converter Output

Disconnect Circuit. A ceramic capacitor should be placed

from this node to GND. During shutdown, this pin is

disconnected from the Boost network which allows this

pin to discharge to GND, assuming a load is present to

discharge the capacitance.

CAPP (Pins 10, 11): Connect the Boost output capacitor

from these pins to GND. During shutdown, the voltage on

these pins will remain close to the input voltage due to

the path through the Boost inductor and Schottky. During

normal operation, CAPP will be boosted slightly higher

than the programmed output voltage.

SWP (Pin 12): Positive Switching Node for the Boost

Converter. This is the drain of the internal NMOS power

switch. Connect one end of the Boost inductor to this pin.

Keep the trace area on this pin as small as possible.

GND (Pin 13): Ground Pin. Tie to a local ground plane.

Proper PCB layout is required to achieve advertised per-

formance; see the Applications Information section for

more information.

V

PP

(Pin 14): Programming Voltage Pin. Drive this pin

to 13-15V when programming the OTP memory. Float

otherwise. A bypass capacitor should be placed from this

node to GND if V

PP

is used for programming. If V

PP

falls

below 13V during OTP programming, an internal FAULT

bit, which can be read through the I

2

C interface, can be

set high.

SDA (Pin 15): I

2

C Bidirectional Data Pin. Tie to GND or

V

IN

if unused.

SCL (Pin 16): I

2

C Clock Pin. Tie to GND or V

IN

if un-

used.

Exposed Pad (Pin 17): Ground Pin. Tie to a local ground

plane. Proper PCB layout is required to achieve advertised

performance; see the Applications Information section for

more information.