©2012 Silicon Storage Technology, Inc. DS25023B 06/13

13

1 Mbit / 2 Mbit / 4 Mbit Multi-Purpose Flash

SST39LF010 / SST39LF020 / SST39LF040

SST39VF010 / SST39VF020 / SST39VF040

Data Sheet

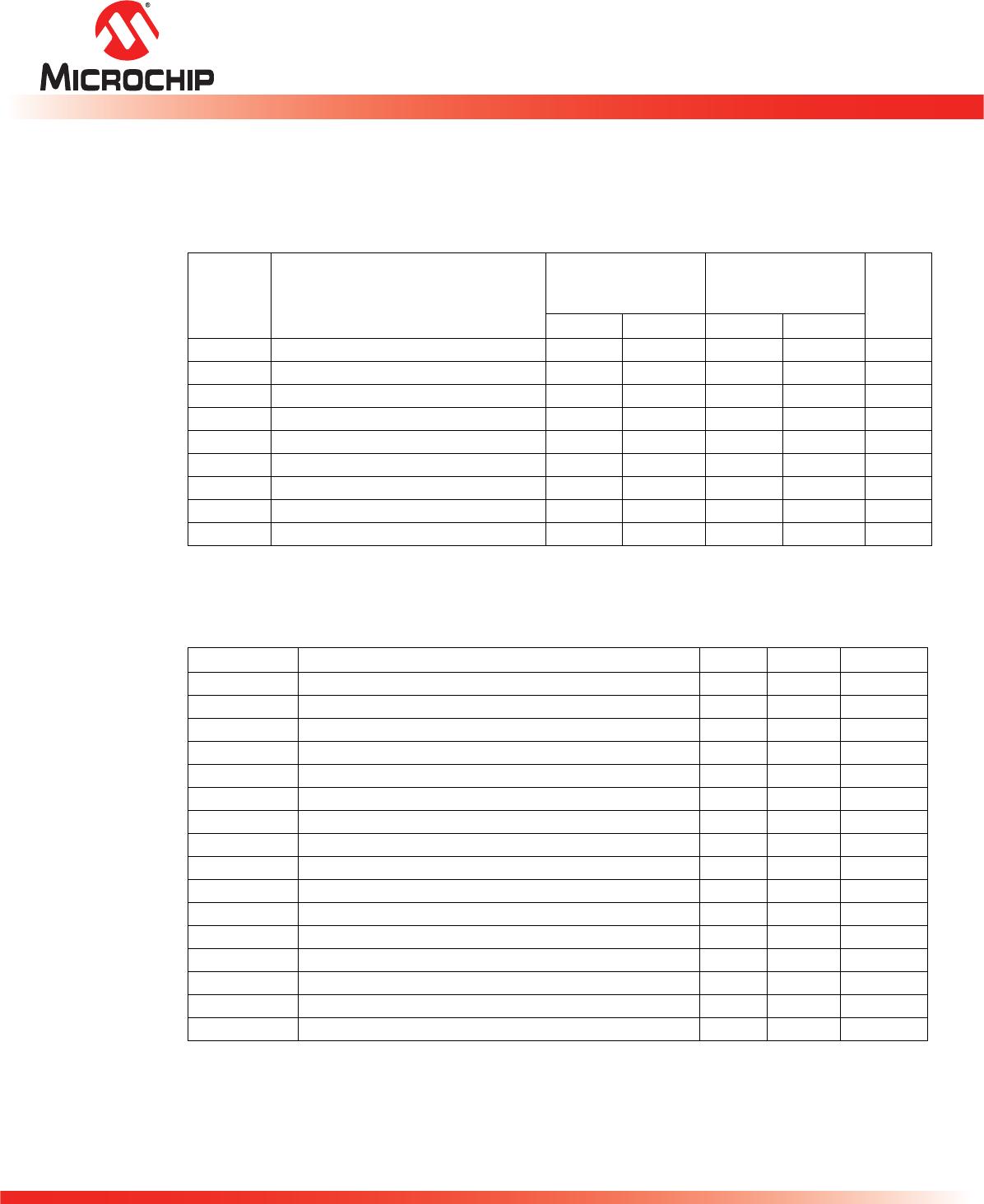

AC Characteristics

Table 12: Read Cycle Timing Parameters - V

DD

= 3.0-3.6V for SST39LF010/020/040 and

2.7-3.6V for SST39VF010/020/040

Symbol Parameter

SST39LF010-55

SST39LF020-55

SST39LF040-55

SST39VF010-70

SST39VF020-70

SST39VF040-70

UnitsMin Max Min Max

T

RC

Read Cycle Time 55 70 ns

T

CE

Chip Enable Access Time 55 70 ns

T

AA

Address Access Time 55 70 ns

T

OE

Output Enable Access Time 30 35 ns

T

CLZ

1

1. This parameter is measured only for initial qualification and after a design or process change that could affect this

parameter.

CE# Low to Active Output 0 0 ns

T

OLZ

1

OE# Low to Active Output 0 0 ns

T

CHZ

1

CE# High to High-Z Output 15 25 ns

T

OHZ

1

OE# High to High-Z Output 15 25 ns

T

OH

1

Output Hold from Address Change

00ns

T12.2 25023

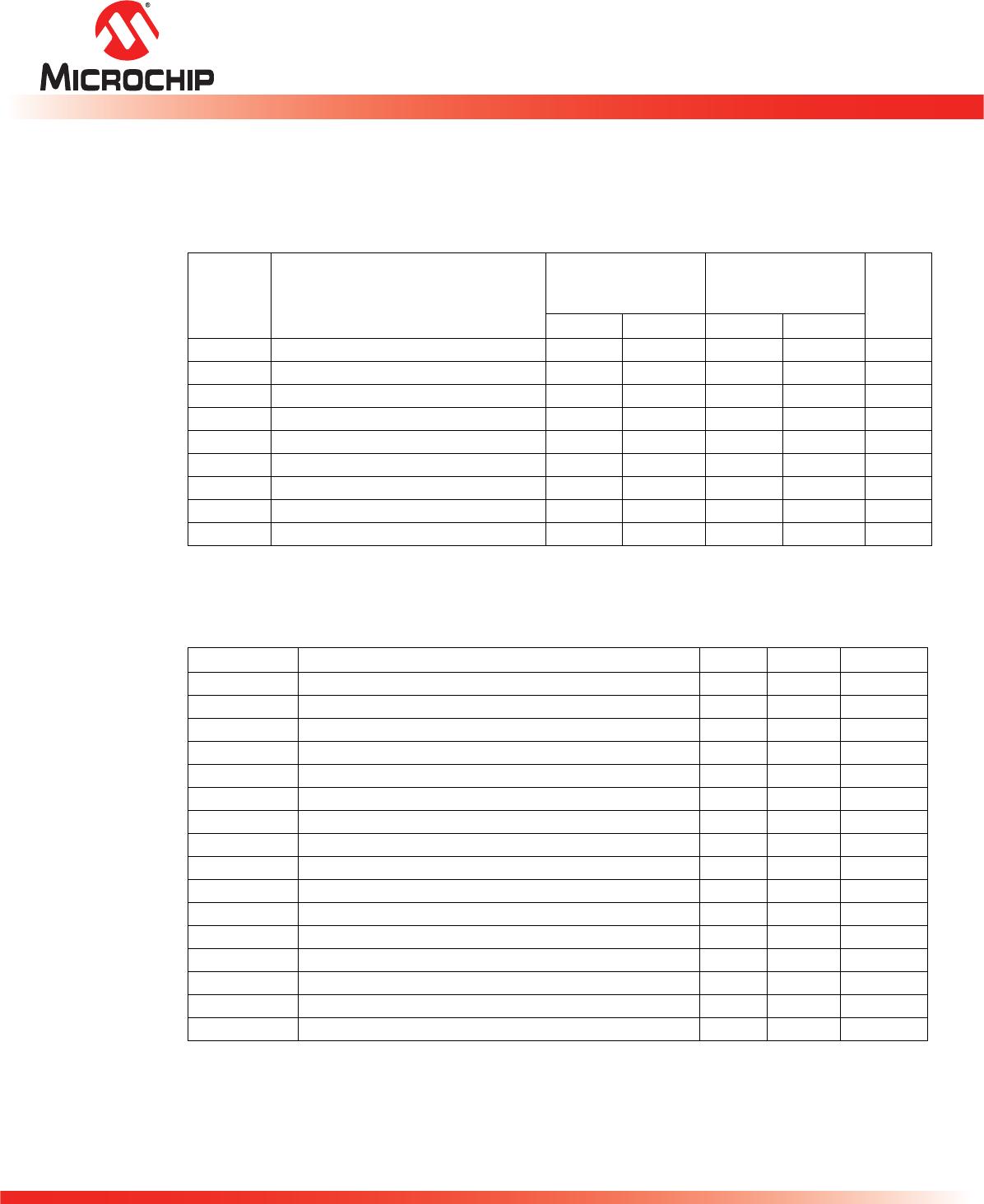

Table 13: Program/Erase Cycle Timing Parameters

Symbol Parameter Min Max Units

T

BP

Byte-Program Time 20 µs

T

AS

Address Setup Time 0 ns

T

AH

Address Hold Time 30 ns

T

CS

WE# and CE# Setup Time 0 ns

T

CH

WE# and CE# Hold Time 0 ns

T

OES

OE# High Setup Time 0 ns

T

OEH

OE# High Hold Time 10 ns

T

CP

CE# Pulse Width 40 ns

T

WP

WE# Pulse Width 40 ns

T

WPH

1

1. This parameter is measured only for initial qualification and after a design or process change that could affect this

parameter.

WE# Pulse Width High 30 ns

T

CPH

1

CE# Pulse Width High 30 ns

T

DS

Data Setup Time 40 ns

T

DH

1

Data Hold Time 0 ns

T

IDA

1

Software ID Access and Exit Time 150 ns

T

SE

Sector-Erase 25 ms

T

SCE

Chip-Erase 100 ms

T13.1 25023