AD7730/AD7730L

–13–

Communications Register (RS2–RS0 = 0, 0, 0)

The Communications Register is an 8-bit write-only register. All communications to the part must start with a write operation to the

Communications Register. The data written to the Communications Register determines whether the next operation is a read or

write operation, the type of read operation, and to which register this operation takes place. For single-shot read or write operations,

once the subsequent read or write operation to the selected register is complete, the interface returns to where it expects a write op-

eration to the Communications Register. This is the default state of the interface, and on power-up or after a RESET, the AD7730

is in this default state waiting for a write operation to the Communications Register. In situations where the interface sequence is

lost, a write operation of at least 32 serial clock cycles with DIN high, returns the AD7730 to this default state by resetting the

part. Table VI outlines the bit designations for the Communications Register. CR0 through CR7 indicate the bit location, CR denot-

ing the bits are in the Communications Register. CR7 denotes the first bit of the data stream.

Table VI. Communications Register

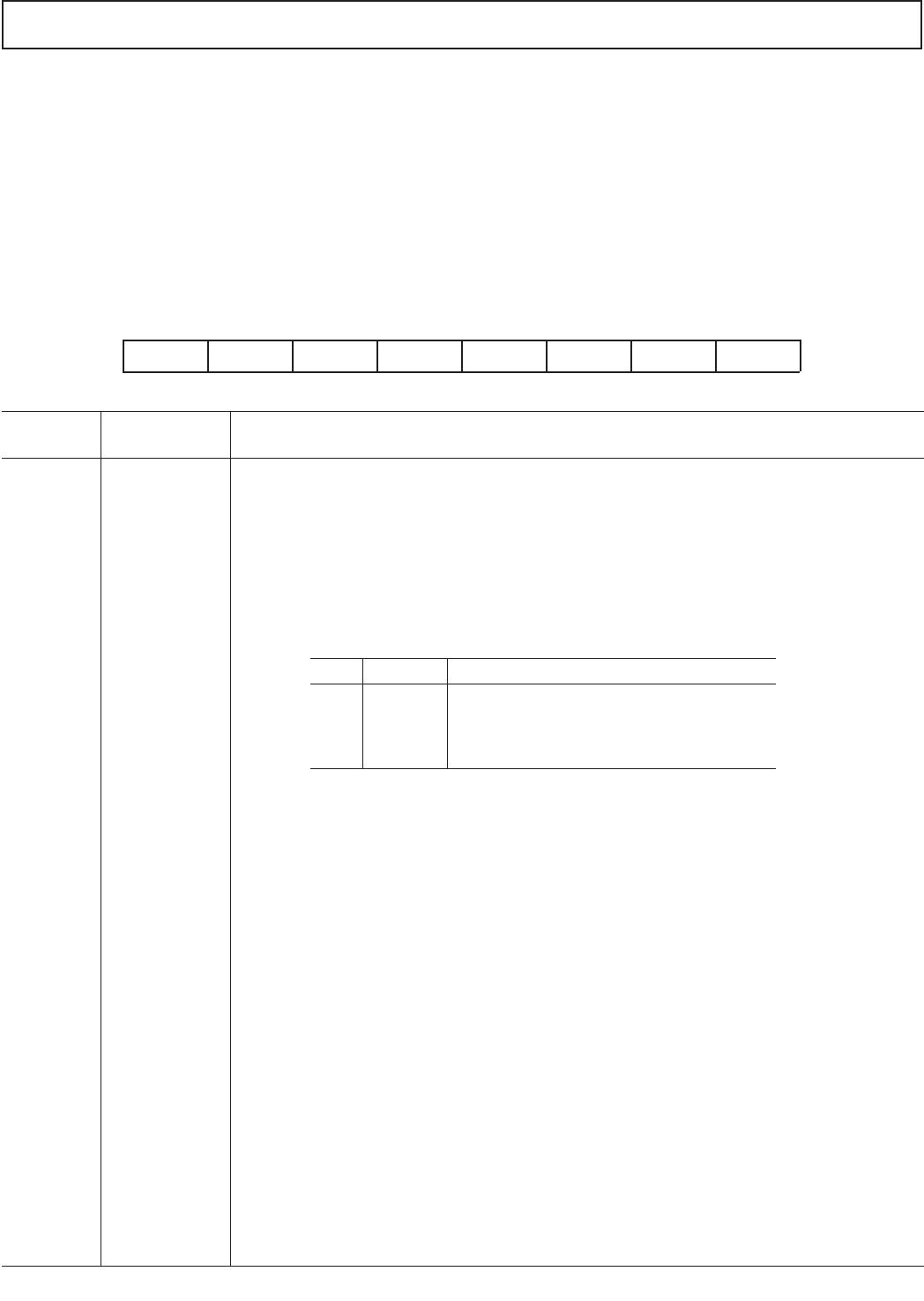

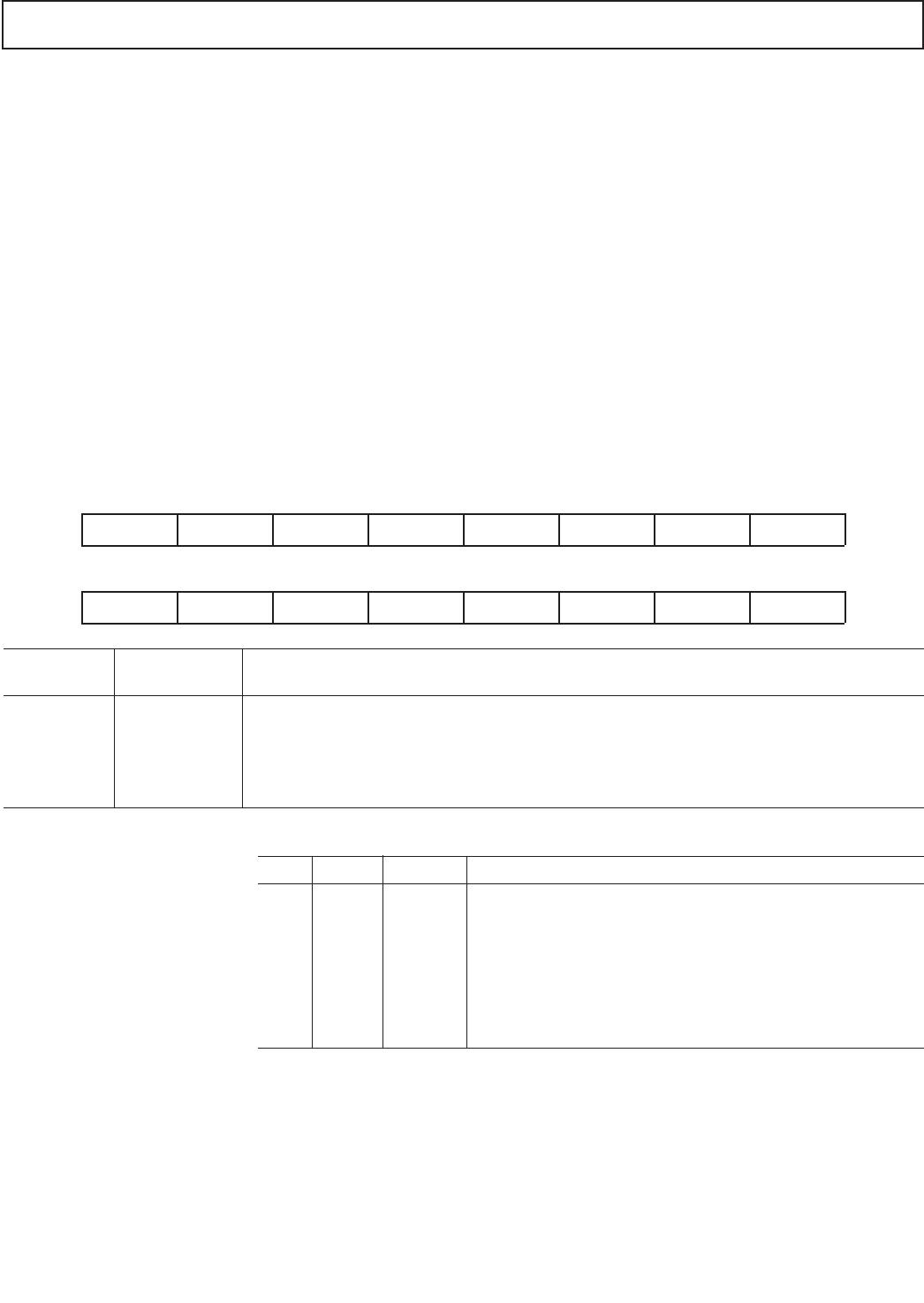

CR7 CR6 CR5 CR4 CR3 CR2 CR1 CR0

WEN ZERO RW1 RW0 ZERO RS2 RS1 RS0

Bit Bit

Location Mnemonic Description

CR7 WEN Write Enable Bit. A 0 must be written to this bit so the write operation to the Communications

Register actually takes place. If a 1 is written to this bit, the part will not clock on to subsequent

bits in the register. It will stay at this bit location until a 0 is written to this bit. Once a 0 is writ-

ten to the WEN bit, the next seven bits will be loaded to the Communications Register.

CR6 ZERO A zero must be written to this bit to ensure correct operation of the AD7730.

CR5, CR4 RW1, RW0 Read/Write Mode Bits. These two bits determine the nature of the subsequent read/write opera-

tion. Table VII outlines the four options.

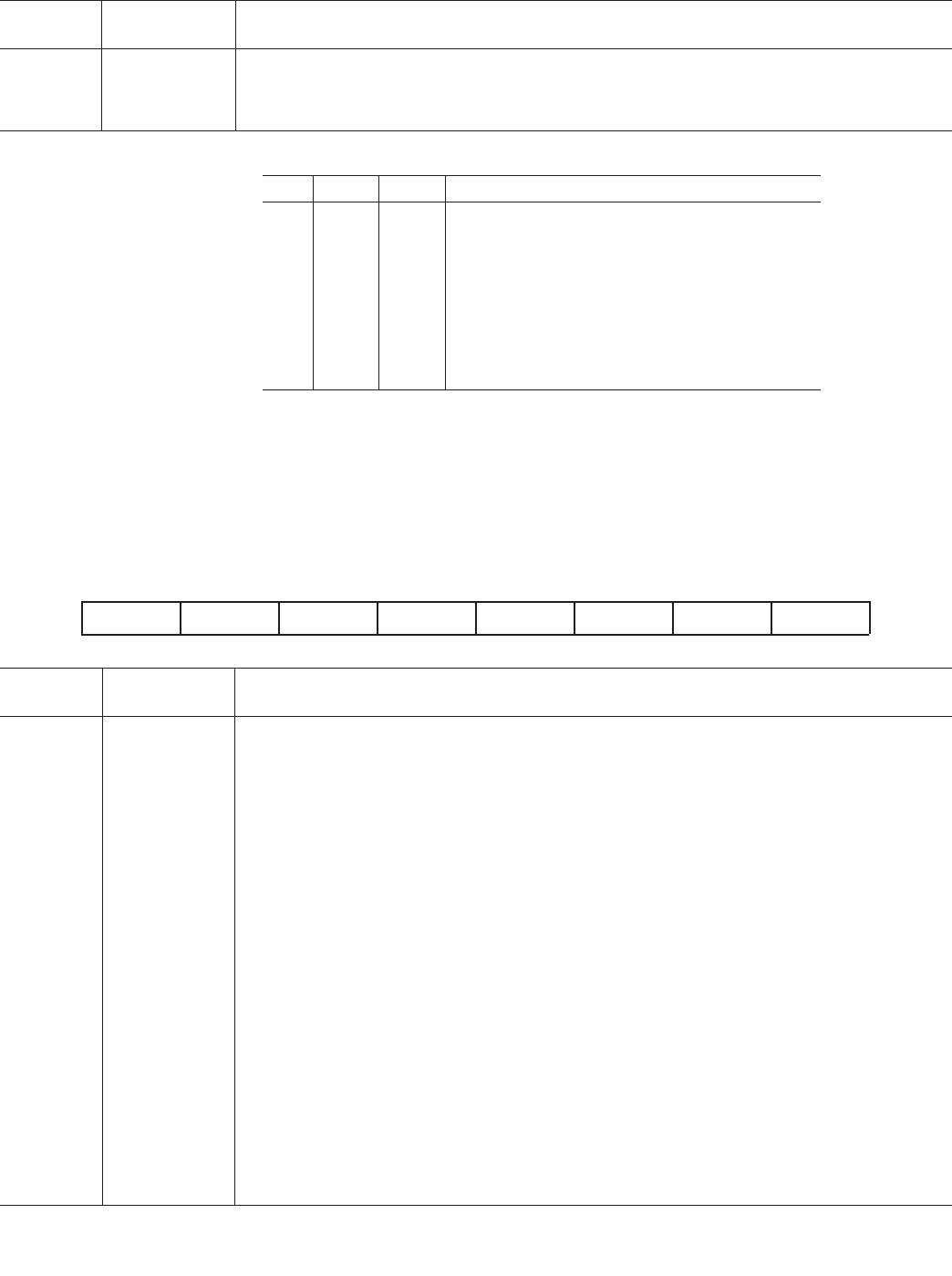

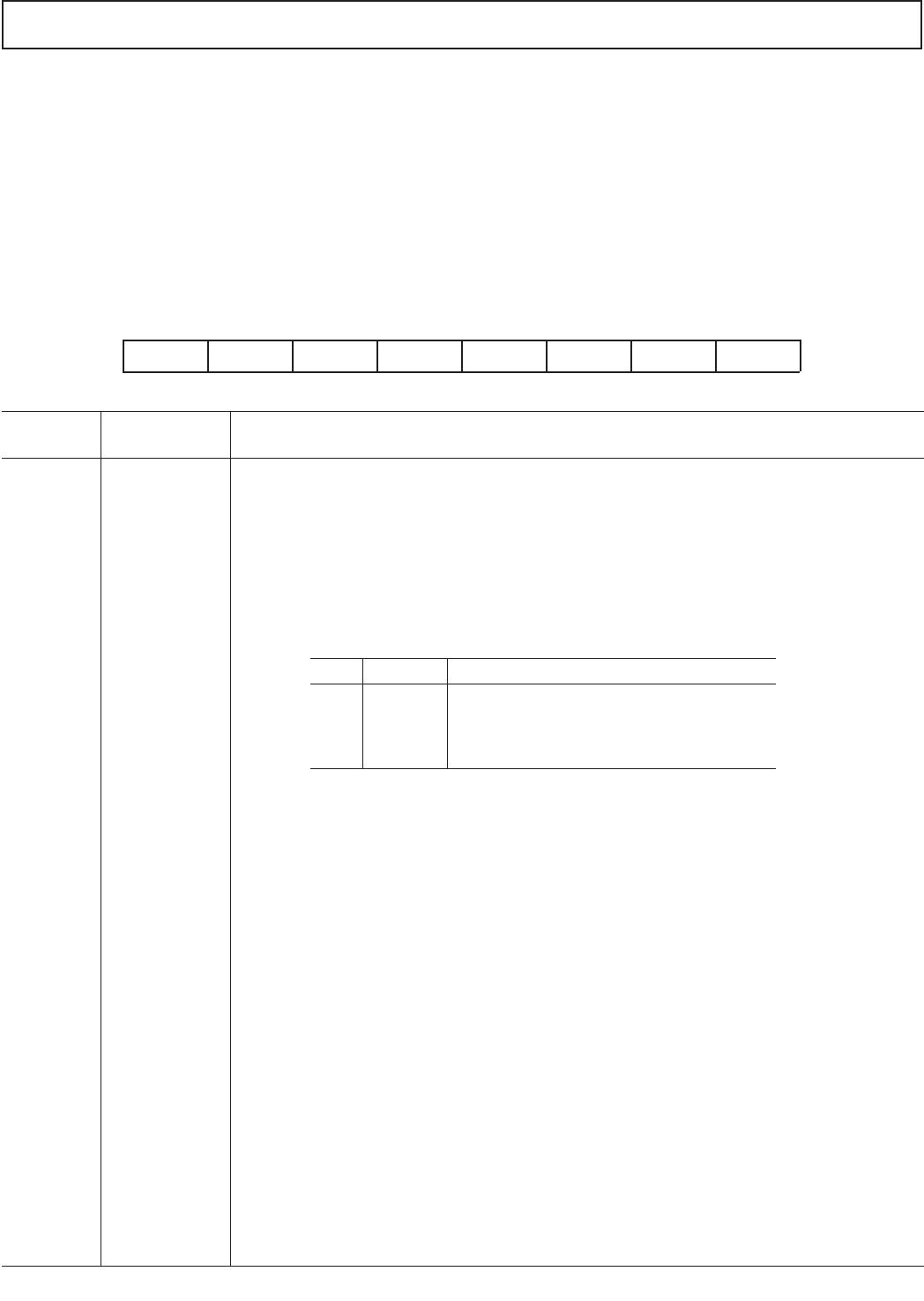

Table VII. Read/Write Mode

RW1 RW0 Read/Write Mode

0 0 Single Write to Specified Register

0 1 Single Read of Specified Register

1 0 Start Continuous Read of Specified Register

1 1 Stop Continuous Read Mode

With 0, 0 written to these two bits, the next operation is a write operation to the register specified by

bits RS2, RS1, RS0. Once the subsequent write operation to the specified register has been com-

pleted, the part returns to where it is expecting a write operation to the Communications Register.

With 0,1 written to these two bits, the next operation is a read operation of the register specified

by bits RS2, RS1, RS0. Once the subsequent read operation to the specified register has been

completed, the part returns to where it is expecting a write operation to the Communications

Register.

Writing 1,0 to these bits, sets the part into a mode of continuous reads from the register speci-

fied by bits RS2, RS1, RS0. The most likely registers with which the user will want to use this

function are the Data Register and the Status Register. Subsequent operations to the part will

consist of read operations to the specified register without any intermediate writes to the Com-

munications Register. This means that once the next read operation to the specified register has

taken place, the part will be in a mode where it is expecting another read from that specified

register. The part will remain in this continuous read mode until 30 Hex has been written to the

Communications Register.

When 1,1 is written to these bits (and 0 written to bits CR3 through CR0), the continuous read

mode is stopped and the part returns to where it is expecting a write operation to the Communi-

cations Register. Note, the part continues to look at the DIN line on each SCLK edge during

continuous read mode to determine when to stop the continuous read mode. Therefore, the user

must be careful not to inadvertently exit the continuous read mode or reset the AD7730 by

writing a series of 1s to the part. The easiest way to avoid this is to place a logic 0 on the DIN

line while the part is in continuous read mode. Once the part is in continuous read mode, the

user should ensure that an integer multiple of 8 serial clocks should have taken place before

attempting to take the part out of continuous read mode.

REV. B