AD7730/AD7730L

–25–

Burnout Currents

The AD7730 contains two 100 nA constant current generators,

one source current from AV

DD

to AIN(+) and one sink current

from AIN(–) to AGND. The currents are switched to the se-

lected analog input pair. Both currents are either on or off,

depending on the BO bit of the Mode Register. These currents

can be used in checking that a transducer is still operational

before attempting to take measurements on that channel. If the

currents are turned on, allowed flow in the transducer, a mea-

surement of the input voltage on the analog input taken and the

voltage measured is full scale, it indicates that the transducer

has gone open-circuit. If the voltage measured is 0 V, it indicates

that the transducer has gone short circuit. For normal operation,

these burnout currents are turned off by writing a 0 to the BO

bit. The current sources work over the normal absolute input

voltage range specifications.

REFERENCE INPUT

The AD7730’s reference inputs, REF IN(+) and REF IN(–),

provide a differential reference input capability. The common-

mode range for these differential inputs is from AGND to

AV

DD

. The nominal reference voltage, V

REF

(REF IN(+)—

REF IN(–)), for specified operation is +2.5 V with the HIREF

bit at 0 V and +5 V with the HIREF bit at 1. The part is also

functional with V

REF

of +2.5 V with the HIREF bit at 1. This

results in a halving of all input ranges. The resolution in nV will

be unaltered but will appear halved in terms of counts.

Both reference inputs provide a high impedance, dynamic load.

The typical average dc input leakage current over temperature

is 8.5 μA with HIREF = 1 and V

REF

= +5 V, and 2.5 μA with

HIREF = 0 and V

REF

= +2.5 V. Because the input impedance of

each reference input is dynamic, external resistance/capacitance

combinations on these inputs may result in gain errors on the

part.

The AD7730 can be operated in either ac or dc mode. If the

bridge excitation is fixed dc, the AD7730 should be operated in

dc mode. If the analog input and the reference inputs are externally

chopped before being applied to the part the AD7730 should be

operated in ac mode and not dc mode. In ac mode, it is assumed

that both the analog inputs and reference inputs are chopped

and as a result change phase every alternate chopping cycle. If

the chopping is synchronized by the AD7730 (using the ACX

signals to control the chopping) the part then takes into account

the reversal of the analog input and reference input signals.

The output noise performance outlined in Tables I through IV

is for an analog input of 0 V and is unaffected by noise on the

reference. To obtain the same noise performance as shown in

the noise tables over the full input range requires a low noise

reference source for the AD7730. If the reference noise in the

bandwidth of interest is excessive, it will degrade the performance

of the AD7730. In applications where the excitation voltage for

the bridge transducer on the analog input also drives the refer-

ence voltage for the part, the effect of the noise in the excita-

tion voltage will be removed as the application is ratiometric.

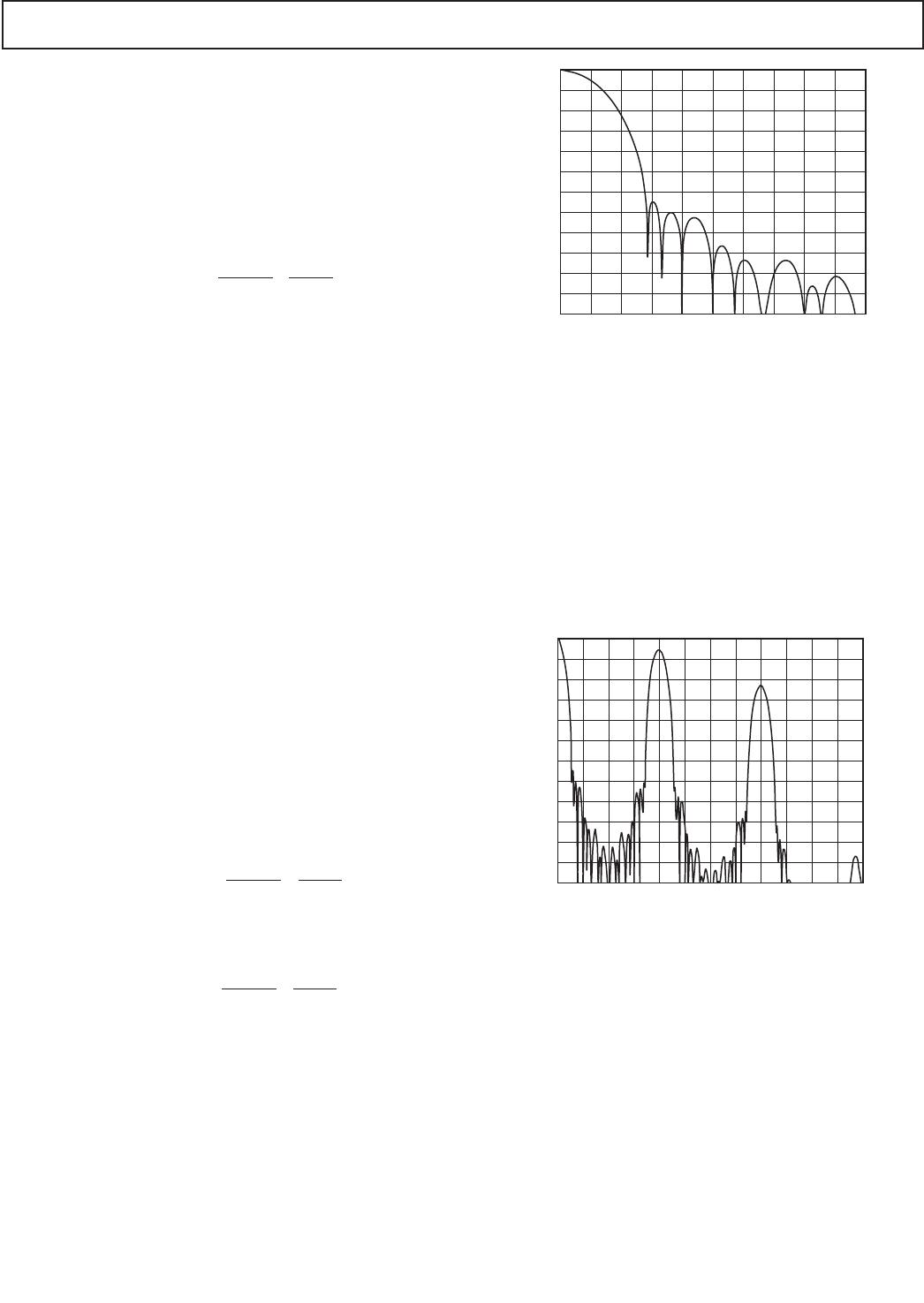

Figure 7 shows how the reference voltage can be connected in a

ratiometric fashion in a dc-excited bridge application. In this

case, the excitation voltage for the AD7730 and the transducer

is a dc voltage. The HIREF bit of the Mode Register should be

set to 1. Figure 8 meanwhile shows how the reference can be

connected in a ratiometric fashion in an ac-excited bridge

AV

DD

DV

DD

AGND DGND

AD7730

EXCITATION

VOLTAGE = +5V

IN+

OUT–

IN–

OUT+

REF IN(+)

REF IN(–)

AIN1(+)

AIN1(–)

Figure 7. Ratiometric Generation of Reference in DC-

Excited Bridge Application

AV

DD

DV

DD

EXCITATION

VOLTAGE = +5V

AGND DGND

IN+

OUT–

IN–

OUT+

AD7730

REF IN(+)

REF IN(–)

AIN1(+)

AIN1(–)

ACX

ACX

AC

EXCITATION

CLOCK

Figure 8. Ratiometric Generation of Reference in AC-

Excited Bridge Application

application. In this case, both the reference voltage for the part

and the excitation voltage for the transducer are chopped. Once

again, the HIREF bit should be set to 1.

If the AD7730 is not used in a ratiometric application, a low

noise reference should be used. Recommended 2.5 V reference

voltage sources for the AD7730 include the AD780, REF43

and REF192. If any of these references are used as the reference

source for the AD7730, the HIREF bit should be set to 0. It is

generally recommended to decouple the output of these references

to further reduce the noise level.

Reference Detect

The AD7730 includes on-chip circuitry to detect if the part

has a valid reference for conversions or calibrations. If the volt-

age between the REF IN(+) and REF IN(–) pins goes below

0.3 V or either the REF IN(+) or REF IN(–) inputs is open

circuit, the AD7730 detects that it no longer has a valid reference.

In this case, the NO REF bit of the Status Register is set to a 1.

If the AD7730 is performing normal conversions and the NO

REF bit becomes active, the part places all ones in the Data

Register. Therefore, it is not necessary to continuously monitor

the status of the NO REF bit when performing conversions. It is

only necessary to verify its status if the conversion result read

from the Data Register is all 1s.

REV. B