AD7730/AD7730L

–20–

DAC Register (RS2–RS0 = 1, 0, 0); Power On/Reset Status: 20 Hex

The DAC Register is an 8-bit register from which data can either be read or to which data can be written. This register provides

the code for the offset-compensation DAC on the part. Table XVI outlines the bit designations for the DAC Register. DR0

through DR7 indicate the bit location, DR denoting the bits are in the DAC Register. DR7 denotes the first bit of the data

stream. The number in brackets indicates the power-on/reset default status of that bit. Figure 5 shows a flowchart for reading

from the registers on the AD7730 and Figure 6 shows a flowchart for writing to the registers on the part.

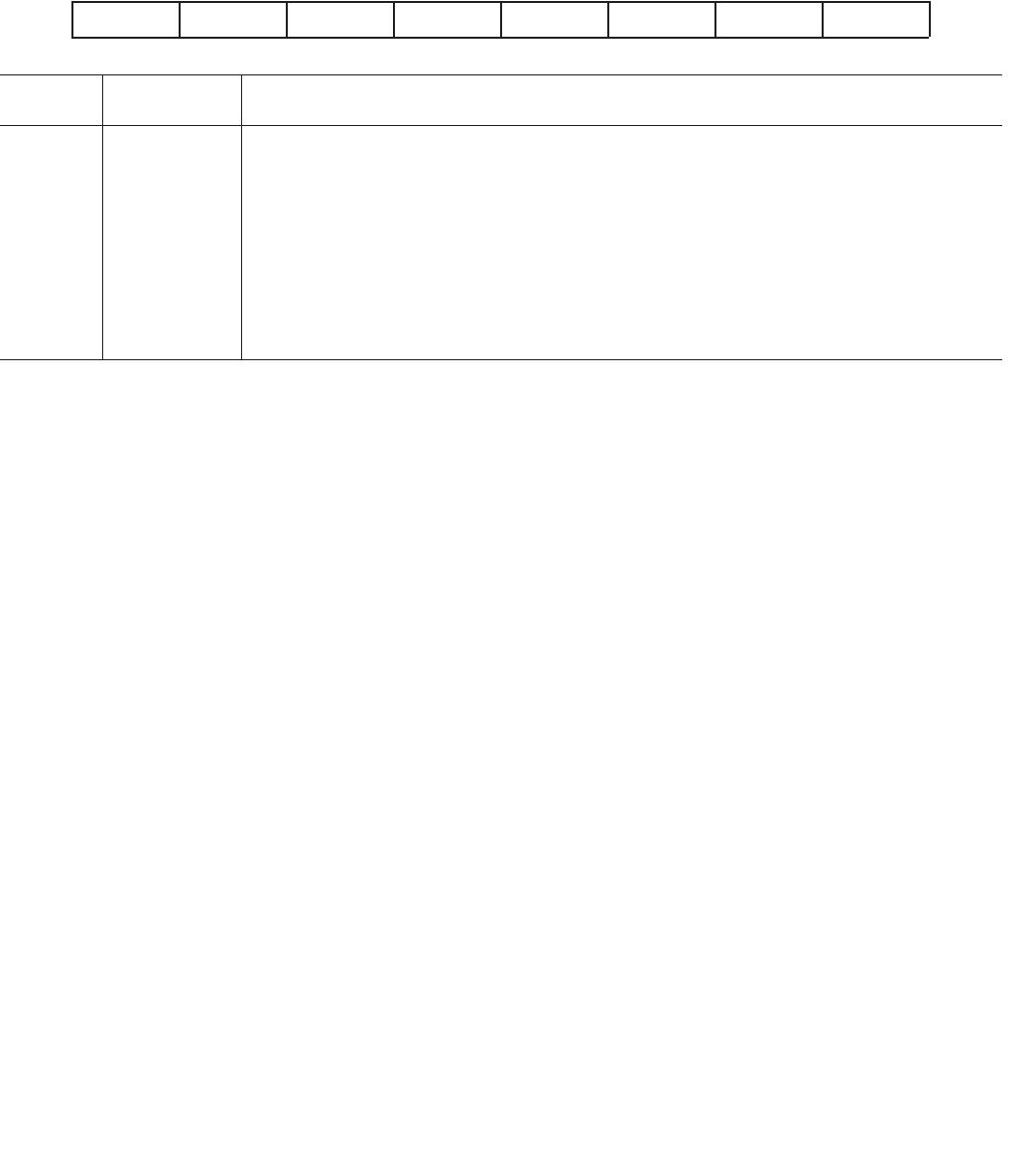

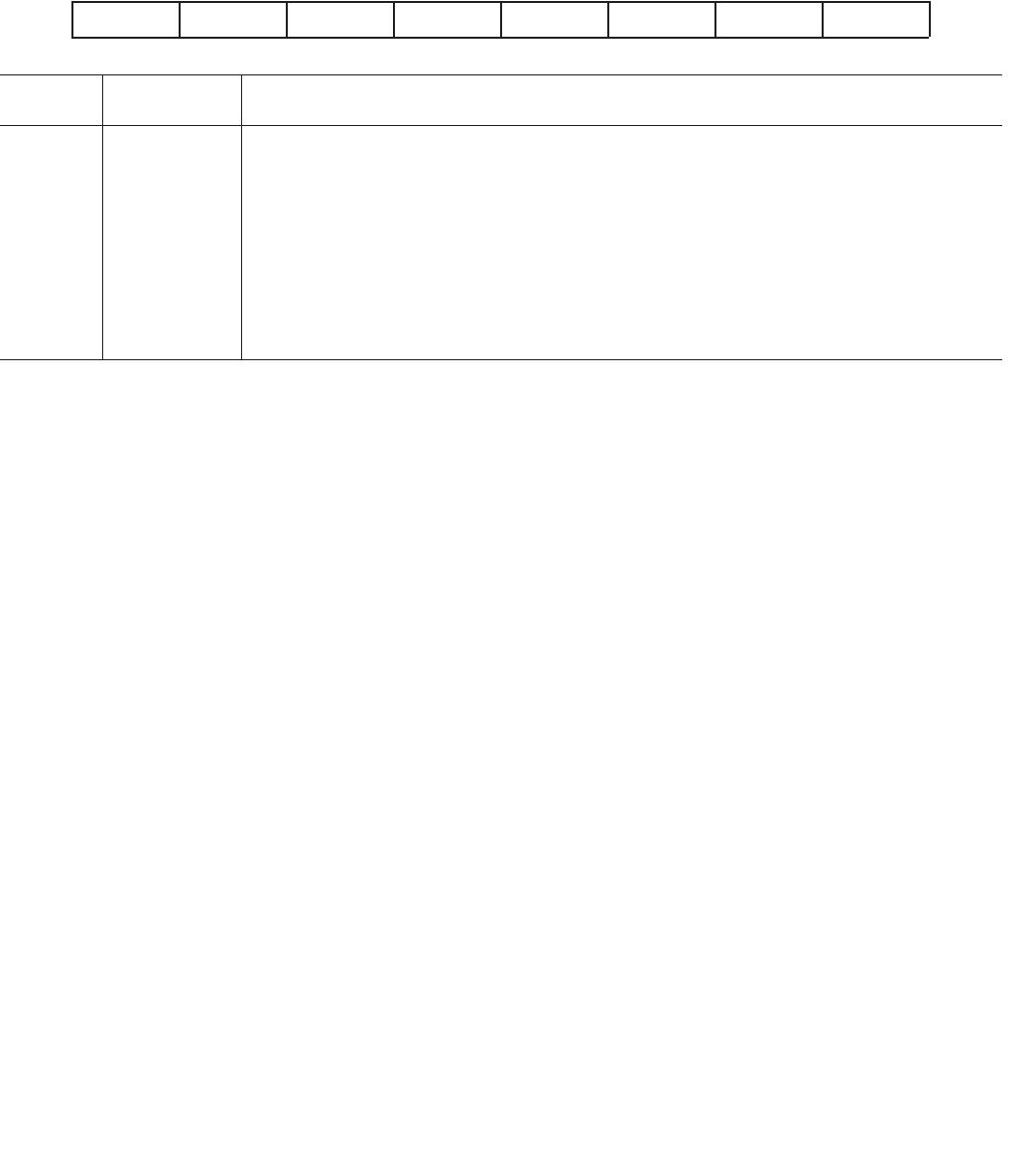

Table XVI. DAC Register

DR7 DR6 DR5 DR4 DR3 DR2 DR1 DR0

ZERO (0) ZERO (0) DAC5 (1) DAC4 (0) DAC3 (0) DAC2 (0) DAC1 (0) DAC0 (0)

Bit Bit

Location Mnemonic Description

DR7–DR6 ZERO A zero must be written to these bits to ensure correct operation of the AD7730.

DR5–DR0 DAC5–DAC0 DAC Selection Bits. These bits program the output of the offset DAC. The DAC is effectively

6 bits with one sign bit (DAC5) and five magnitude bits. With DAC5 at 1, the DAC output

subtracts from the analog input before it is applied to the PGA. With DAC5 at 0, the DAC

output adds to the analog input before it is applied to the PGA. The DAC output is given by

(V

REF

/62.5) × (D/32) = (V

REF

/2000) × D where D is the decimal equivalent of bits DAC4 to

DAC0. Thus, for a 5 V reference applied across the REF IN pins, the DAC resolution is 2.5 mV

and offsets in the range –77.5 mV to +77.5 mV can be removed from the analog input signal

before it is applied to the PGA. Note, that the HIREF bit has no effect on the DAC range or

resolution, it controls the ADC range only.

Offset Calibration Register (RS2–RS0 = 1, 0, 1); Power-On/Reset Status: 800000 Hex

The AD7730 contains three 24-bit Offset Calibration Registers, labelled Offset Calibration Register 0 to Offset Calibration Reg-

ister 2, to which data can be written and from which data can be read. The three registers are totally independent of each other.

The Offset Calibration Register is used in conjunction with the associated Gain Calibration Register to form a register pair. The

calibration register pair used to scale the output is as outlined in Table XIII. The Offset Calibration Register is updated after an

offset calibration routine (1, 0, 0 or 1, 1, 0 loaded to the MD2, MD1, MD0 bits of the Mode Register). During subsequent

conversions, the contents of this register are subtracted from the filter output prior to gain scaling being performed on the word.

Figure 5 shows a flowchart for reading from the registers on the AD7730 and Figure 6 shows a flowchart for writing to the regis-

ters on the part.

Gain Calibration Register (RS2–RS0 = 1, 1, 0); Power-On/Reset Status: 593CEA

The AD7730 contains three 24-bit Gain Calibration Registers, labelled Gain Calibration Register 0 to Gain Calibration Register

2, to which data can be written and from which data can be read. The three registers are totally independent of each other. The

Gain Calibration Register is used in conjunction with the associated Offset Calibration Register to form a register pair. The

calibration register pair used to scale the output is as outlined in Table XIII. The Gain Calibration Register is updated after a

gain calibration routine (1, 0, 1 or 1, 1, 1 loaded to the MD2, MD1, MD0 bits of the Mode Register). During subsequent con-

versions, the contents of this register are used to scale the number which has already been offset corrected with the Offset Cali-

bration Register contents. Figure 5 shows a flowchart for reading from the registers on the AD7730 and Figure 6 shows a

flowchart for writing to the registers on the part.

Test Register (RS2–RS0 = 1, 1, 1); Power-On/Reset Status: 000000Hex

The AD7730 contains a 24-bit Test Register to which data can be written and from which data can be read. The contents of this

Test Register are used in testing the device. The user is advised not to change the status of any of the bits in this register from the

default (Power-On or RESET) status of all 0s as the part will be placed in one of its test modes and will not operate correctly. If the

part enters one of its test modes, exercising RESET or writing 32 successive 1s to the part will exit the AD7730 from the mode and

return all register contents to their power-on/reset status. Note, if the part is placed in one of its test modes, it may not be possible to

read back the contents of the Test Register depending on the test mode in which the part has been placed.

REV. B