SC18IM700_3 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

Product data sheet Rev. 3 — 12 October 2017 10 of 24

NXP Semiconductors

SC18IM700

Master I

2

C-bus controller with UART interface

9.2 Register descriptions

9.2.1 Baud Rate Generator (BRG)

The baud rate generator is an 8-bit counter that generates the data rate for the transmitter

and the receiver. The rate is programmed through the BRG register and the baud rate can

be calculated as follows:

(1)

Remark: To calculate the baud rate the values in the BRG registers must first be

converted from hex to decimal.

Remark: For the new baud rate to take effect, both BRG0 and BRG1 must be written in

sequence (BRG0, BRG1) with new values. The new baud rate will be in effect once BRG1

is written.

9.2.2 Programmable port configuration (PortConf1 and PortConf2)

GPIO port 0 to port 7 may be configured by software to one of four types. These are:

quasi-bidirectional, push-pull, open-drain, and input-only. Two bits are used to select the

desired configuration for each port pin. PortConf1 is used to select the configuration for

GPIO3 to GPIO0, and PortConf2 is used to select the configuration for GPIO7 to GPIO4.

A port pin has Schmitt triggered input that also has a glitch suppression circuit.

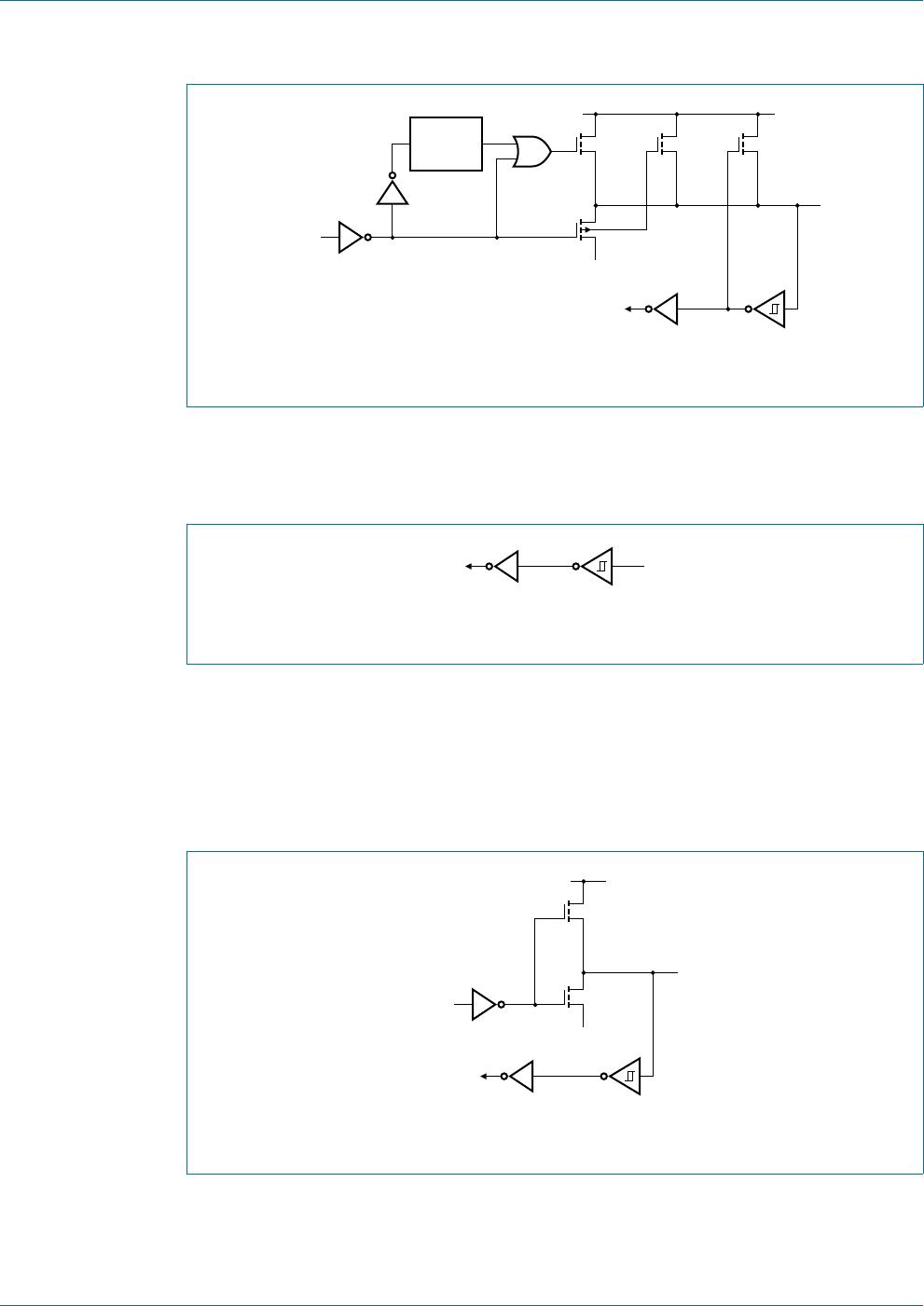

9.2.2.1 Quasi-bidirectional output configuration

Quasi-bidirectional output type can be used as both an input and output without the need

to reconfigure the port. This is possible because when the port outputs a logic HIGH, it is

weakly driven, allowing an external device to pull the pin LOW. When the pin is driven

LOW, it is driven strongly and able to sink a fairly large current. These features are

somewhat similar to an open-drain output except that there are three pull-up transistors in

the quasi-bidirectional output that serve different purposes.

The SC18IM700 is a 3 V device, but the pins are 5 V tolerant. In quasi-bidirectional mode,

if a user applies 5 V on the pin, there will be a current flowing from the pin to V

DD

, causing

extra power consumption. Therefore, applying 5 V in quasi-bidirectional mode is

discouraged.

A quasi-bidirectional port pin has a Schmitt triggered input that also has a glitch

suppression circuit.

Baud rate

7.3728 10

6

16 BRG1 BRG0+

-----------------------------------------------------

=

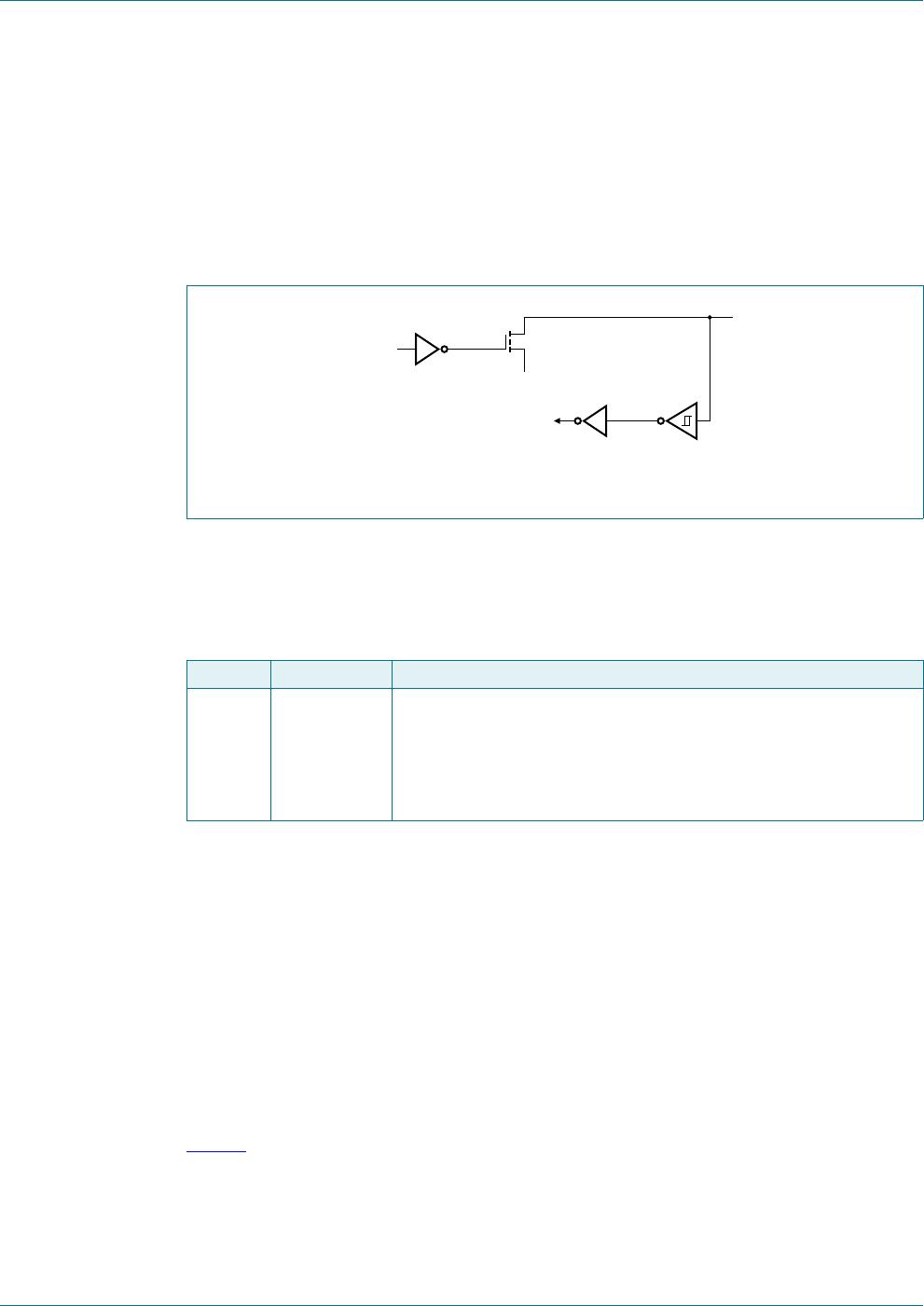

Table 6. Port configurations

GPIOx.1 GPIOx.0 Port configuration

0 0 quasi-bidirectional output configuration

0 1 input-only configuration

1 0 push-pull output configuration

1 1 open-drain output configuration