xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx xxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

SC18IM700_3 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

Product data sheet Rev. 3 — 12 October 2017 9 of 24

NXP Semiconductors

SC18IM700

Master I

2

C-bus controller with UART interface

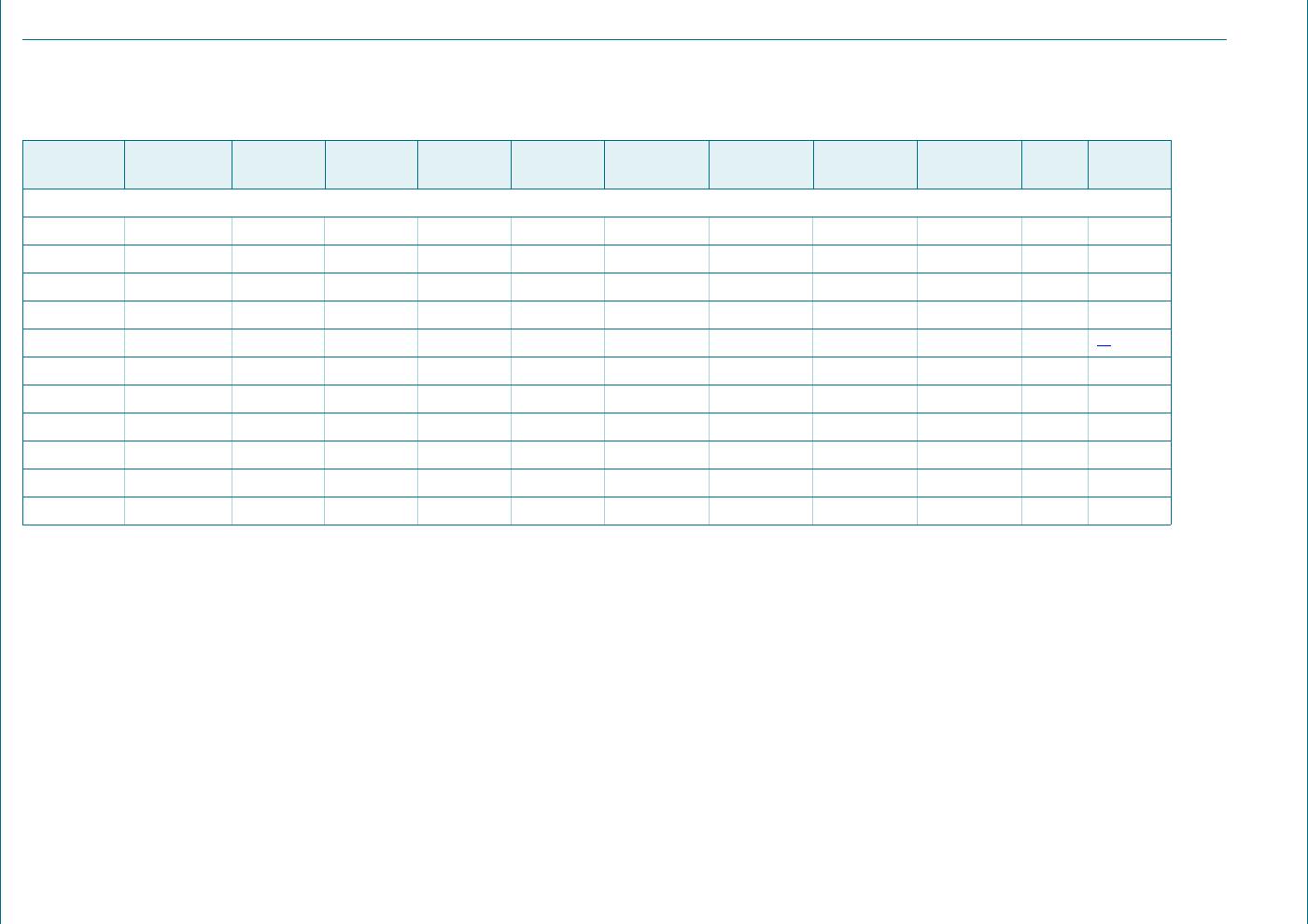

9. Internal registers available

9.1 Register summary

[1] Since the GPIO pins are configured as inputs after reset, the default value of this register depends on the states of the GPIO pins.

Table 5. Internal registers summary

Register

address

Register Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 R/W Default

value

General register set

0x00 BRG0 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W 0xF0

0x01 BRG1 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W 0x02

0x02 PortConf1 GPIO3.1 GPIO3.0 GPIO2.1 GPIO2.0 GPIO1.1 GPIO1.0 GPIO0.1 GPIO0.0 R/W 0x55

0x03 PortConf2 GPIO7.1 GPIO7.0 GPIO6.1 GPIO6.0 GPIO5.1 GPIO5.0 GPIO4.1 GPIO4.0 R/W 0x55

0x04 IOState GPIO7 GPIO6 GPIO5 GPIO4 GPIO3 GPIO2 GPIO1 GPIO0 R/W -

[1]

0x05 reserved bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 - 0x00

0x06 I2CAdr bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W 0x26

0x07 I2CClkL bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W 0x13

0x08 I2CClkH bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W 0x13

0x09 I2CTO TO7 TO6 TO5 TO4 TO3 TO2 TO1 TE R/W 0x66

0x0AI2CStat1111I2CStat[3]I2CStat[2]I2CStat[1]I2CStat[0]R0xF0