AD7152/AD7153 Data Sheet

Rev. A | Page 18 of 24

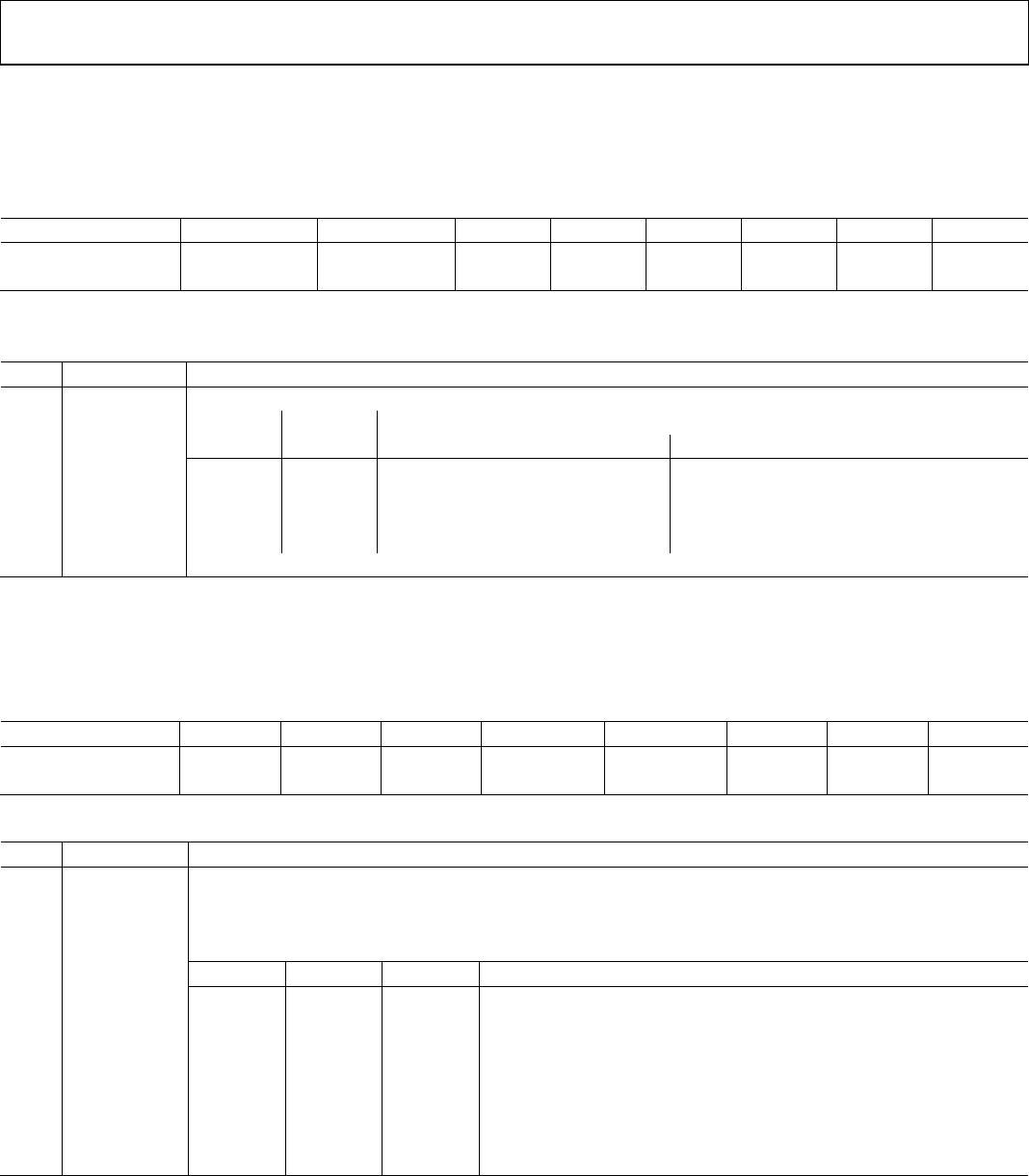

CIRCUIT DESCRIPTION

DIGITAL

FILTER

12-BIT Σ-∆

MODULATOR

CLOCK

GENERATOR

VOLTAGE

REFERENCE

AD7152

I

2

C

SERIAL

INTERFACE

07450-025

EXCITATION

EXC2

CIN1(+)

CIN1(–)

CIN2(+)

CIN2(–)

EXC1

SDA

SCL

DD

GND

CONTROL LOGIC

CALIBRATION

CAP+

CAP–

MUX

Figure 25. AD7152 Block Diagram

DIGITAL

FILTER

12-BIT Σ-∆

MODULATOR

CLOCK

GENERATOR

VOLTAGE

REFERENCE

AD7153

I

2

C

SERIAL

INTERFACE

07450-026

EXCITATION

CIN1(+)

CIN1(–)

EXC1

SDA

SCL

DD

GND

CONTROL LOGIC

CALIBRATION

CAP+

CAP–

MUX

Figure 26. AD7153 Block Diagram

The core of the AD7152/AD7153 is a precision converter

consisting of a second-order modulator (Σ-Δ or charge-

balancing) and a third-order digital filter.

In addition to the converter, the AD7152/AD7153 integrate a

multiplexer, an excitation source, and CAPDACs for the capaci-

tive inputs, a voltage reference, a complete clock generator, a

control and calibration logic, and an I

2

C-compatible serial

interface.

The AD7153 has one capacitive input, while the AD7152 has

two capacitive inputs. For the AD7152, the modulator input and

the excitation source are multiplexed between the converting

channel. All other features and specifications are identical for

both devices.

CAPACITANCE-TO-DIGITAL CONVERTER (CDC)

Figure 27 shows the CDC simplified functional diagram. The

measured capacitance C

X

is connected between the excitation

source and the Σ-Δ modulator input. A square-wave excitation

signal is applied on the C

X

during the conversion and the mod-

ulator continuously samples the charge going through the C

X

.

The digital filter processes the modulator output, which is a

stream of 0s and 1s containing the information in 0 and 1

density. The data from the digital filter is scaled, applying the

calibration coefficients, and the final result can be read through

the serial interface. The AD7152/AD7153 are designed for

floating capacitive sensors. Therefore, both C

X

plates have to

be isolated from ground.

DIGITAL

FILTER

12-BIT Σ-∆

MODULATOR

CLOCK

GENERATOR

CAPACITANCE-TO-DIGITAL CONVERTER

(CDC)

07450-027

EXCITATION

DATA

EXC

CIN

C

X

Figure 27. CDC Simplified Block Diagram

EXCITATION SOURCE

The AD7152/AD7153 have one excitation source. For the

AD7152, the excitation source is switched between the

excitation pins, EXC1 and EXC2, depending on which

channel performs a conversion.