Data Sheet AD7152/AD7153

Rev. A | Page 7 of 24

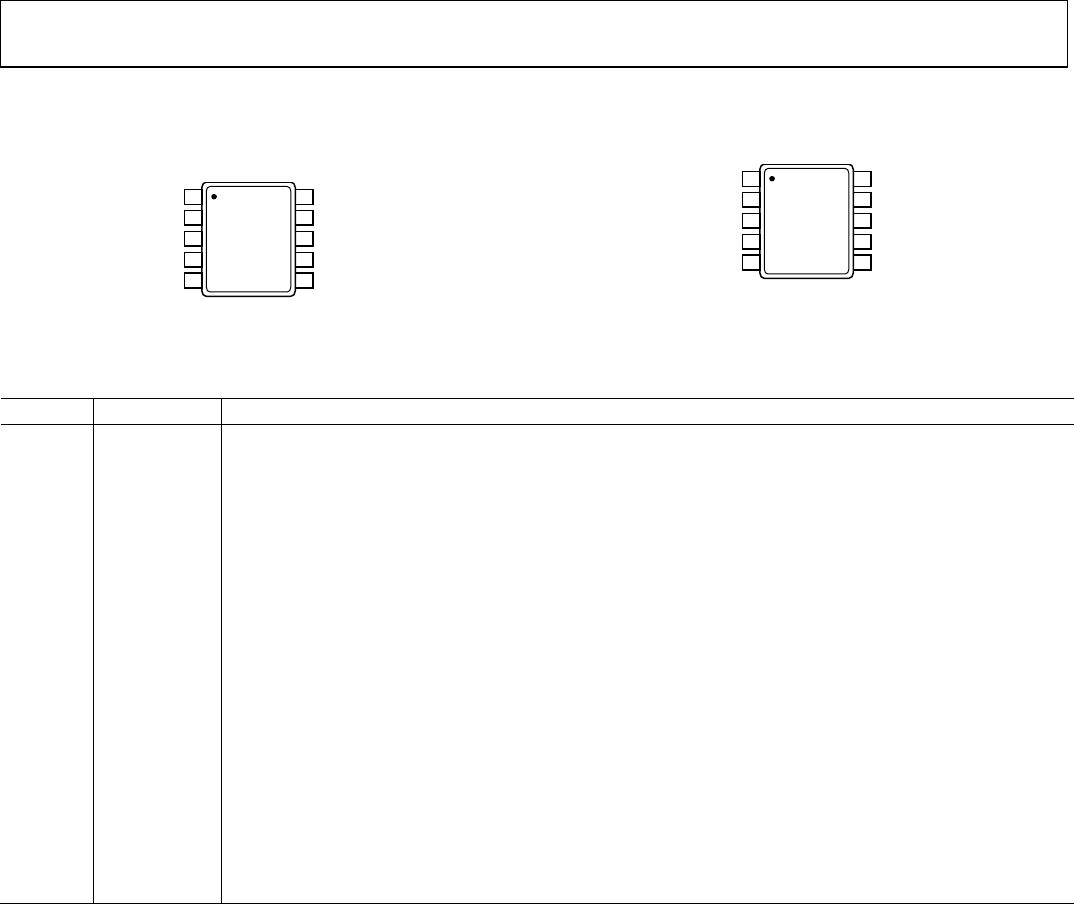

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

GND

1

VDD

2

CIN1(–)

3

CIN1(+)

4

EXC2

5

SDA

10

SCL

9

CIN2(–)

8

CIN2(+)

7

EXC1

6

AD7152

TOP VIEW

(Not to Scale)

07450-004

Figure 4. AD7152 Pin Configuration

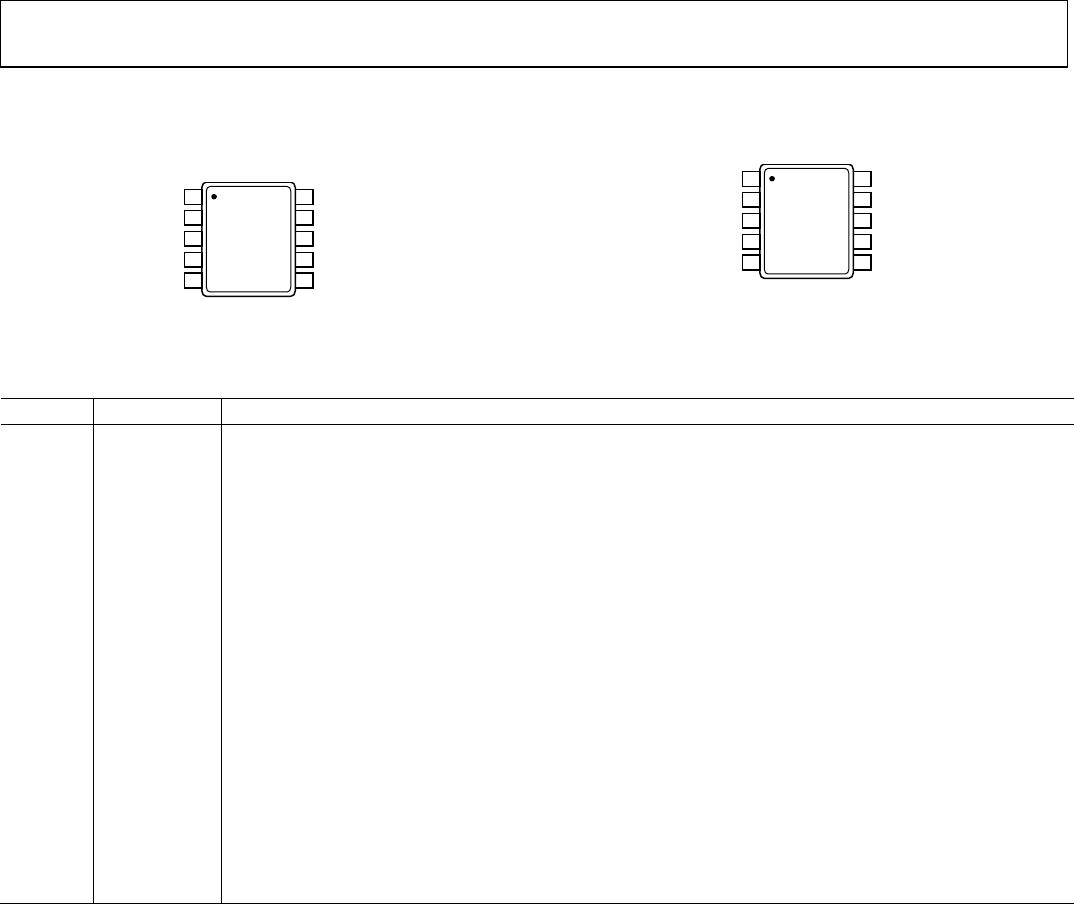

NC = NO CONNECT

GND

1

VDD

2

CIN1(–)

3

CIN1(+)

4

NC

5

SDA

10

SCL

9

NC

8

NC

7

EXC1

6

AD7153

TOP VIEW

(Not to Scale)

07450-005

Figure 5. AD7153 Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 GND Ground Pin.

2 VDD

Power Supply Voltage. This pin should be decoupled to GND, using a low impedance capacitor, for example, in

combination with a 10 μF tantalum and a 0.1 μF multilayer ceramic capacitor.

3 CIN1(–)

CDC Negative Capacitive Input of Channel 1. If not used, this pin can be left as an open circuit or connected to

GND. This pin is internally disconnected in single-ended CDC configuration.

4 CIN1(+) CDC Positive Capacitive Input of Channel 1. If not used, this pin can be left as an open circuit or connected to GND.

5 EXC2/NC

AD7152: CDC Excitation Output for Channel 2. The measured capacitance is connected between one of the EXC

pins and one of the CIN pins. If not used, these pins should be left as an open circuit.

AD7153: No Connect. This pin must be left as an open circuit.

6 EXC1

CDC Excitation Output for Channel 1. The measured capacitance is connected between one of the EXC pins and

one of the CIN pins. If not used, these pins should be left as an open circuit.

7 CIN2(+)/NC

AD7152: CDC Positive Capacitive Input of Channel 2. If not used, this pin can be left as an open circuit or

connected to GND.

AD7153: No Connect. This pin must be left as an open circuit.

8 CIN2(–)/NC

AD7152: CDC Negative Capacitive Input of Channel 2. If not used, this pin can be left as an open circuit or

connected to GND. This pin is internally disconnected in single-ended CDC configuration.

AD7153: No Connect. This pin must be left as an open circuit.

9 SCL

Serial Interface Clock Input. Connects to the master clock line. Requires a pull-up resistor if one is not already

provided in the system.

10 SDA

Serial Interface Bidirectional Data. Connects to the master data line. Requires a pull-up resistor if one is not

provided elsewhere in the system.