Data Sheet AD7152/AD7153

Rev. A | Page 21 of 24

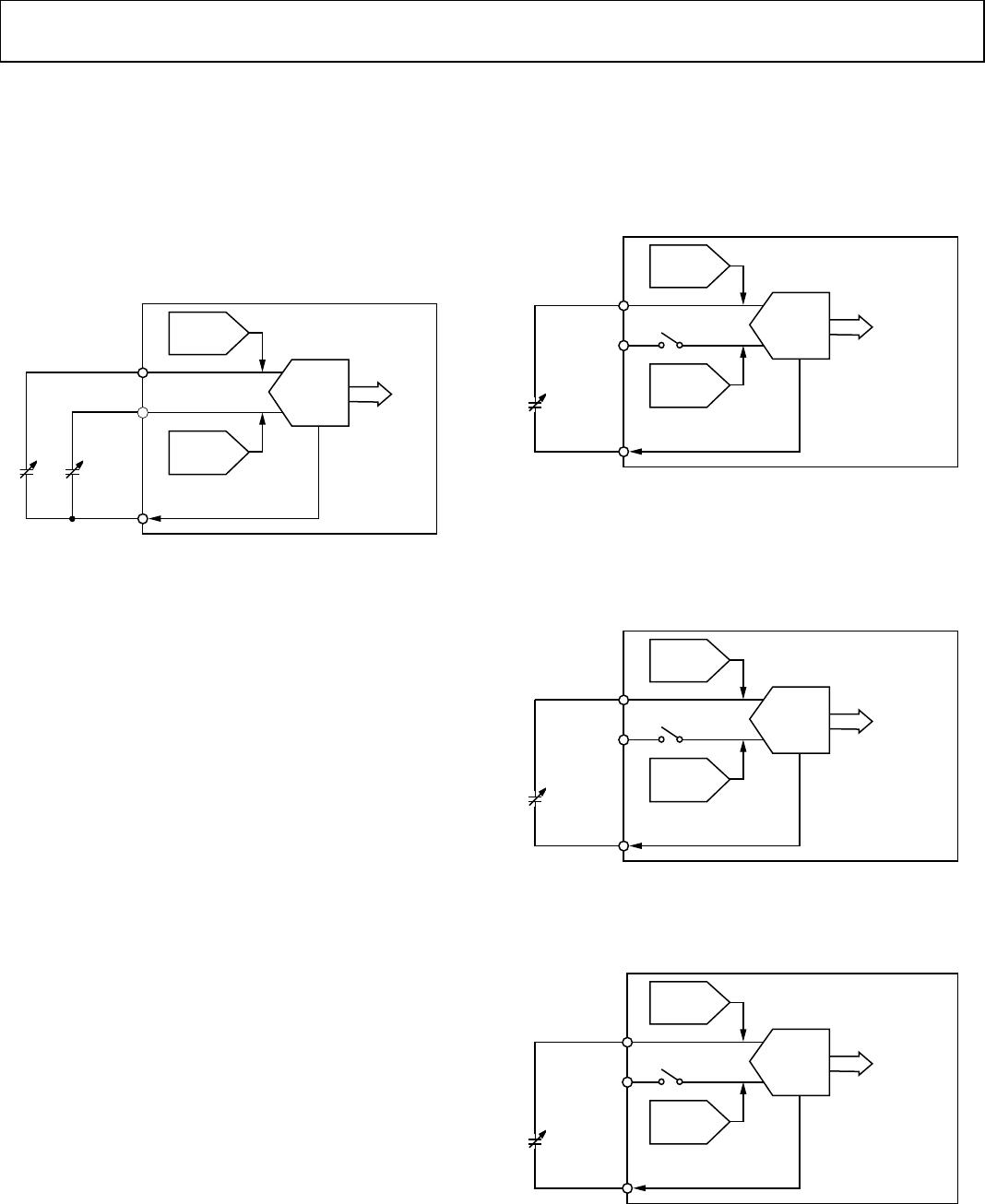

PARASITIC PARALLEL RESISTANCE

DATA

CDC

EXC

CIN

R

P

07450-022

C

X

Figure 37. Parasitic Parallel Resistance

The CDC measures the charge transfer between the EXC pin

and CIN pin. Any resistance connected in parallel to the meas-

ured capacitance C

X

(see Figure 37), such as the parasitic

resistance of the sensor, also transfers charge. Therefore, the

parallel resistor is seen as an additional capacitance in the

output data causing a capacitive input error (see Figure 15).

PARASITIC SERIAL RESISTANCE

DATA

CDC

EXC

R

S1

CIN

R

S2

C

X

07450-023

Figure 38. Parasitic Serial Resistance

The CDC result is affected by a resistance in series with the

measured capacitance. The total serial resistance, which refers

to R

S1

and R

S2

in Figure 38, should be less than 20 kΩ for the

specified performance (see Figure 16).

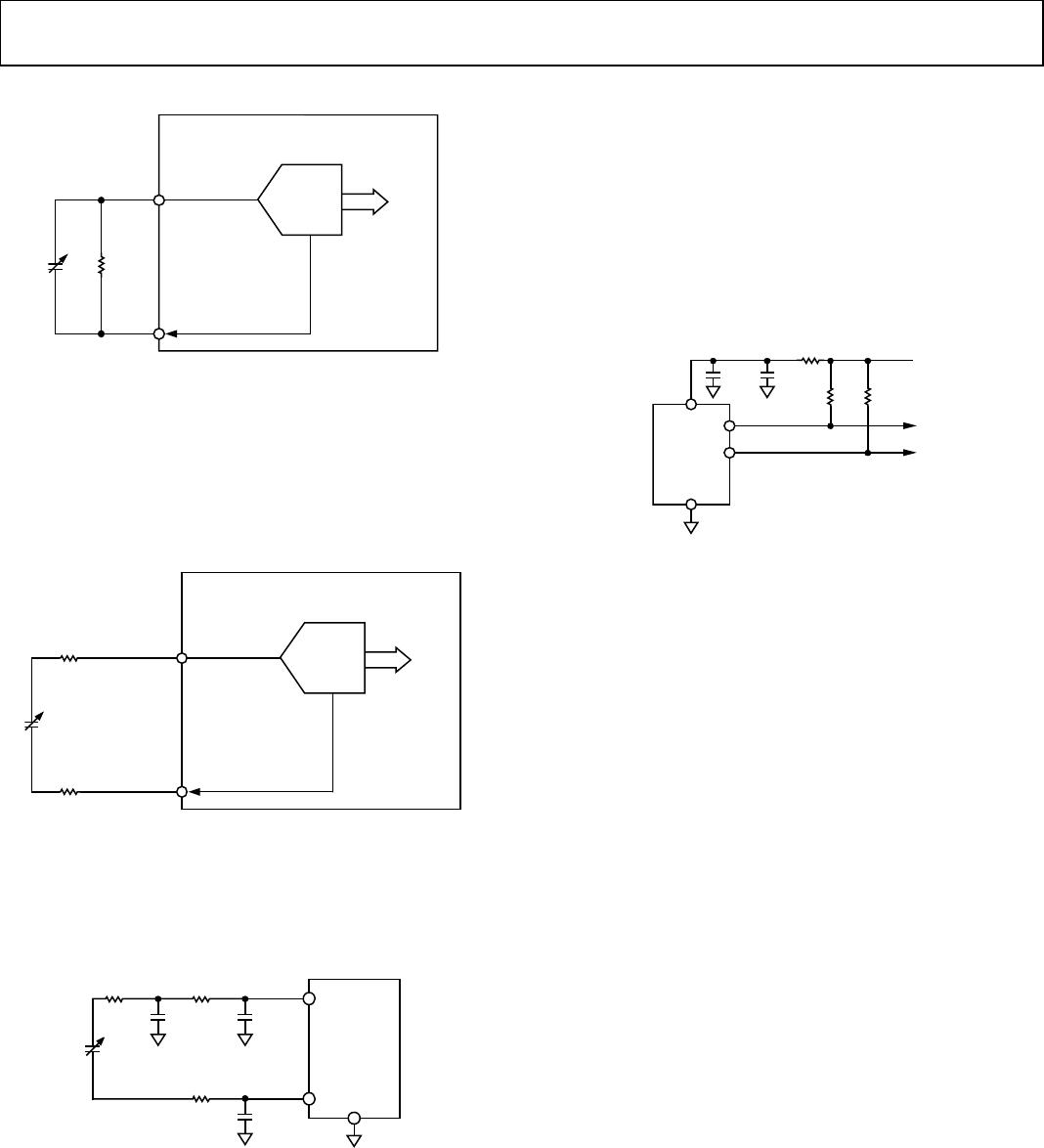

INPUT EMC PROTECTION

CDC

GND

07450-039

CIN

EXC

C2

C3

C

X

R3

R2R1

C1

Figure 39. AD7152/AD7153 EMC Protection

Some applications may require an additional input filter for

improving electromagnetic compatibility (EMC). Any input

filter must be carefully designed, considering the balance between

the system capacitance performance and system electromagnetic

immunity.

Figure 39 shows one of the possible input circuit configurations

significantly improving the system immunity against high fre-

quency noise and slightly affecting the AD7152 performance in

terms of additional gain and offset error.

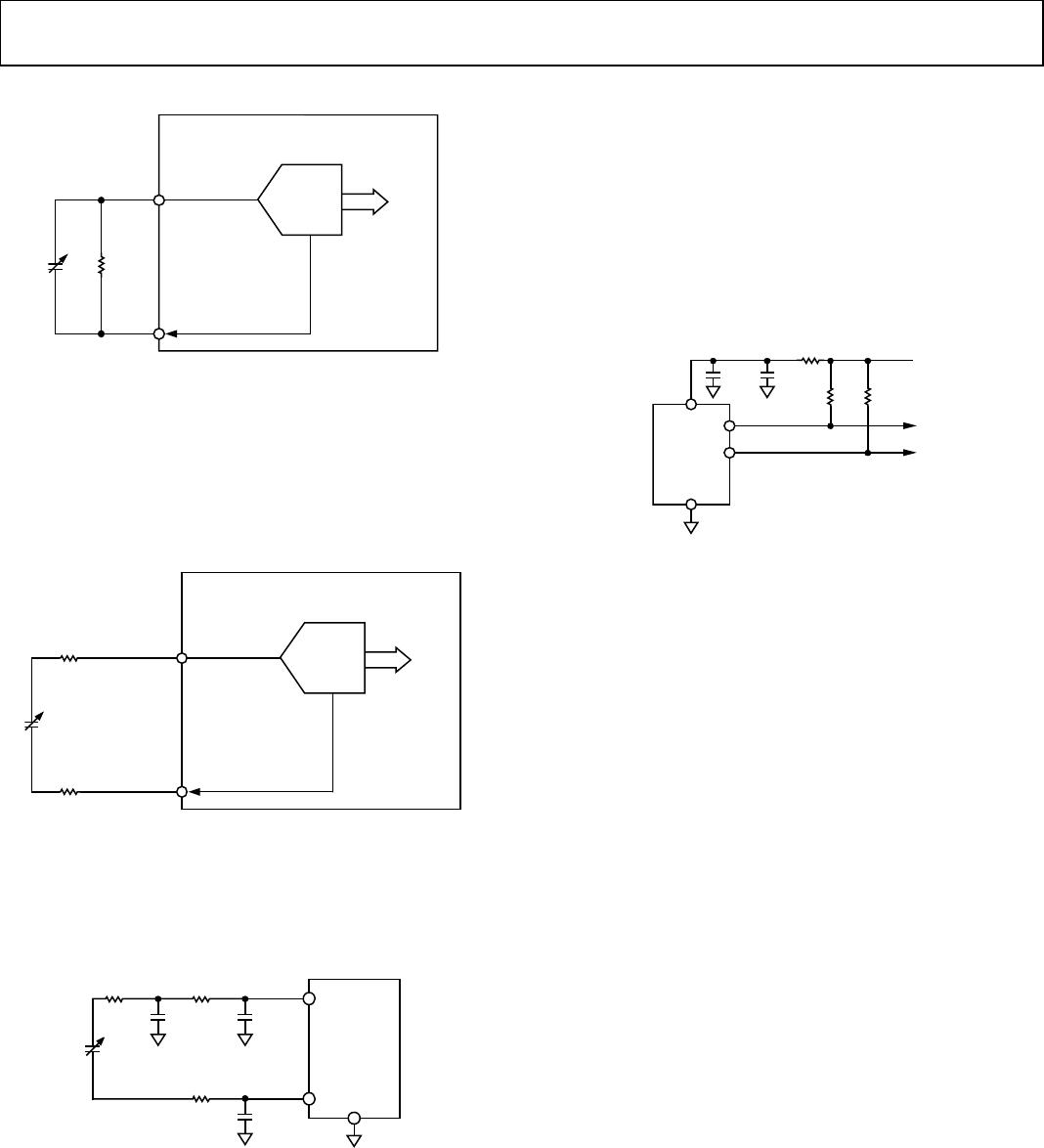

POWER SUPPLY DECOUPLING AND FILTERING

CDC

GND

SDA

SCL

0.1µF 10µF

1kΩ

DD

1kΩ 1kΩ

7450-058

Figure 40. AD7152/AD7153 V

DD

Decoupling and Filtering

The AD7152 has good dc and low frequency power supply

rejection but may be sensitive to higher frequency ripple and

noise, specifically around the excitation frequency and its

harmonics. Figure 40 shows a possible circuit configuration

for improving the system immunity against ripple and noise

coupled to the AD7152 via the power supply.

Because the serial interface is connected to the other circuits in

the system, it is better to connect the pull-up resistors on the

other side of the V

DD

filter than to connect to the AD7152.

CAPACITIVE GAIN CALIBRATION

The gain of the AD7152/AD7153 is factory calibrated for the full

scale of 4 pF in the production for each device individually. The

factory gain coefficient is stored in a one-time programmable

(OTP) memory and is copied to the capacitive gain registers at

power-up or after reset.

The gain can be changed by executing a capacitance gain

calibration mode, for which an external full-scale capacitance

needs to be connected to the capacitance input, or by writing a

user value to the capacitive gain register. This change is tempo-

rary and the factory gain coefficient can be reloaded after

power-up or reset. The device is tested and specified only for

use with the default factory calibration coefficient.

CAPACITIVE SYSTEM OFFSET CALIBRATION

The capacitive offset is dominated by the parasitic offset in the

application, such as the initial capacitance of the sensor, any

parasitic capacitance of tracks on the board, and the capacitance

of any other connections between the sensor and the CDC.

Therefore, the AD7152/AD7153 are not factory calibrated for

capacitive offset. The user should calibrate the system capacitance

offset in the application.