AD7152/AD7153 Data Sheet

Rev. A | Page 4 of 24

Parameter Min Typ Max Unit

1

Test Conditions/Comments

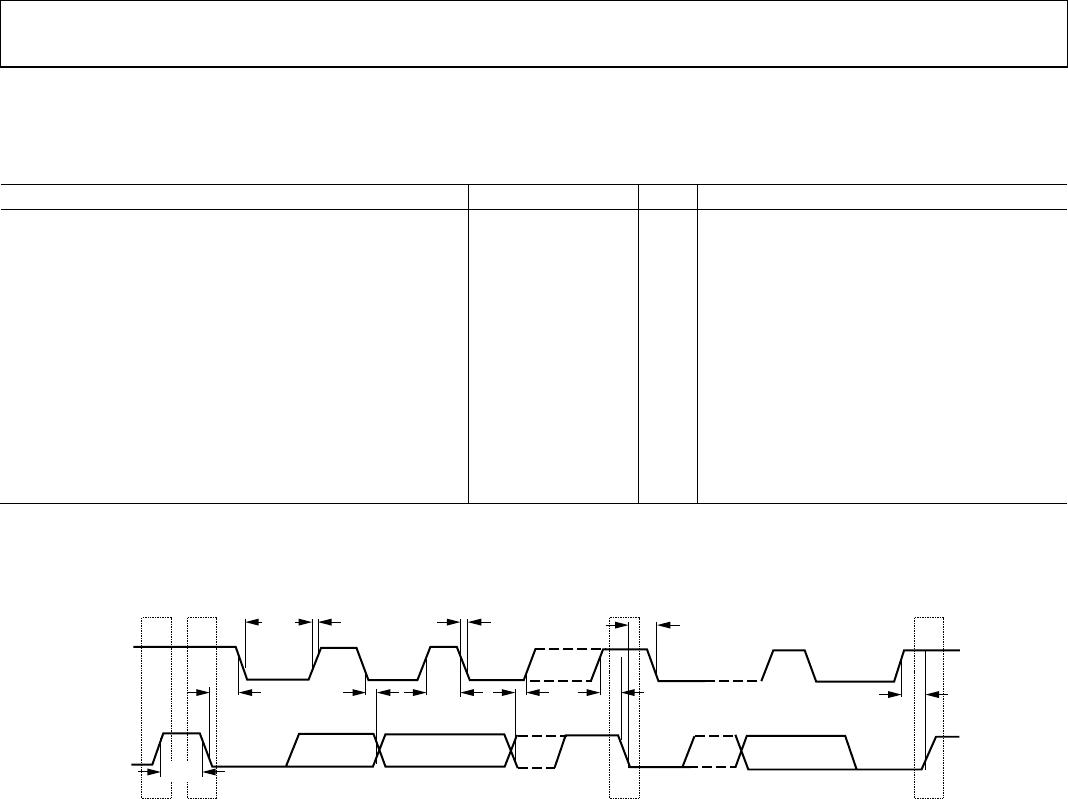

POWER REQUIREMENTS

V

DD

-to-GND Voltage 2.7 3.6 V V

DD

= 3.3 V, nominal

Current, I

DD

9

100 120 µA

Current Power-Down Mode, I

DD

9

1 5 µA Temperature ≤ 25°C

1

Capacitance units: 1 pF = 10

−12

F; 1 fF = 10

−15

F; 1 aF = 10

−18

F.

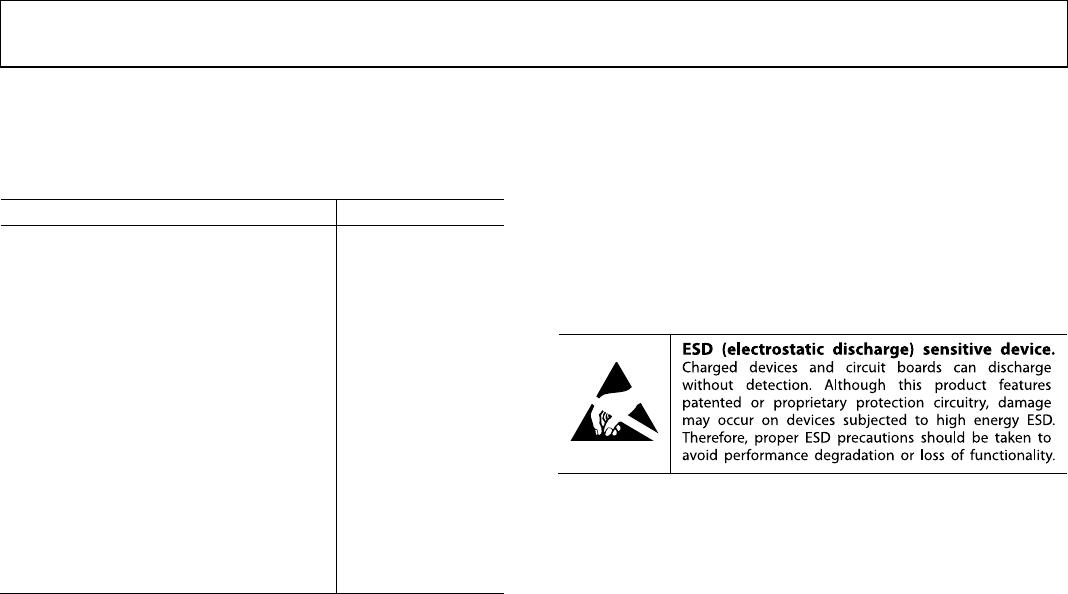

2

Specification is not production tested but is supported by characterization data at initial product release.

3

Except Channel 2 in differential mode. To achieve the specified performance in differential mode, the I

2

C interface must be idle during the capacitance conversion to

prevent signal coupling from the SCL pin to the adjacent CIN2(−) pin.

4

Factory calibrated. The absolute error includes factory gain calibration error and integral nonlinearity error all at 25°C. At different temperatures, compensation for

gain drift over temperature is required.

5

Specification is not production tested but guaranteed by design.

6

A system offset calibration is effectively a conversion; therefore, the offset error is of the order of the conversion noise. This applies after calibration at the temperature,

capacitive input range, and applied V

DD

of interest. The capacitive input offset can be reduced using a system offset calibration. Large offsets should be removed using

CAPDACs.

7

The gain error is factory calibrated at 25°C. At different temperatures, compensation for gain drift over temperature is required.

8

The CAPDAC resolution is five bits in the actual CAPDAC full range. Using the on-chip offset calibration or adjusting the capacitive offset calibration register can

further reduce the CIN offset or the unchanging CIN component.

9

Digital inputs equal to V

DD

or GND.