1©2017 Integrated Device Technology, Inc. October 24, 2017

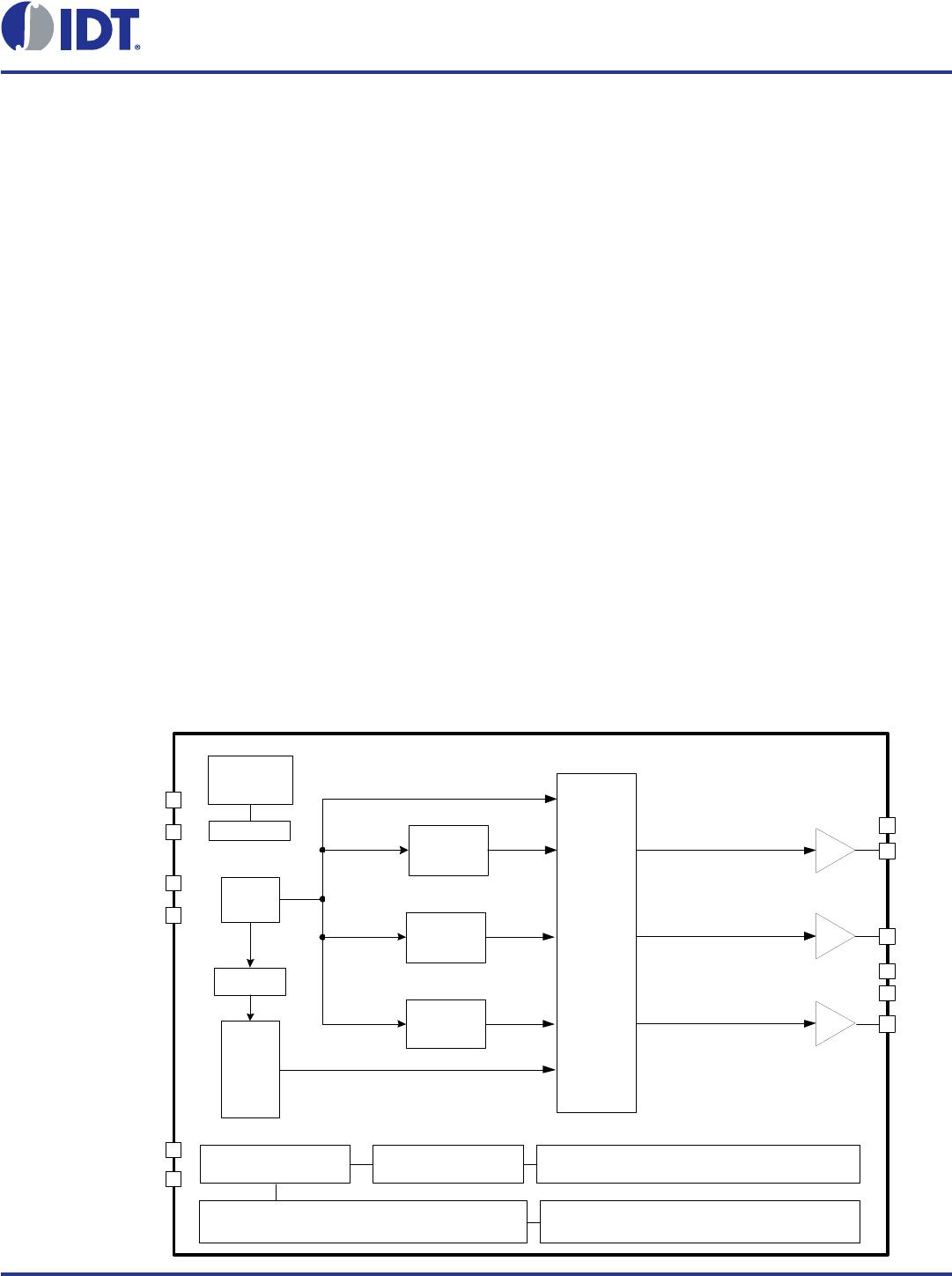

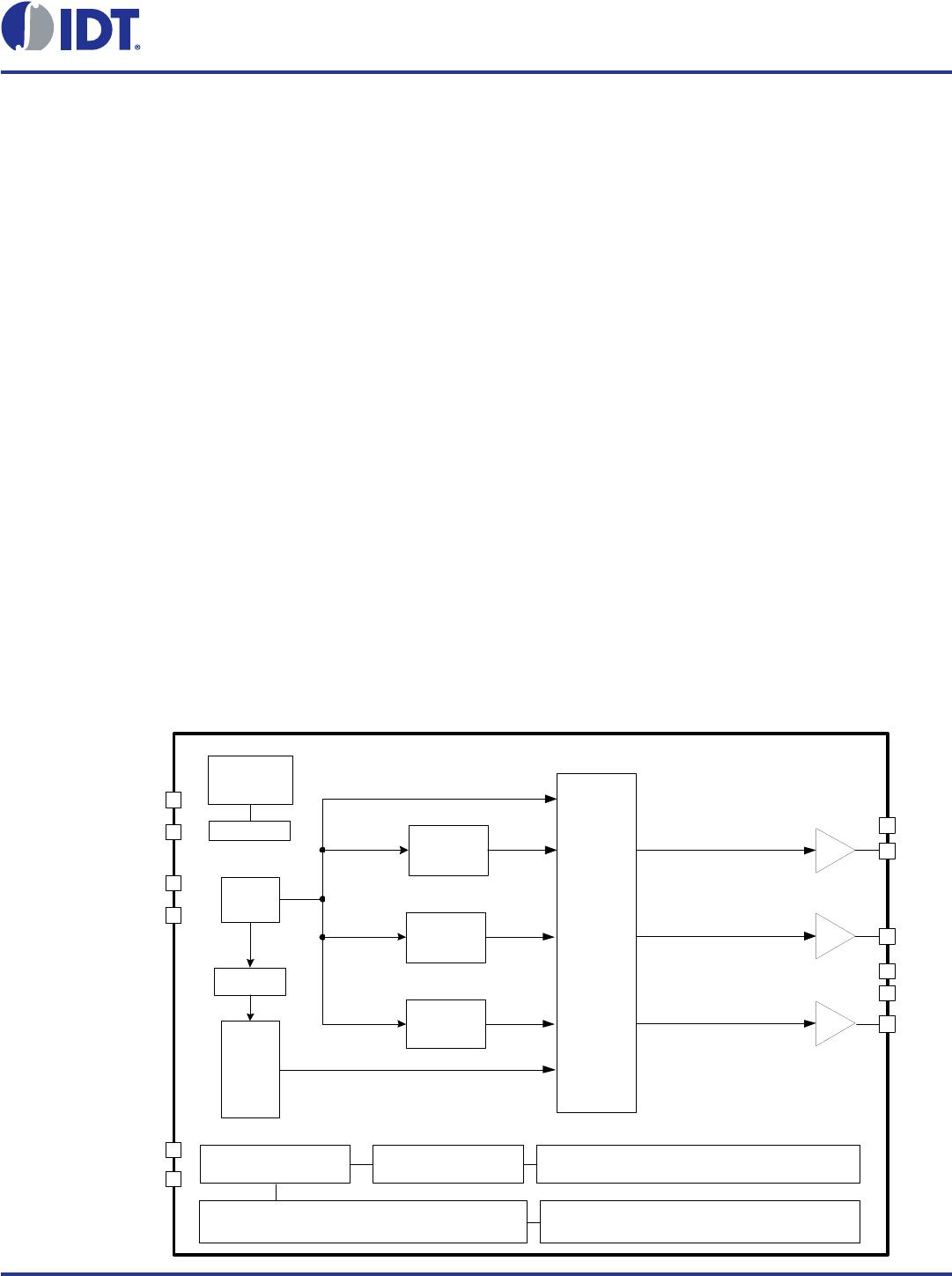

Description

The 5L2503 MicroClock programmable clock generator is

intended for low-power, consumer, wearable and smart devices.

The 5L2503 device is a 3 PLL architecture design. Each PLL is

individually programmable, allowing up to 3 unique frequency

outputs. The 5L2503 has built-in unique features such as

Proactive Power Saving (PPS) to deliver better system level

power management.

An internal OTP memory allows the user to store the configuration

in the device without programming after power-up, and then can

be reprogrammed again through the I

2

C interface.

The device has programmable VCO and PLL source selection

allowing the user to do power-performance optimization based on

the application requirements. A low-power 32.768kHz clock is

supported with only less than 2μA current consumption for system

RTC reference clock needs.

Typical Applications

▪ SmartDevice

▪ Handheld

▪ Wearable applications

▪ Consumer application crystal replacements

Features

▪ Configurable OE1 pin function as OE, PPS or DFC control

function

▪ Proactive Power Saving (PPS) features save power during the

end device power down mode

▪ Dynamic Frequency Control (DFC) feature allows programming

up to 4 difference frequencies switch dynamically

▪ Spread spectrum clock support to lower system EMI

▪ I

2

C Interface

Output Features

▪ 3 LVCMOS outputs: 1MHz–125MHz

▪ Low Power 32.768kHz clock supported

▪ Wireless clock crystal integration and fan out directly

Key Specifications

▪ 2μA operation for RTC clock 32.768kHz output

▪ 2.5 × 2.5 mm 12-DFN small form factor package

Block Diagram

Overshoot Reduction

(ORT)

OSC

PLL2

OUT3

OUT2

OUT1

PLL3

OE1

SDA_DFC0/OE2

SEL_DFC/ SCL_DFC1/OE3

OTP memory (1 configuration ) Proactive Power Saving Logic (PPS)

I

2

C Engine Dynamic Frequency Control Logic (DFC)

POR

Power

Monitor

VDD1_8

32.768K

DCO

Calibration

VSS

VDDO

PLL1

VSS

Mux

&

Divider

XOUT

CLKIN / XIN

5L2503

Datasheet

MicroClock Programmable Clock

Generator