19©2017 Integrated Device Technology, Inc. October 24, 2017

5L2503 Datasheet

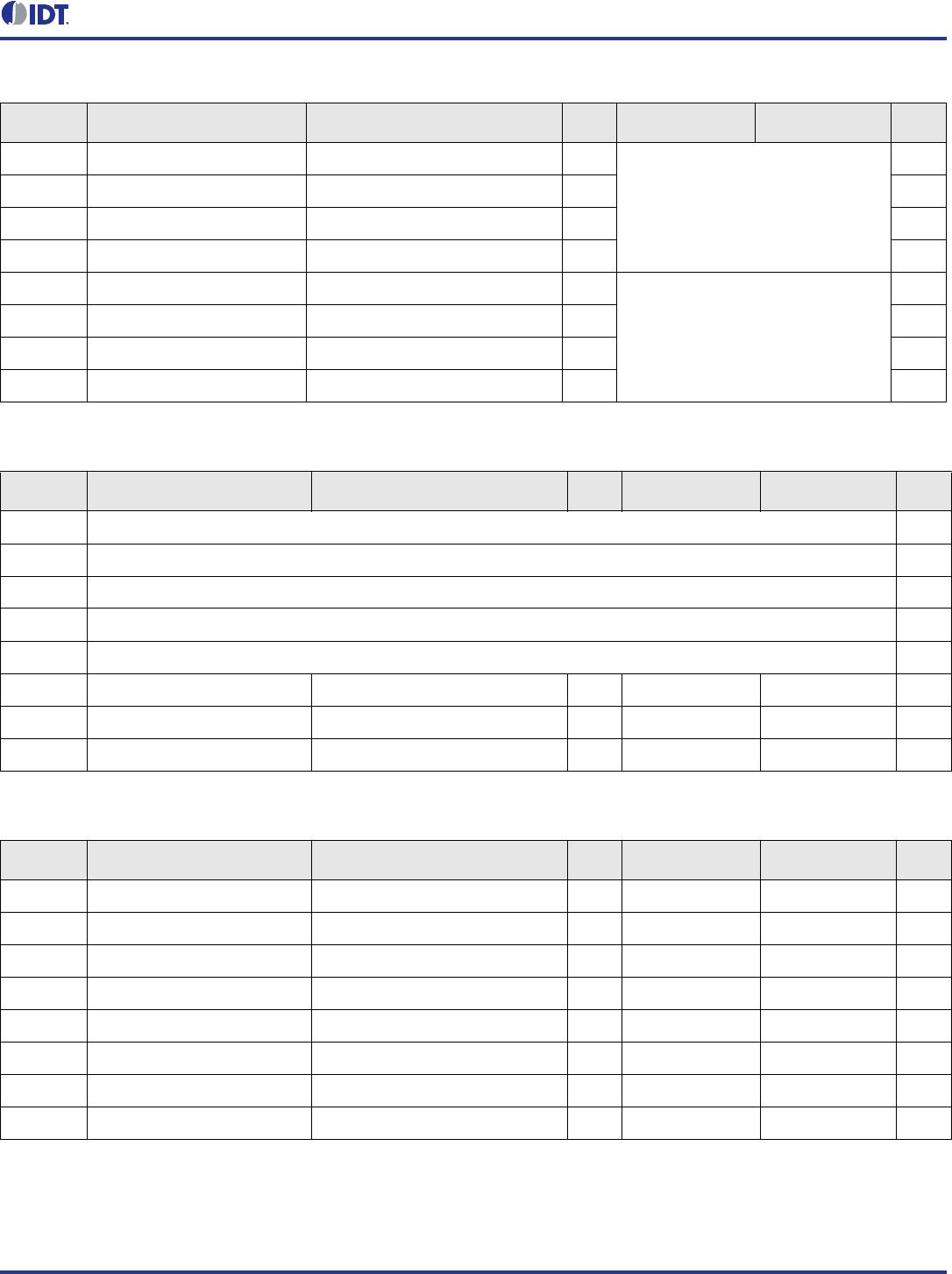

Byte 15: Output Divider1 Control

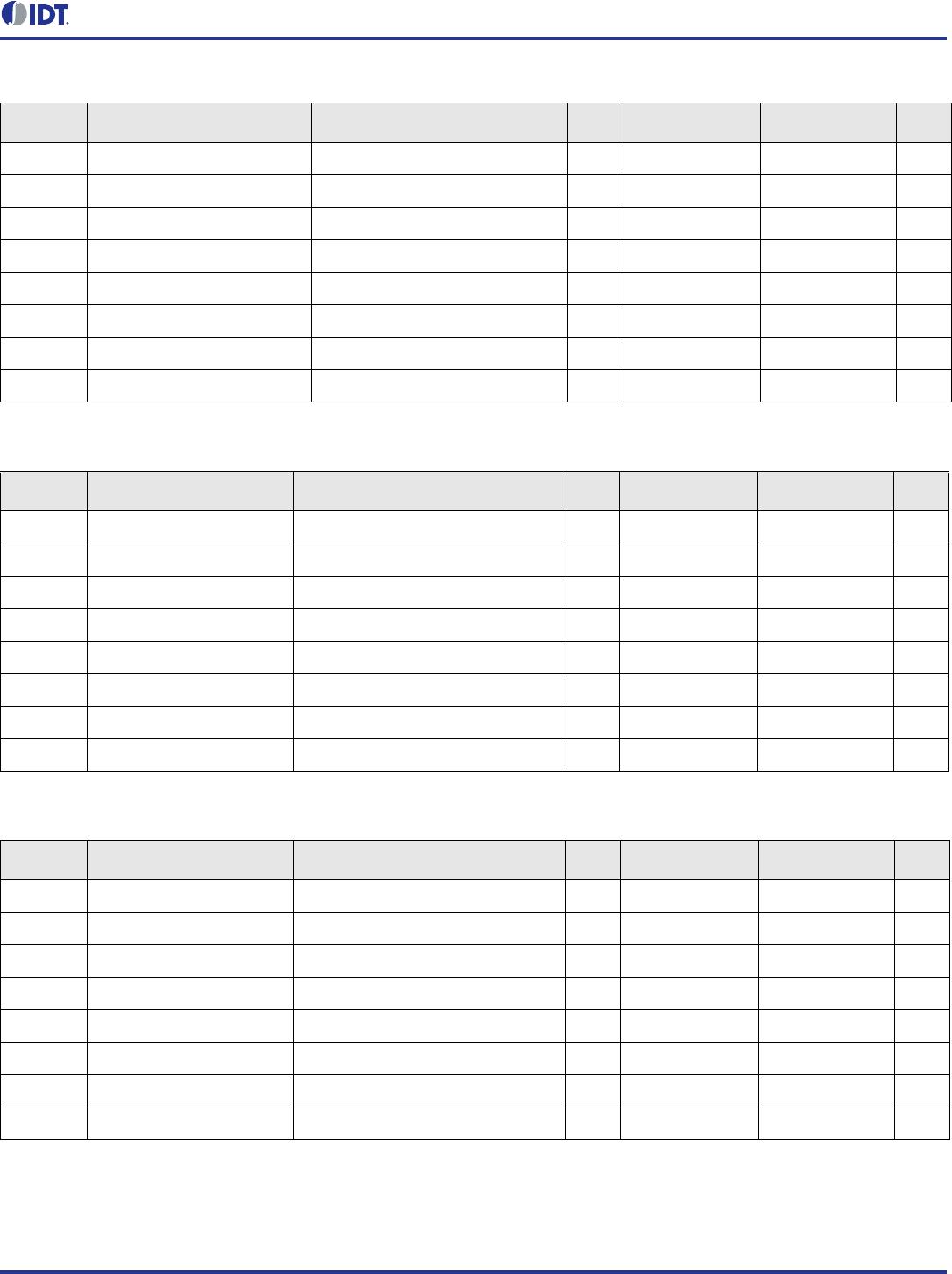

Byte 16: PLL2 Integer Feedback Divide

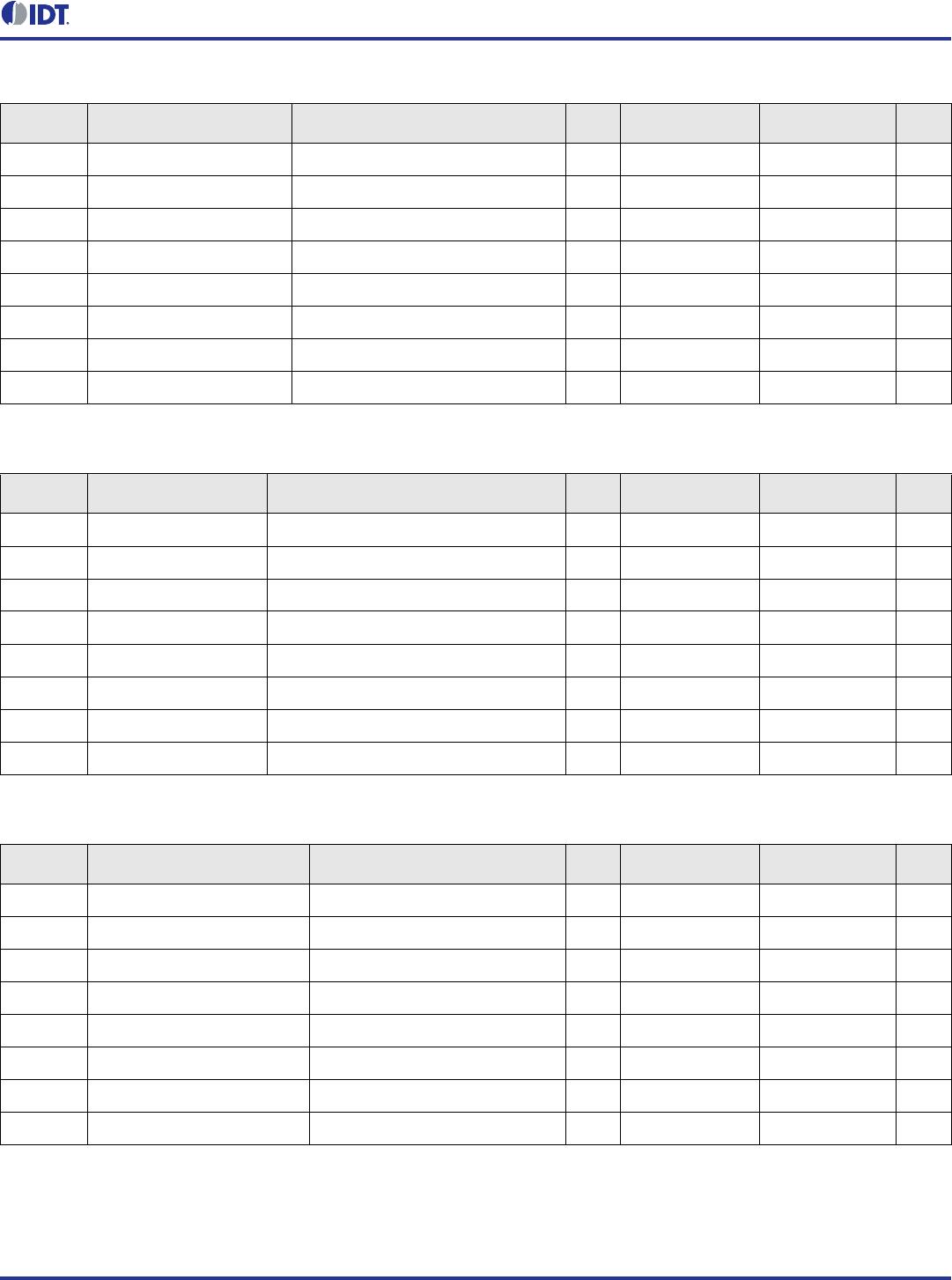

Byte 17: PLL2 Integer Feedback Divider

Byte 0Fh Name Control Function Type 0 1 PWD

Bit 7 OUTDIV1[3] Output divider1 control bit 3 R/W

DIV1[3:2] = 1,2,4,8; DIV1[1:0] =

1,4,5,6; Default Divider = 1 x 1 = 1

0

Bit 6 OUTDIV1[2] Output divider1 control bit 2 R/W 0

Bit 5 OUTDIV1[1] Output divider1 control bit 1 R/W 0

Bit 4 OUTDIV1[0] Output divider1 control bit 0 R/W 0

Bit 3 OUTDIV2[3] Output divider2 control bit 3 R/W

DIV2[3:2] = 1,2,4,5; DIV2[1:0] =

1,3,5,10; Default Divider = 1 x 10 =

10

0

Bit 2 OUTDIV2[2] Output divider2 control bit 2 R/W 0

Bit 1 OUTDIV2[1] Output divider2 control bit 1 R/W 1

Bit 0 OUTDIV2[0] Output divider2 control bit 0 R/W 1

Byte 10h Name Control Function Type 0 1 PWD

Bit 7 Reserved 0

Bit 6 Reserved 0

Bit 5 Reserved 0

Bit 4 Reserved 0

Bit 3 Reserved 0

Bit 2 PLL2_FB_INT[10] PLL2 feedback integer divider 10 R/W — — 0

Bit 1 PLL2_FB_INT[9] PLL2 feedback integer divider 9 R/W — — 0

Bit 0 PLL2_FB_INT[8] PLL2 feedback integer divider 8 R/W — — 0

Byte 11h Name Control Function Type 0 1 PWD

Bit 7 PLL2_FB_INT_DIV[7] PLL2 feedback integer divider 7 R/W — — 0

Bit 6 PLL2_FB_INT_DIV[6] PLL2 feedback integer divider 6 R/W — — 0

Bit 5 PLL2_FB_INT_DIV[5] PLL2 feedback integer divider 5 R/W — — 1

Bit 4 PLL2_FB_INT_DIV[4] PLL2 feedback integer divider 4 R/W — — 1

Bit 3 PLL2_FB_INT_DIV[3] PLL2 feedback integer divider 3 R/W — — 1

Bit 2 PLL2_FB_INT_DIV[2] PLL2 feedback integer divider 2 R/W — — 1

Bit 1 PLL2_FB_INT_DIV[1] PLL2 feedback integer divider 1 R/W — — 0

Bit 0 PLL2_FB_INT_DIV[0] PLL2 feedback integer divider 0 R/W — — 0