22©2017 Integrated Device Technology, Inc. October 24, 2017

5L2503 Datasheet

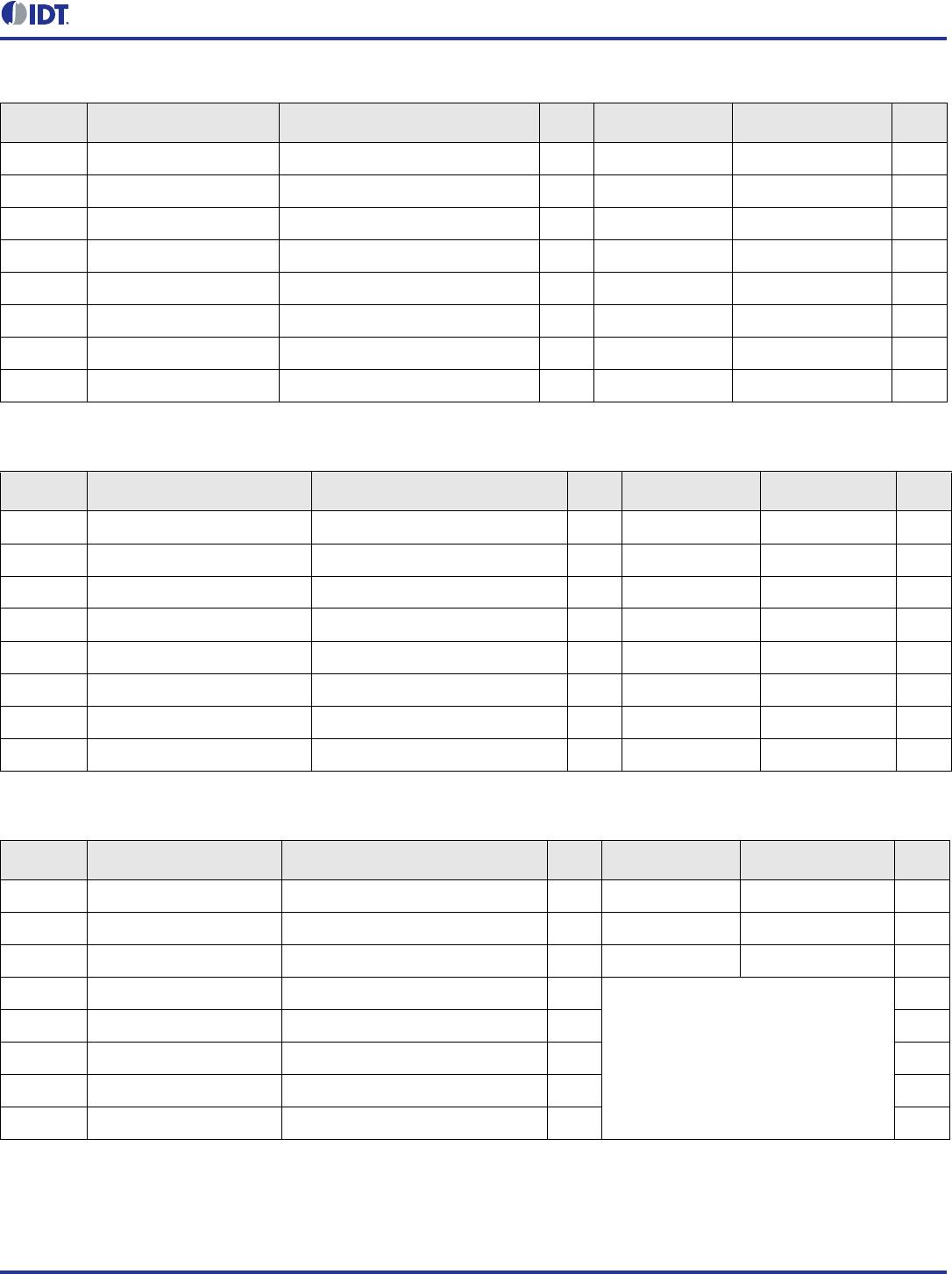

Byte 24: PLL2 Control Register

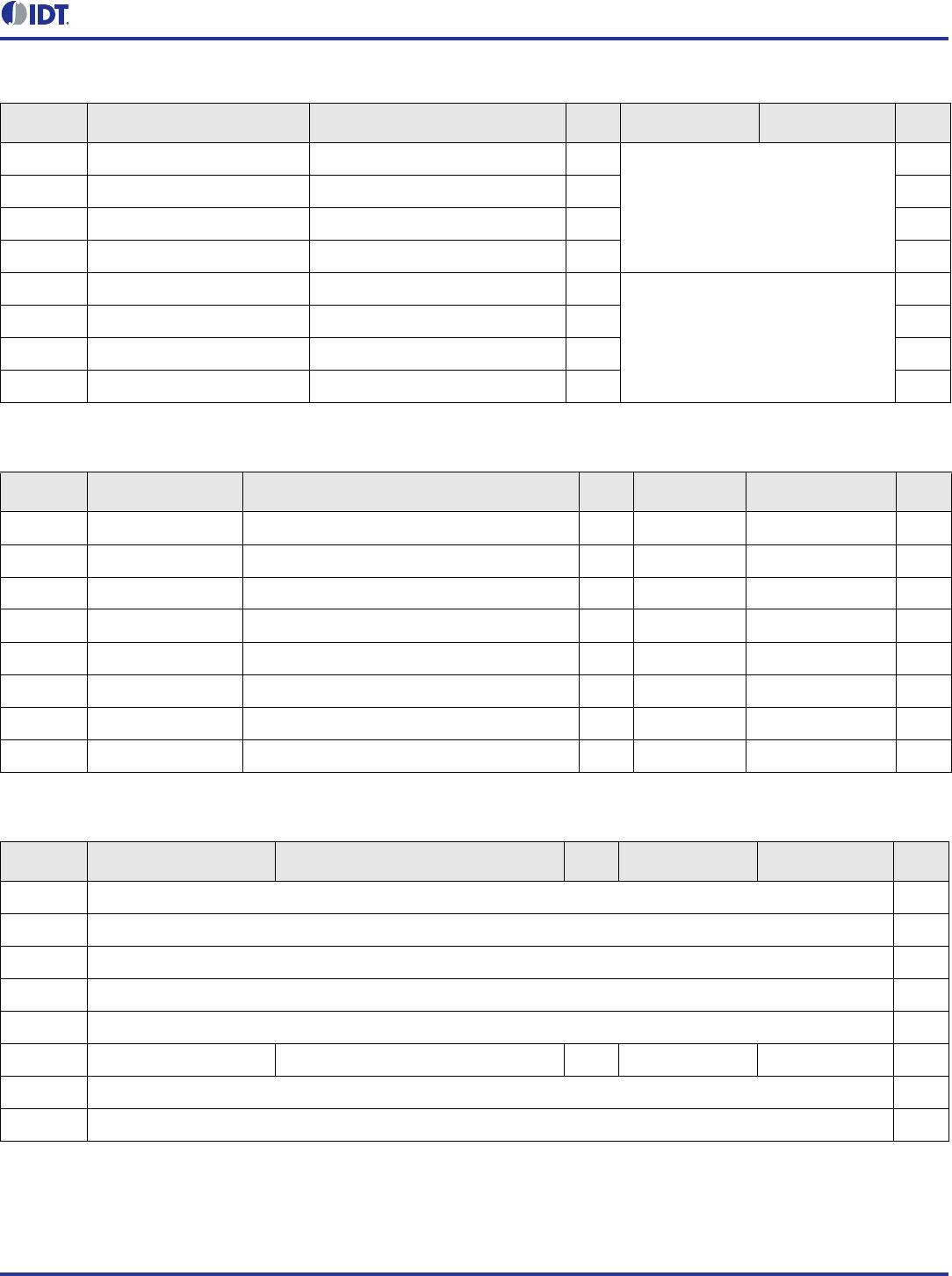

Byte 25: PLL2 Charge Pump Control

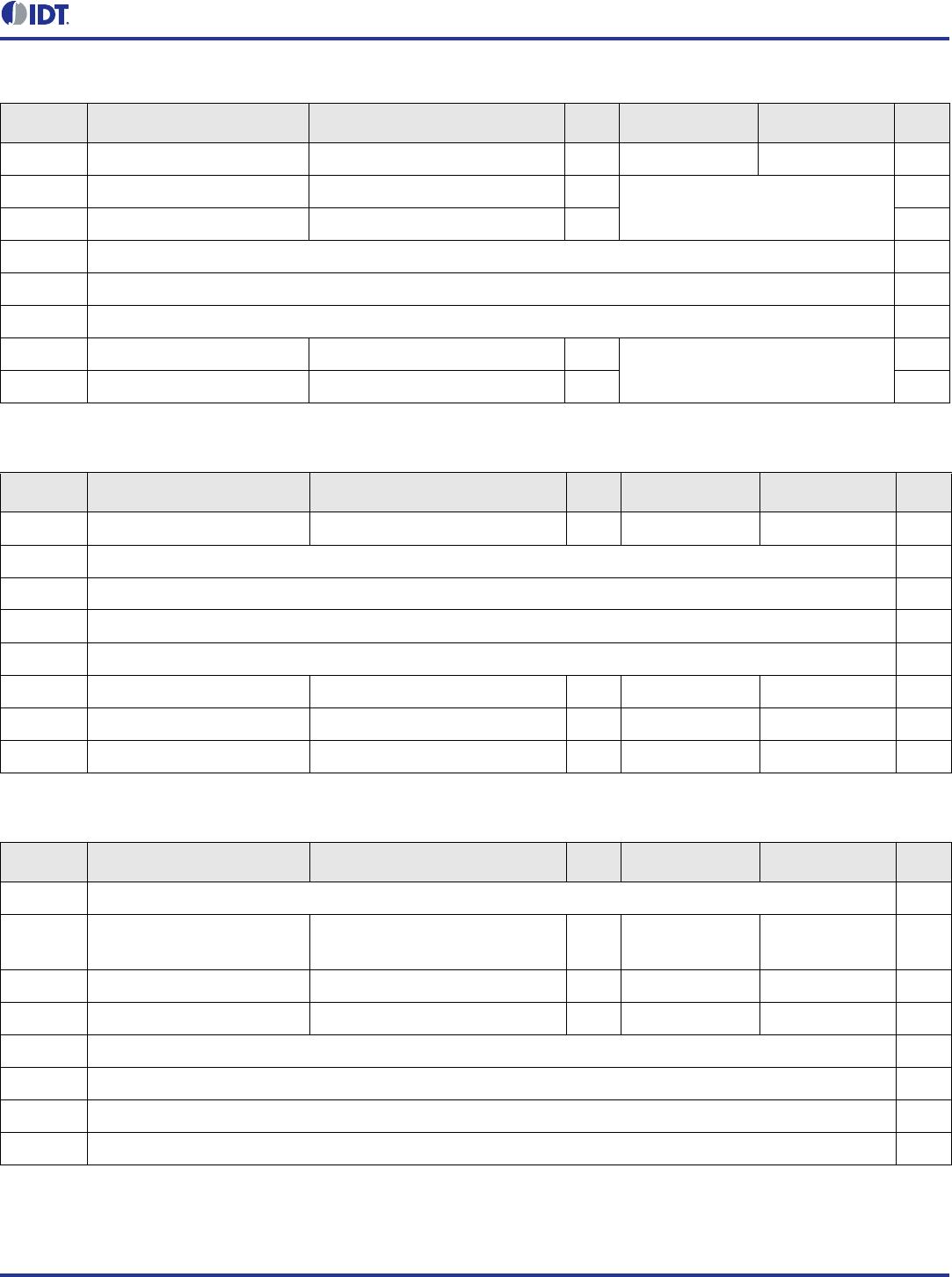

Byte 26: PLL2 M Divider Setting

Byte 18h Name Control Function Type 0 1 PWD

Bit 7 PLL2_PERIOD[9] PLL2 period control bit 9 R/W — — 0

Bit 6 PLL2_PERIOD[8] PLL2 period control bit 8 R/W — — 0

Bit 5 PLL2_SSEN PLL2 spread spectrum enable R/W disable enable 0

Bit 4 PLL2_R100K PLL2 loop filter resister 100kohm — bypass plus 100kohm 0

Bit 3 PLL2_R50K PLL2 loop filter resister 50kohm — bypass plus 50kohm 1

Bit 2 PLL2_R25K PLL2 loop filter resister 25kohm — bypass plus 25kohm 1

Bit 1 PLL2_R12.5K PLL2 loop filter resister 12.5kohm — bypass plus 12.5kohm 1

Bit 0 PLL2_R6K PLL2 loop filter resister 6kohm — bypass only 6kohm applied 0

Byte 19h Name Control Function Type 0 1 PWD

Bit 7 PLL2_CP_16X PLL2 charge pump control R/W — x16 0

Bit 6 PLL2_CP_8X PLL2 charge pump control R/W — x8 0

Bit 5 PLL2_CP_4X PLL2 charge pump control R/W — x4 0

Bit 4 PLL2_CP_2X PLL2 charge pump control R/W — x2 1

Bit 3 PLL2_CP_1X PLL2 charge pump control R/W — x1 0

Bit 2 PLL2_CP_/24 PLL2 charge pump control R/W — /24 1

Bit 1 PLL2_CP_/3 PLL2 charge pump control R/W — /3 0

Bit 0 PLL2_SIREF PLL2 SiRef current selection R/W 10μA20μA0

Byte 1Ah Name Control Function Type 0 1 PWD

Bit 7 PLL2_MDIV_Doubler PLL2 reference divider - doubler R/W disable enable 0

Bit 6 PLL2_MDIV1 PLL2 reference divider 1 R/W disable M DIV1 bypadd divider (/1) 0

Bit 5 PLL2_MDIV2 PLL2 reference divider 2 R/W disable M DIV2 bypadd divider (/2) 0

Bit 4 PLL2_MDIV[4] PLL2 reference divider control bit 4 R/W

3–64, default is 26

1

Bit 3 PLL2_MDIV[3] PLL2 reference divider control bit 3 R/W 1

Bit 2 PLL2_MDIV[2] PLL2 reference divider control bit 2 R/W 0

Bit 1 PLL2_MDIV[1] PLL2 reference divider control bit 1 R/W 1

Bit 0 PLL2_MDIV[0] PLL2 reference divider control bit 0 R/W 0