15©2017 Integrated Device Technology, Inc. October 24, 2017

5L2503 Datasheet

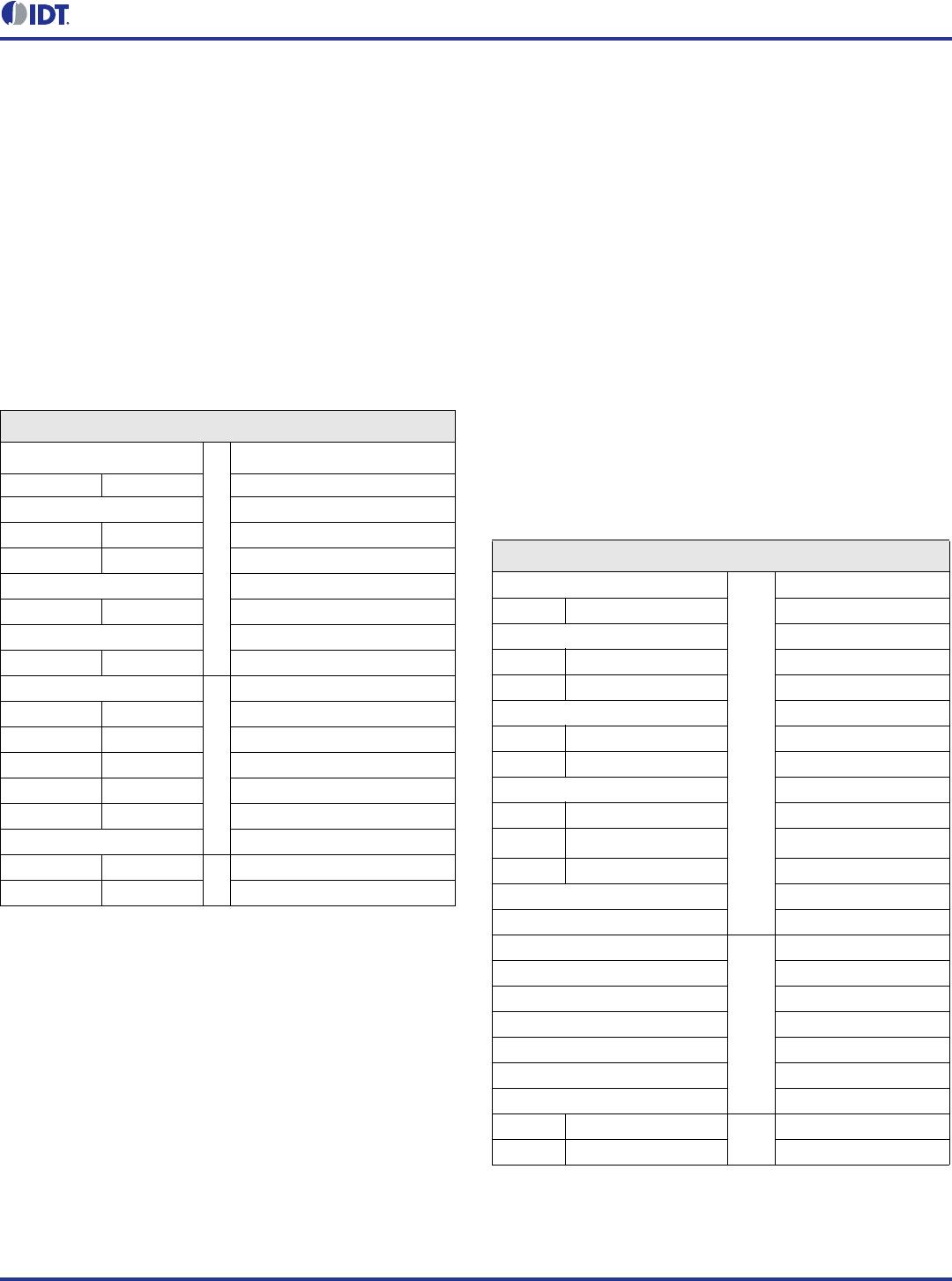

Byte 3: PLL3 M Divider

Byte 4: PLL3 N Divider

Byte 5: PLL3 Loop Filter Setting and N Divider 10:8

Byte 03h Name Control Function Type 0 1 PWD

Bit 7 PLL3_MDIV1 PLL3 source clock divider R/W disable M DIV1 bypadd divider (/1) 0

Bit 6 PLL3_MDIV2 PLL3 source clock divider R/W disable M DIV2 bypadd divider (/2) 0

Bit 5 PLL3 M_DIV[5] PLL3 reference integer divider R/W

3–64, default 26

0

Bit 4 PLL3 M_DIV[4] PLL3 reference integer divider R/W 1

Bit 3 PLL3 M_DIV[3] PLL3 reference integer divider R/W 1

Bit 2 PLL3 M_DIV[2] PLL3 reference integer divider R/W 0

Bit 1 PLL3 M_DIV[1] PLL3 reference integer divider R/W 1

Bit 0 PLL3 M_DIV[0] PLL3 reference integer divider R/W 0

Byte 04h Name Control Function Type 0 1 PWD

Bit 7 PLL3 N_DIV[7] PLL3 VCO feedback integer divider bit7 R/W

12–2048, default VCO setting is

480MHz

1

Bit 6 PLL3 N_DIV[6] PLL3 VCO feedback integer divider bit6 R/W 1

Bit 5 PLL3 N_DIV[5] PLL3 VCO feedback integer divider bit5 R/W 1

Bit 4 PLL3 N_DIV[4] PLL3 VCO feedback integer divider bit4 R/W 0

Bit 3 PLL3 N_DIV[3] PLL3 VCO feedback integer divider bit3 R/W 0

Bit 2 PLL3 N_DIV[2] PLL3 VCO feedback integer divider bit2 R/W 0

Bit 1 PLL3 N_DIV[1] PLL3 VCO feedback integer divider bit1 R/W 0

Bit 0 PLL3 N_DIV[0] PLL3 VCO feedback integer divider bit0 R/W 0

Byte 05h Name Control Function Type 0 1 PWD

Bit 7 PLL3_R100K PLL3 Loop filter resister 100kohm R/W bypass plus 100kohm 0

Bit 6 PLL3_R50K PLL3 Loop filter resister 50kohm R/W bypass plus 50kohm 0

Bit 5 PLL3_R25K PLL3 Loop filter resister 25kohm R/W bypass plus 25kohm 0

Bit 4 PLL3_R12.5K PLL3 Loop filter resister 12.5kohm R/W bypass plus 12.5kohm 1

Bit 3 PLL3_R6K PLL3 Loop filter resister 6kohm R/W bypass

only 6kohm

applied

0

Bit 2 PLL3 N_DIV[10] PLL3 VCO feedback integer divider bit10 R/W

12–2048, default VCO setting is

480MHz

0

Bit 1 PLL3 N_DIV[9] PLL3 VCO feedback integer divider bit9 R/W 0

Bit 0 PLL3 N_DIV[8] PLL3 VCO feedback integer divider bit8 R/W 1