REV. B

AD7865

–15–

When operating the AD7865 in a standby mode between con-

versions, the power savings can be significant. For example,

with a throughput rate of 10 kSPS and external reference, the

AD7865 will be powered up 11 µs out of every 100 µs (1 µs for

wake-up time and 9.6 µs to convert four channels. Therefore,

the average power consumption drops to (115 mW × 10.6%) or

12.2 mW approximately.

OFFSET AND FULL-SCALE ADJUSTMENT

In most Digital Signal Processing (DSP) applications, offset and

full-scale errors have little or no effect on system performance.

Offset error can always be eliminated in the analog domain by

ac coupling. Full-scale error effect is linear and does not cause

problems as long as the input signal is within the full dynamic

range of the ADC. Invariably, some applications will require

that the input signal span the full analog input dynamic range.

In such applications, offset and full-scale error will have to be

adjusted to zero.

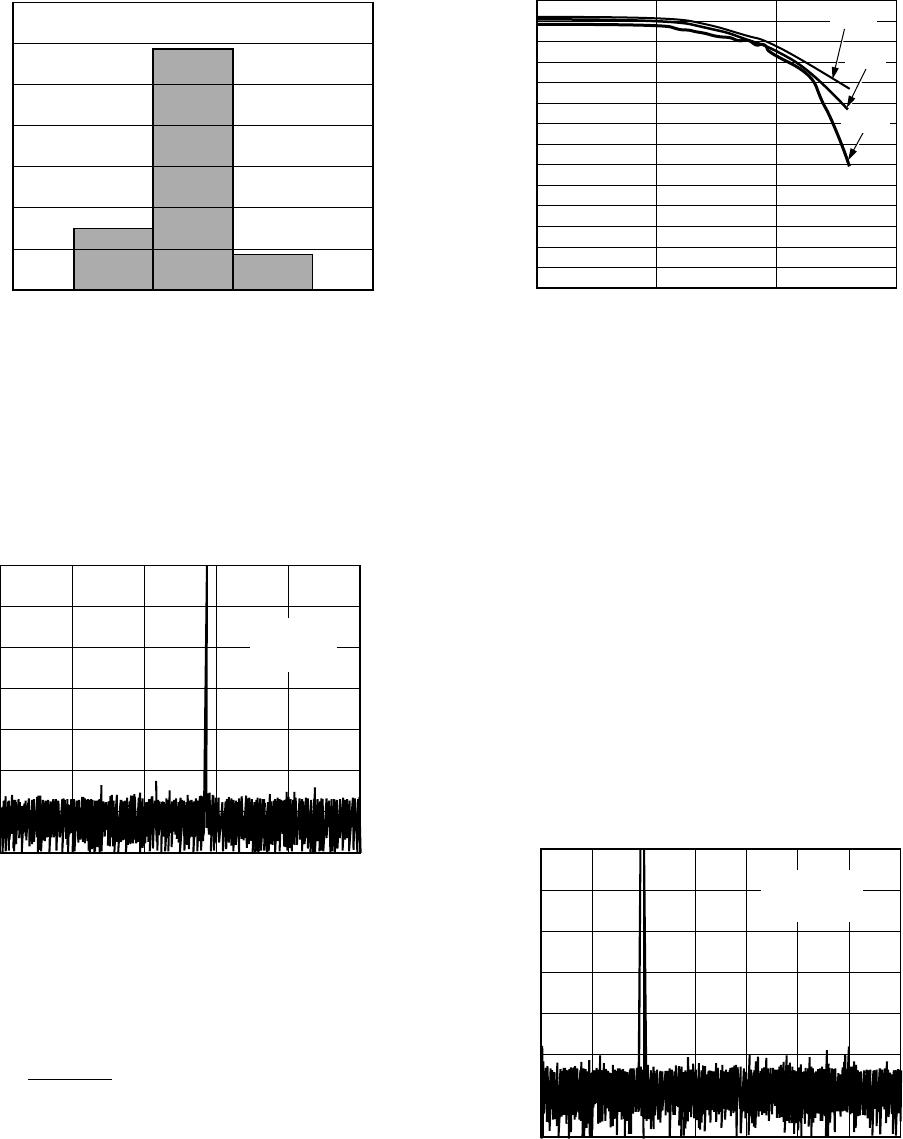

Figure 13 shows a typical circuit that can be used to adjust the

offset and full-scale errors on the AD7865 (V

1

on the AD7865-1

version is shown for example purposes only). Where adjustment

is required, offset error must be adjusted before full-scale error.

This is achieved by trimming the offset of the op amp driving

the analog input of the AD7865 while the input voltage is

1/2 LSB below analog ground. The trim procedure is as follows:

apply a voltage of –610 µV (–1/2 LSB) at V

1

and adjust the op

amp offset voltage until the ADC output code flickers between

1111 1111 1111 and 0000 0000 0000.

Gain error can be adjusted at either the first code transition

(ADC negative full scale) or the last code transition (ADC posi-

tive full scale). The trim procedures for both cases are as follows.

V

1

R1

10k

R2

500

R3

10k

AGND

AD7865*

*ADDITIONAL PINS OMITTED FOR CLARITY

INPUT

RANGE = 10V

R5

10k

V

INxA

R4

10k

Figure 13. Full-Scale Adjust Circuit

Positive Full-Scale Adjust

Apply a voltage of 9.9982 V (FS/2 – 3/2 LSB) at V

1

. Adjust R2

until the ADC output code flickers between 01 1111 1111 1110

and 01 1111 1111 1111.

Negative Full-Scale Adjust

Apply a voltage of –9.9998 V (–FS + 1/2 LSB) at V

1

and adjust

R2 until the ADC output code flickers between 10 0000 0000

0000 and 10 0000 0000 0001.

An alternative scheme for adjusting full-scale error in systems

that use an external reference is to adjust the voltage at the V

REF

pin until the full-scale error for any of the channels is adjusted

out. The good full-scale matching of the channels will ensure

small full-scale errors on the other channels.

DYNAMIC SPECIFICATIONS

The AD7865 is specified and 100% tested for dynamic perfor-

mance specifications as well as traditional dc specifications such

as Integral and Differential Nonlinearity. These ac specifications

are required for such signal processing applications as phased array

sonar, adaptive filters and spectrum analysis. These applications

require information on the ADC’s effect on the spectral content

of the input signal. Hence, the parameters for which the AD7865

is specified include SNR, harmonic distortion, intermodulation

distortion and peak harmonics. These terms are discussed in

more detail in the following sections.

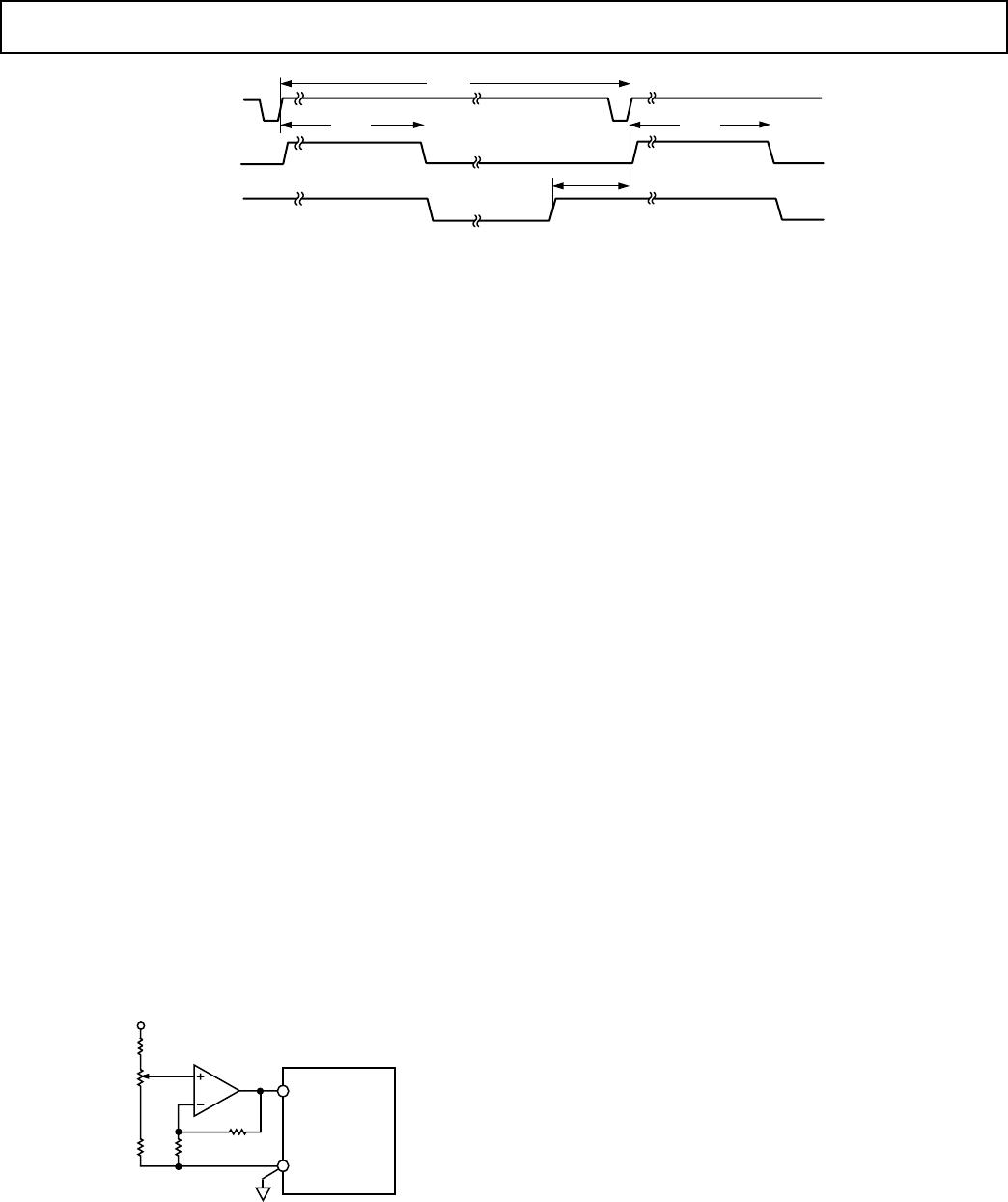

Signal-to-Noise Ratio (SNR)

SNR is the measured signal-to-noise ratio at the output of the

ADC. The signal is the rms magnitude of the fundamental.

Noise is the rms sum of all the nonfundamental signals up to

half the sampling frequency (f

S

/2) excluding dc. SNR is depen-

dent upon the number of quantization levels used in the digitization

process; the more levels, the smaller the quantization noise. The

theoretical signal to noise ratio for a sine wave input is given by

SNR = (6.02N + 1.76) dB (1)

where N is the number of bits.

Thus for an ideal 14-bit converter, SNR = 86.04 dB.

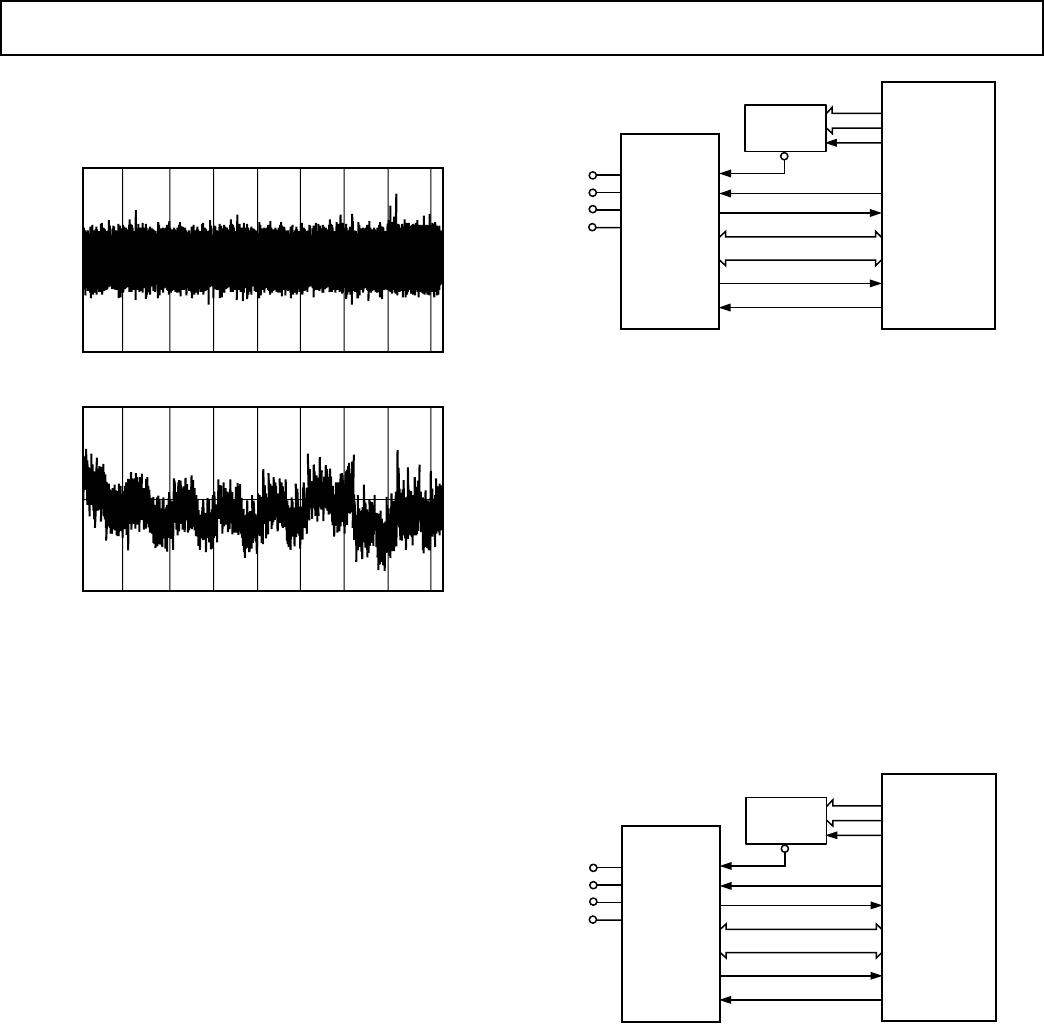

Figure 14 shows a histogram plot for 8192 conversions of a dc

input using the AD7865 with 5 V supply. The analog input was

set at the center of a code transition. It can be seen that most of

the codes appear in the one output bin, indicating very good

noise performance from the ADC.

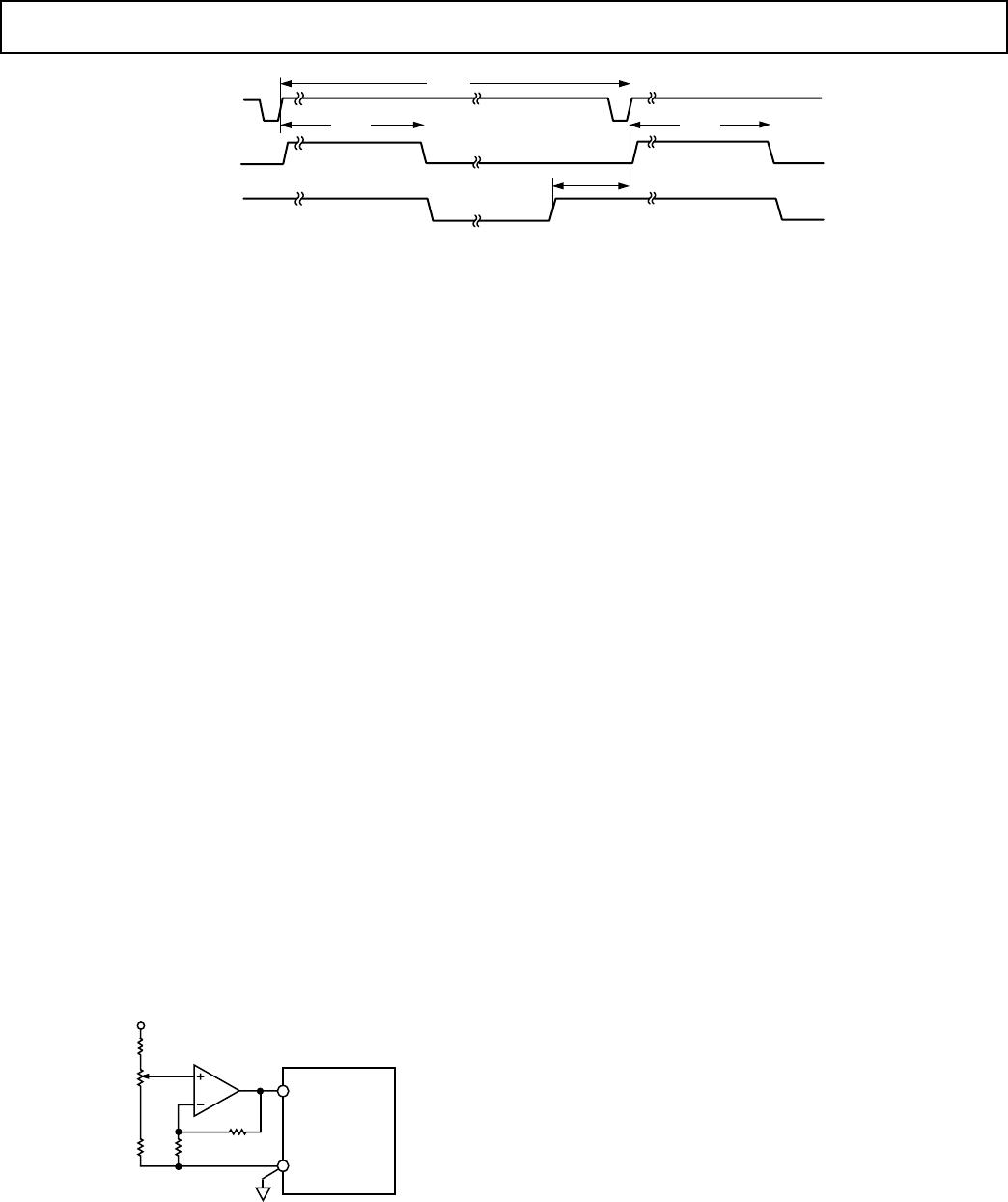

CONVST

BUSY

STBY

100s

I

DD

= 3A

t

BUSY

t

WAKEUP

t

BUSY

7s

Figure 12. Power-Down between Conversion Sequences