PCA9555 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

Product data sheet Rev. 10 — 8 November 2017 5 of 34

NXP Semiconductors

PCA9555

16-bit I

2

C-bus and SMBus I/O port with interrupt

5.2 Pin description

[1] HVQFN and HWQFN package die supply ground is connected to both the V

SS

pin and the exposed center

pad. The V

SS

pin must be connected to supply ground for proper device operation. For enhanced thermal,

electrical, and board-level performance, the exposed pad needs to be soldered to the board using a

corresponding thermal pad on the board, and for proper heat conduction through the board thermal vias

need to be incorporated in the PCB in the thermal pad region.

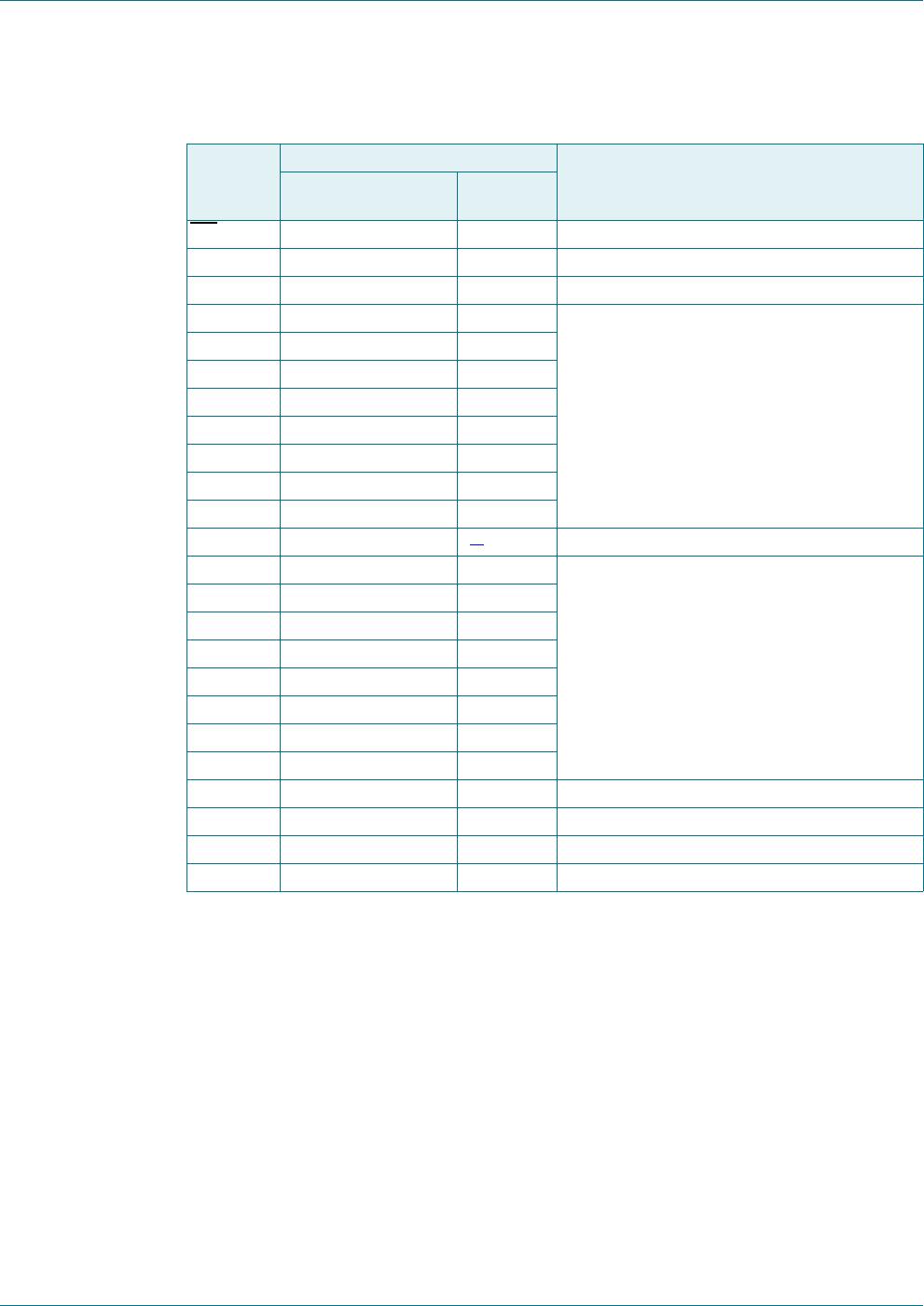

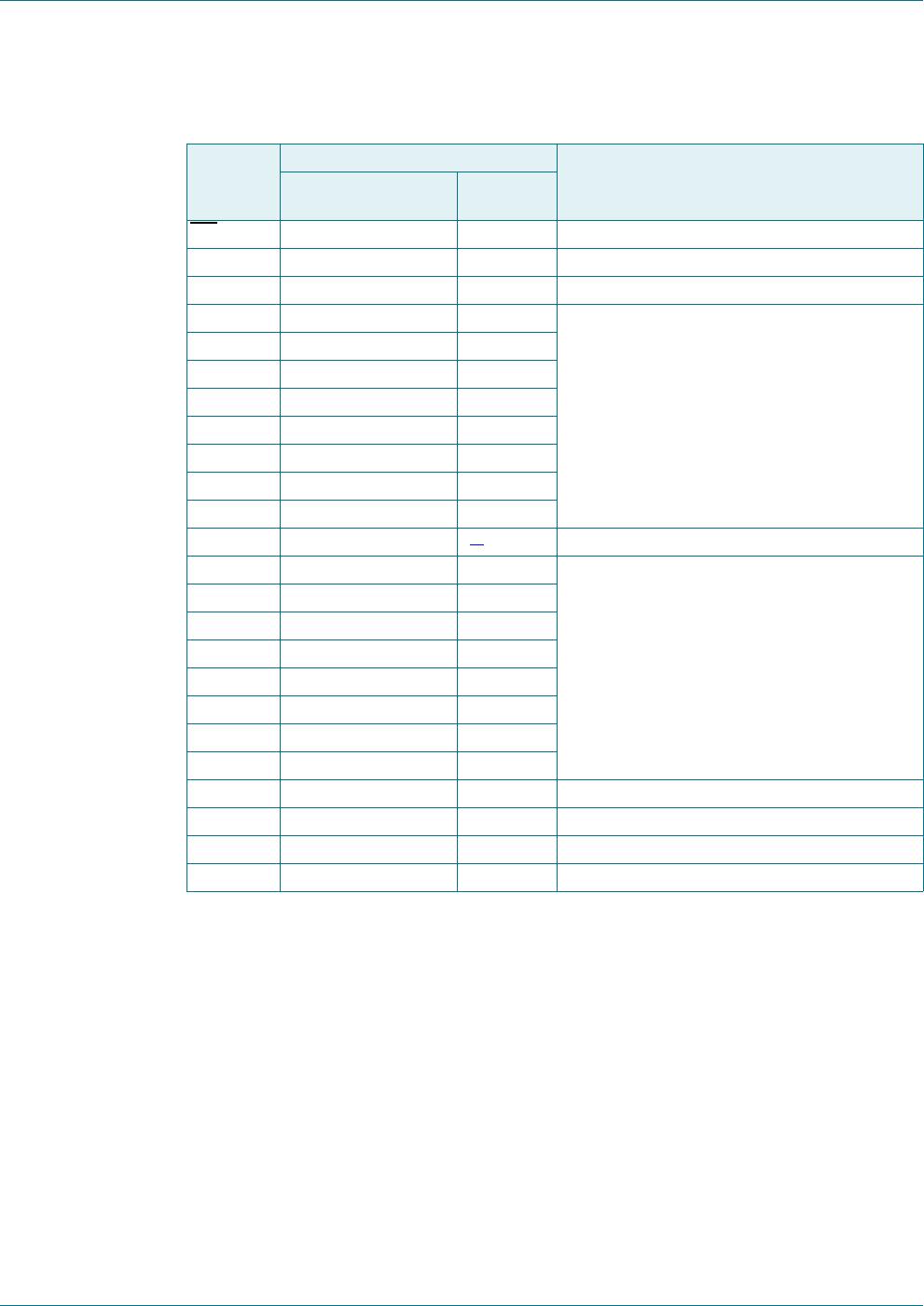

Table 3. Pin description

Symbol Pin Description

SO24, SSOP24,

TSSOP24

HVQFN24,

HWQFN24

INT

1 22 interrupt output (open-drain)

A1 2 23 address input 1

A2 3 24 address input 2

IO0_0 4 1 port 0 input/output

IO0_1 5 2

IO0_2 6 3

IO0_3 7 4

IO0_4 8 5

IO0_5 9 6

IO0_6 10 7

IO0_7 11 8

V

SS

12 9

[1]

supply ground

IO1_0 13 10 port 1 input/output

IO1_1 14 11

IO1_2 15 12

IO1_3 16 13

IO1_4 17 14

IO1_5 18 15

IO1_6 19 16

IO1_7 20 17

A0 21 18 address input 0

SCL 22 19 serial clock line

SDA 23 20 serial data line

V

DD

24 21 supply voltage