CS5521/22/23/24/28

10 DS317F8

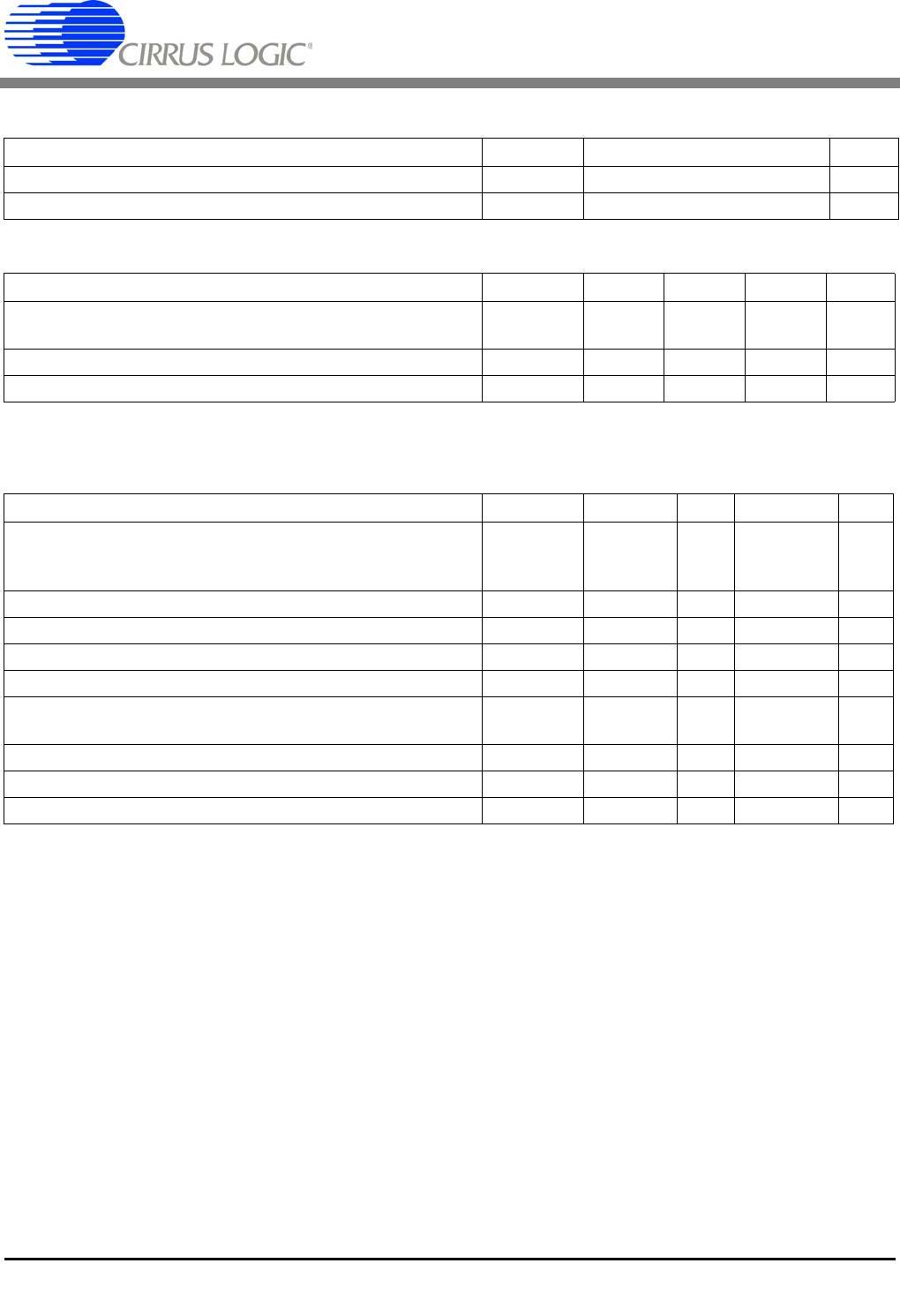

DYNAMIC CHARACTERISTICS

RECOMMENDED OPERATING CONDITIONS

(AGND, DGND = 0 V; See Note 20.)

Notes: 20. All voltages with respect to ground.

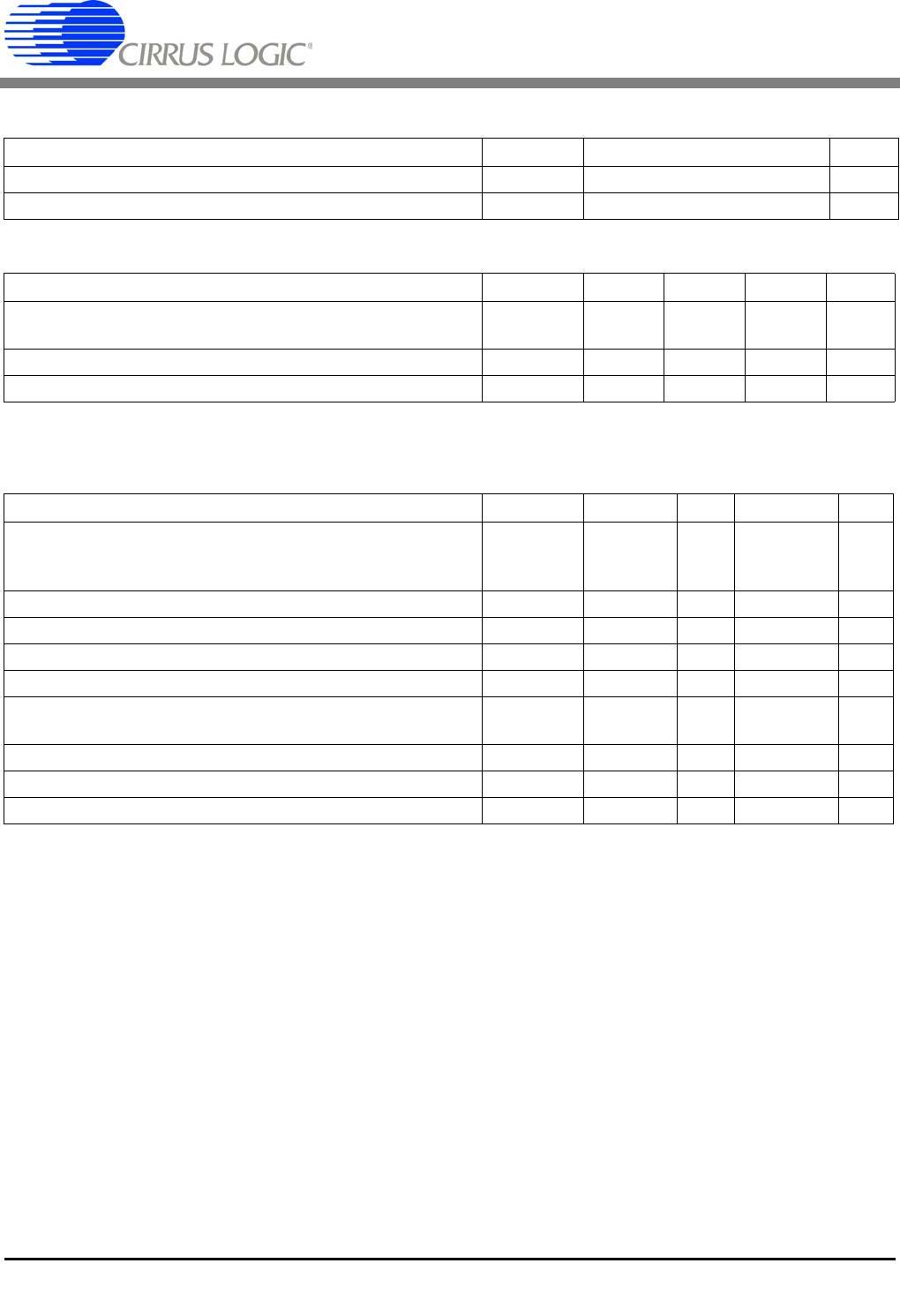

ABSOLUTE MAXIMUM RATINGS (AGND, DGND = 0 V; See Note 20.)

Notes: 21. No pin should go more negative than NBV - 0.3 V.

22. Applies to all pins including continuous overvoltage conditions at the analog input (AIN) pins.

23. Transient current of up to 100 mA will not cause SCR latch-up. Maximum input current for a power

supply pin is ±50 mA.

24. Total power dissipation, including all input currents and output currents.

WARNING: Operation at or beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

Parameter Symbol Ratio Unit

Modulator Sampling Frequency f

s

XIN/4 Hz

Filter Settling Time to 1/2 LSB (Full-scale Step) t

s

1/f

out

s

Parameter Symbol Min Typ Max Unit

DC Power Supplies Positive Digital

Positive Analog

VD+

VA+

2.7

4.75

5.0

5.0

5.25

5.25

V

V

Analog Reference Voltage (VREF+) - (VREF-) VRef

diff

1.0 2.5 VA+ V

Negative Bias Voltage NBV -1.8 -2.1 -2.5 V

Parameter Symbol Min Typ Max Unit

DC Power Supplies (Note 21)

Positive Digital

Positive Analog

VD+

VA+

-0.3

-0.3

-

-

+6.0

+6.0

V

V

Negative Bias Voltage Negative Potential NBV +0.3 -2.1 -3.0 V

Input Current, Any Pin Except Supplies (Note 22 and 23) I

IN

--±10mA

Output Current I

OUT

--±25mA

Power Dissipation (Note 24) PDN - - 500 mW

Analog Input Voltage VREF pins

AIN Pins

V

INR

V

INA

NBV -0.3

NBV -0.3

-

-

(VA+) + 0.3

(VA+) + 0.3

V

V

Digital Input Voltage V

IND

-0.3 - (VD+) + 0.3 V

Ambient Operating Temperature T

A

-40 - 85 °C

Storage Temperature T

stg

-65 - 150 °C