CS5521/22/23/24/28

DS317F8 33

perform a system gain calibration. In either case,

the calibration signals must be within the specified

calibration limits for each specific calibration step

(refer to the ‘System Calibration Specifications’ in

ANALOG CHARACTERISTICS). If a system gain

calibration is performed the following conditions

must be met:

1) Full-scale input must not saturate the 20X in-

strumentation amplifier, if the calibration is on

an input range where the instrumentation am-

plifier is involved.

2) The 1’s density of the modulator must not be

greater than 80 percent (the input to the ΔΣ

modulator must not exceed the maximum input

which Table 1 specifies).

3) The input must not be so small, relative to the

range chosen, that the resulting gain register’s

content, decoded in decimal, exceeds

3.9999998 (see the discussion of operating lim-

its on input span under the Analog Input and

Limitations in Calibration Range sections).

This requires the full-scale input voltage to the

modulator to be at least 25 percent of the nom-

inal value.

The converter’s input ranges were chosen to guar-

antee gain calibration accuracy to 1 LSB

16

or 16

LSB

24

when system gain calibration is performed.

This is useful when a user wants to manually scale

the full-scale range of the converter and maintain

accuracy. For example, if a gain calibration is per-

formed with a 2.5 V full-scale voltage and a 1.25 V

input range is desired, the user can read the con-

tents of the gain register, shift the register contents

left by 1 bit, and then write the result back to the

gain register. This multiplies the gain by 2.

Assuming a system can provide two known voltag-

es, the following equations allow the user to manu-

ally compute the calibration register’s values based

on two uncalibrated conversions (see note). The

offset and gain calibration registers are used to ad-

just a typical conversion as follows:

Rc = (Ru + Co) * Cg / 2

22

.

Calibration can be performed using the following

equations:

Co = (Rc0/G - Ru0)

Cg = 2

22

* G

where G = (Rc1 - Rc0)/(Ru1-Ru0).

Note: Uncalibrated conversions imply that the gain and off-

set registers are at default {gain register = 0x400000

(Hex) and offset register = 0x000000 (Hex)}.

+

-

X20

+

-

External

Connections

+

-

AIN+

AIN-

CM

+

-

0V

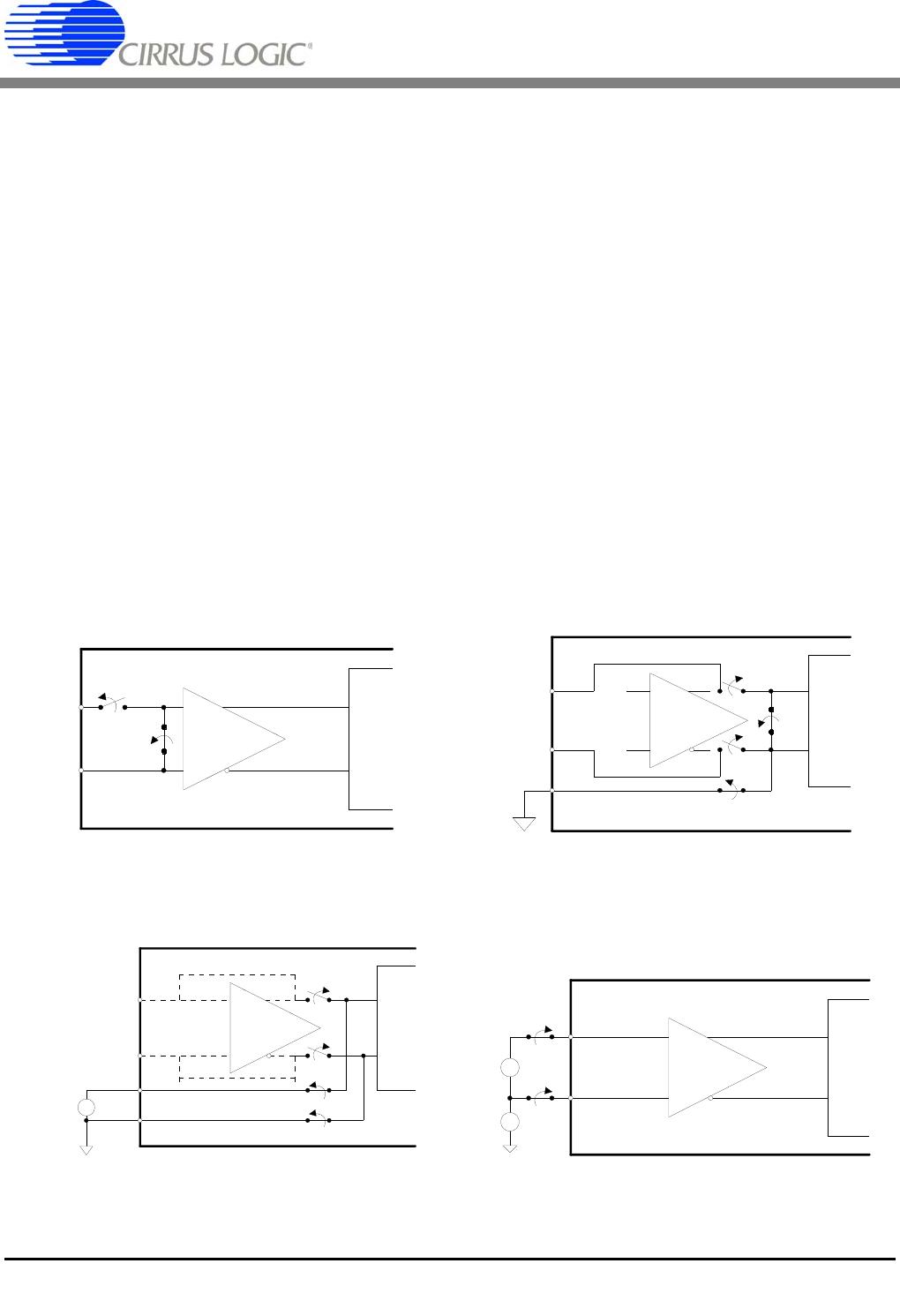

Figure 15. System Calibration of Offset (High Ranges)

+

-

X20

+

-

External

Connections

Full Scale

+

-

AIN+

AIN-

CM

+

-

Figure 16. System Calibration of Gain (Low Ranges)

+

-

X20

+

-

External

Connections

Full Scale

+

-

AIN+

AIN-

CM

+

-

Figure 17. System Calibration of Gain (High Ranges)