CS5521/22/23/24/28

DS317F8 17

mentation amplifier, and providing a number of

flags which indicate converter operation.

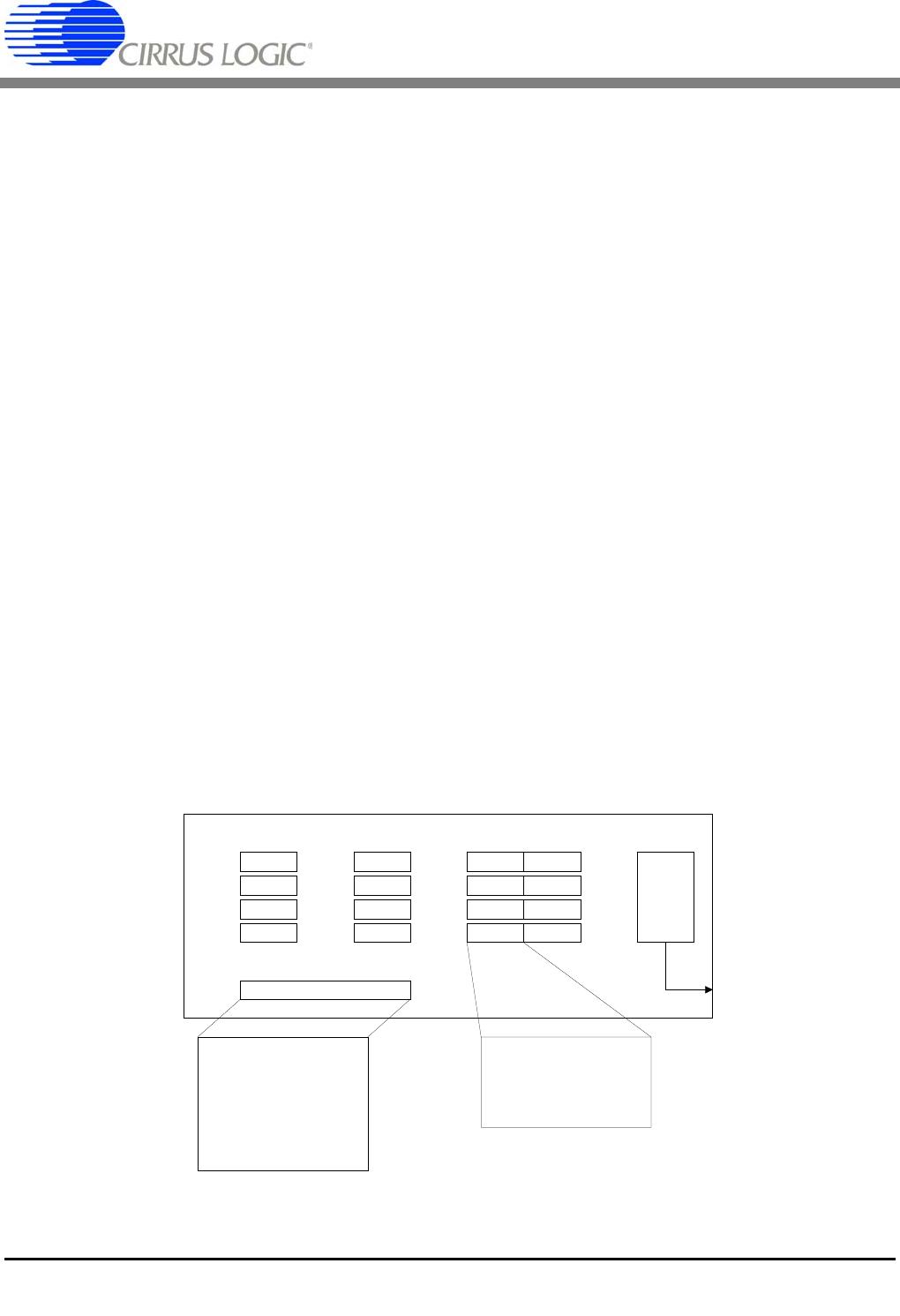

A group of registers, called Channel Set-up Regis-

ters, are also included in the converters. These reg-

isters are used to hold pre-loaded conversion

instructions. Each channel set-up register is 24 bits

wide and holds two 12-bit conversion instructions

(Setups). Upon power-up, these registers can be

initialized by the user’s microcontroller with con-

version instructions. The user can then use bits in

the configuration register to choose a conversion

mode.

Several conversion modes are possible. Using the

single conversion mode, an 8-bit command word

can be written into the serial port. The command in-

cludes pointer bits which ‘point’ to a 12-bit com-

mand in one of the Channel Setup Registers which

is to be executed. The 12-bit commands can be set-

up to perform a conversion on any of the input

channels of the converter. More than one of the 12-

bit Setups can be used for the same analog input

channel. This allows the user to convert on the

same signal with either a different conversion

speed, a different gain range, or any of the other op-

tions available in the Setup Register. The user can

set up the registers to perform conversions using

different conversion options on each of the input

channels.

The ADCs also include multiple-channel conver-

sion capability. User bits in the configuration regis-

ter of the ADCs can be configured to sequence

through the 12-bit command Setups, performing a

conversion according to the content of each 12-bit

Setup. This channel scanning capability can be

configured to run continuously, or to scan through

a specified number of Setup Registers and stop un-

til commanded to continue. In the multiple-channel

scanning modes, the conversion data words are

loaded into an on-chip data FIFO. The converter is-

sues a flag on the SDO pin when a scan cycle is

completed so the user can read the FIFO. More de-

tails are given in the following pages.

Instructions are provided on how to initialize the

converter, perform offset and gain calibrations, and

to configure the converter for the various conver-

sion modes. Each of the bits of the configuration

register and of the Channel Setup Registers is de-

scribed. A list of examples follows the description

section. Table 2 can be used to decode all valid

commands (the first 8 bits into the serial port).

AIN1

AIN2

AIN3

AIN4

4 (24) 4 (24) 4 (12 x 2) 8 x 24

Off 1

Off 2

Off 3

Off 4

Gain 1

Gain 2

Gain 3

Gain 4

Setup 1

Setup 3

Setup 5

Setup 7

Setup 2

Setup 4

Setup 6

Setup 8

DATA

FIFO

SDO

1 x 24

Configuration

Chop Frequency

Multiple Conversions

Depth Pointer

Loop

Read Convert

Powerdown Modes

Flags

Etc.

Latch Outputs

Channel Select

Output Word Rate

PGA Selection

Unipolar/Bipolar

Figure 9. CS5523/24 Register Diagram