LTC4417

21

4417f

applicaTions inForMaTion

master and connect its highest valid priority channel to

the common output. If seven, or more, input supplies are

prioritized, additional LTC4417s can be added by connect-

ing all individual V

OUT

pins together and connecting each

LTC4417’s CAS to the next lower priority LTC4417’s EN.

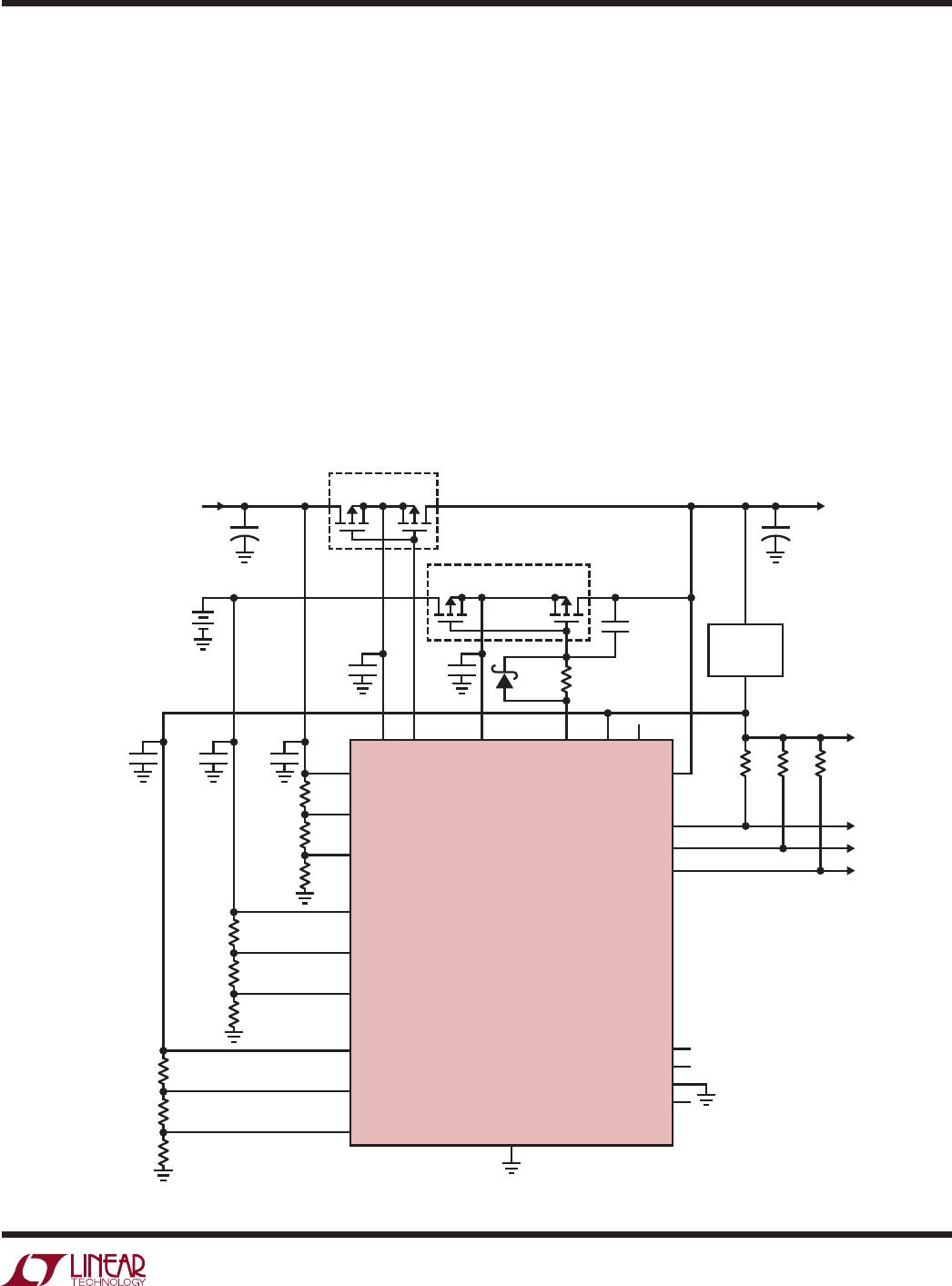

DESIGN EXAMPLE

A 2A multiple input supply system consisting of a 12V

supply with a source resistance of 20mΩ, 7.4V main

lithium-ion battery, and a backup 7.4V lithium-ion battery

is designed with priority sourcing from the 12V supply,

as shown in Figure 13. Power is sourced from the main

battery when the 12V supply is absent and the backup

battery is only used when the main battery and 12V supply

are not available. The ambient conditions of the system

will be between 25°C and 85°C.

The design limits the output voltage droop to 800mV

during switchover. The load capacitor is assumed to have

a minimum ESR of 50mΩ at 85°C and 80mΩ at 25°C

through paralleling low ESR rated aluminum electrolytic

capacitors. The input source is allowed to drop 1V.

Selecting External P-Channel MOSFET

The design starts with selecting a suitable 2A rated

P-channel MOSFET with desired

R

DS(ON)

. Reviewing several

MOSFET options, the low 18mΩ R

DS(ON)

, dual P-channel

IRF7324 with a –20V BV

DSS

, is chosen for this application.

The low 18mΩ R

DS(ON)

results in a 72mV combined drop

at 25°C and 85mV drop at 85°C. Each P-channel MOSFET

dissipates 72mW at 25°C and 85mW at 85°C.

Inrush Current Limiting

When connecting a higher voltage source to a lower voltage

output, significant inrush current can occur. The magnitude

of the inrush current can be calculated with Equation (19).

I

INRUSH

=

V1– V

OUT(INIT)

R

SRC

+ESR(C

L

)+ 2 •R

DS(ON)

(19)

where V

OUT(INIT)

is the V

OUT

voltage when initially powered

from a supply voltage less than V1, V1 is the higher voltage

source, R

SRC

is source resistance of V1, ESR(C

L

) is the

ESR of the load capacitor, and R

DS(ON)

is the on-resistance

of the external back-to-back MOSFET.

Given a total series resistance from input to output, the

worst case inrush current will occur when V1 is running

20% high, at 14.4V, and V

OUT

is at its undervoltage limit

of 5.6V. During this condition, a maximum inrush current

of 83A will occur, as shown in Equation (20).

I

INRUSH

=

14.4V – 5.6V

20mΩ+ 50mΩ+36mΩ

= 83A

(20)

Because the 83A of inrush current exceeds the 71A ab-

solute maximum pulsed drain current rating, I

DM

, of the

IRF7324, inrush current limiting is required.

Calculating the load capacitance, C

L

, and inrush current

limiting circuitry component, R

S

, is an iterative process.

To start, use Equation (14), with 0.79 • R

S

• C

S

initially set

to 10µs. To limit the output voltage droop to the desired

800mV, reserve 200mV for initial droop due to the load

current flowing in the ESR of the output capacitor. Next,

choose C

L

to set the maximum V

OUT

droop to 600mV, as

shown in Equation (21).

C

L

=

2A •(3µs+12µs+10µs)

600mV

C

L

= 83.3µF

(21)

For margin, choose the initial C

L

value equal to 100µF and

use Equation (16) to determine R

S

. With an allowable 1V

input voltage drop and source resistance, R

SRC

, of 20mΩ,

the input voltage droop of 700mV is used to set the inrush

current of 35A. The other terms in the equation come

from the external P-channel MOSFET manufacturer’s data

sheet. The transfer characteristics curve shows the gate

voltage, V

GS

, is approximately 1.8V when driving the 35A

inrush current and the capacitance verses drain-to-source

voltage curve shows the maximum C

RSS

is approximately

600pF. C

S

is set to be greater than ten times C

RSS

, or

6.8nF. To ensure the designed inrush current is lower

than the absolute maximum pulse drain current rating,

I

DM

, calculate R

S

using the maximum value for ∆V

G(SINK)

and C

L

, and the minimum value for C

S

. For aluminum