AD7859/AD7859L

REV. A

–14–

and 1.5 CLKIN periods are allowed for the acquisition time.

With a 1.8 MHz clock, this gives a full cycle time of 10 µs,

which equates to a throughput rate of 100 kSPS.

When using the software conversion start for maximum

throughput, the user must ensure the control register write op-

eration extends beyond the falling edge of BUSY. The falling

edge of BUSY resets the

CONVST bit to 0 and allows it to be

reprogrammed to 1 to start the next conversion.

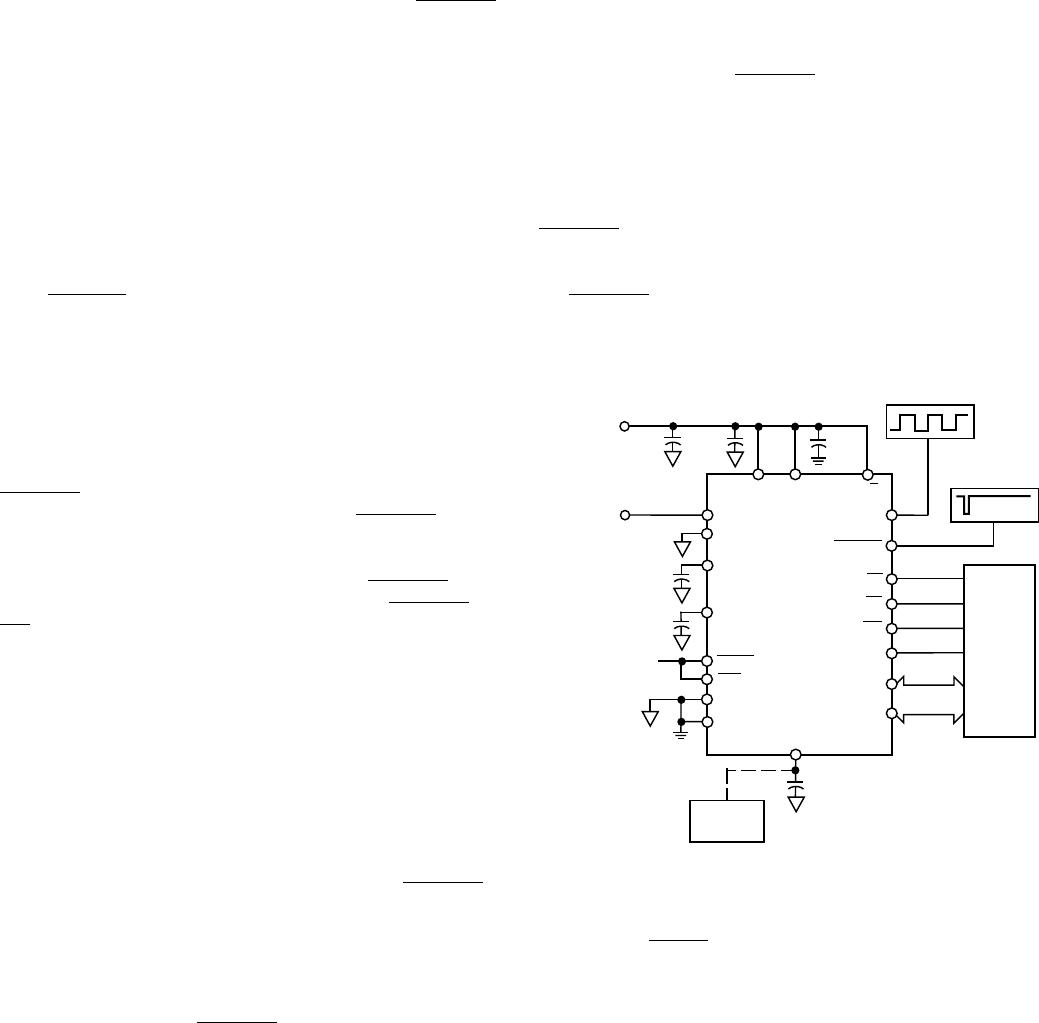

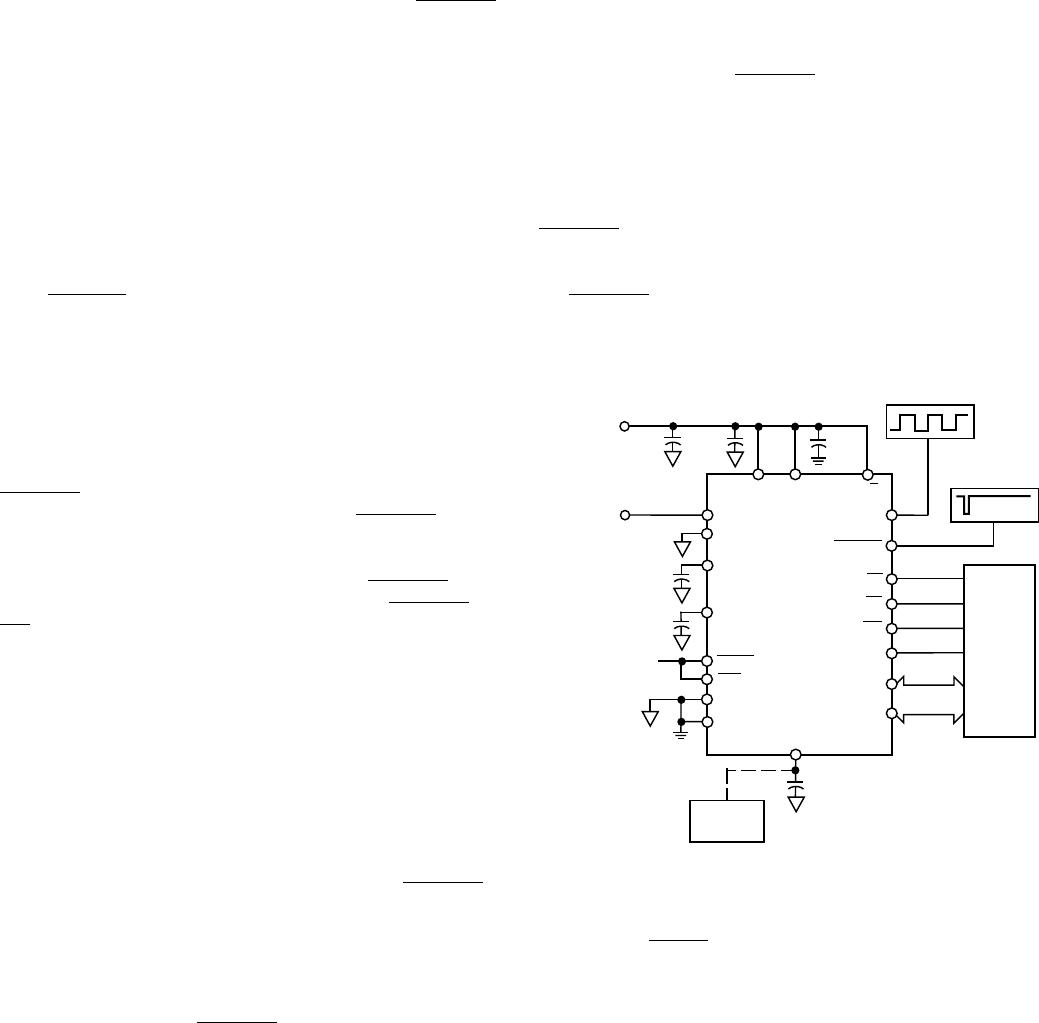

TYPICAL CONNECTION DIAGRAM

Figure 8 shows a typical connection diagram for the AD7859/

AD7859L. The AGND and the DGND pins are connected

together at the device for good noise suppression. The first

CONVST applied after power-up starts a self-calibration

sequence. This is explained in the calibration section of this data

sheet. Note that after power is applied to AV

DD

and DV

DD

and

the

CONVST signal is applied, the part requires (70 ms + 1/

sample rate) for the internal reference to settle and for the self-

calibration on power-up to be completed.

AV

DD

DV

DD

AIN(+)

AIN(–)

C

REF1

C

REF2

SLEEP

DB15

DB0

CONVST

AGND

DGND

CLKIN

REF

IN

/REF

OUT

AD7859/

AD7859L

ANALOG

SUPPLY

+3V TO +5V

0.1µF

0.1µF10µF

0.1µF

0.01µF

CONVERSION

START SIGNAL

0.1nF EXTERNAL REF

0.1µF INTERNAL REF

CAL

0V TO 2.5V

INPUT

4MHz/1.8MHz

OSCILLATOR

OPTIONAL

EXTERNAL

REFERENCE

CS

RD

WR

W/B

BUSY

DV

DD

µC/µP

AD780/

REF192

Figure 8. Typical Circuit

For applications where power consumption is a major concern,

the power-down options can be exercised by writing to the part

and using the

SLEEP pin. See the Power-Down section for more

details on low power applications.

CIRCUIT INFORMATION

The AD7859/AD7859L is a fast, 8-channel, 12-bit, single sup-

ply A/D converter. The part requires an external 4 MHz/1.8

MHz master clock (CLKIN), two C

REF

capacitors, a CONVST

signal to start conversion and power supply decoupling capaci-

tors. The part provides the user with track/hold, on-chip refer-

ence, calibration features, A/D converter and parallel interface

logic functions on a single chip. The A/D converter section of

the AD7859/AD7859L consists of a conventional successive-ap-

proximation converter based around a capacitor DAC. The

AD7859/AD7859L accepts an analog input range of 0 to +V

REF.

V

REF

can be tied to V

DD

. The reference input to the part con-

nected via a 150 kΩ resistor to the internal 2.5 V reference and

to the on-chip buffer.

A major advantage of the AD7859/AD7859L is that a conver-

sion can be initiated in software, as well as by applying a signal

to the

CONVST pin. The part is available in a 44-pin PLCC or a

44-pin PQFP package, and this offers the user considerable

spacing saving advantages over alternative solutions. The

AD7859L version typically consumes only 5.5 mW making it

ideal for battery-powered applications.

CONVERTER DETAILS

The master clock for the part is applied to the CLKIN pin.

Conversion is initiated on the AD7859/AD7859L by pulsing the

CONVST input or by writing to the control register and setting

the CONVST bit to 1. On the rising edge of

CONVST (or at

the end of the control register write operation), the on-chip

track/hold goes from track to hold mode. The falling edge of the

CLKIN signal which follows the rising edge of

CONVST ini-

tiates the conversion, provided the rising edge of

CONVST (or

WR when converting via the control register) occurs typically at

least 10 ns before this CLKIN edge. The conversion takes 16.5

CLKIN periods from this CLKIN falling edge. If the 10 ns set-

up time is not met, the conversion takes 17.5 CLKIN periods.

The time required by the AD7859/AD7859L to acquire a signal

depends upon the source resistance connected to the AIN(+) in-

put. Please refer to the acquisition time section for more details.

When a conversion is completed, the BUSY output goes low,

and the result of the conversion can be read by accessing the

data through the data bus. To obtain optimum performance

from the part, read or write operations should not occur during

the conversion or less than 200 ns prior to the next

CONVST

rising edge. Reading/writing during conversion typically de-

grades the Signal-to-(Noise + Distortion) by less than 0.5 dBs.

The AD7859 can operate at throughput rates of over 200 kSPS

(up to 100 kSPS for the AD7859L).

With the AD7859L, 100 kSPS throughput can be obtained as

follows: the CLKIN and

CONVST signals are arranged to give

a conversion time of 16.5 CLKIN periods as described above