BELASIGNA 250

http://onsemi.com

7

Mechanical Information and Circuit Design Guidelines

Mechanical Information

BELASIGNA 250 is available in two packages in

production quantities:

• A 7 x 7 mm LFBGA package where all the device I/Os

are available at the BGA level

• A 5 x 5 mm CABGA package

BELASIGNA 250 also exists in a PLCC package, but it

is only used on the evaluation and development board. The

PLCC package is not available in production quantities. A

separate data sheet is available for this part (part number

0W548−001−XTD). Contact ON Semiconductor for more

information on this package option.

All BELASIGNA 250 package options are Green

(RoHS− compliant). Contact ON Semiconductor for

supporting documentation.

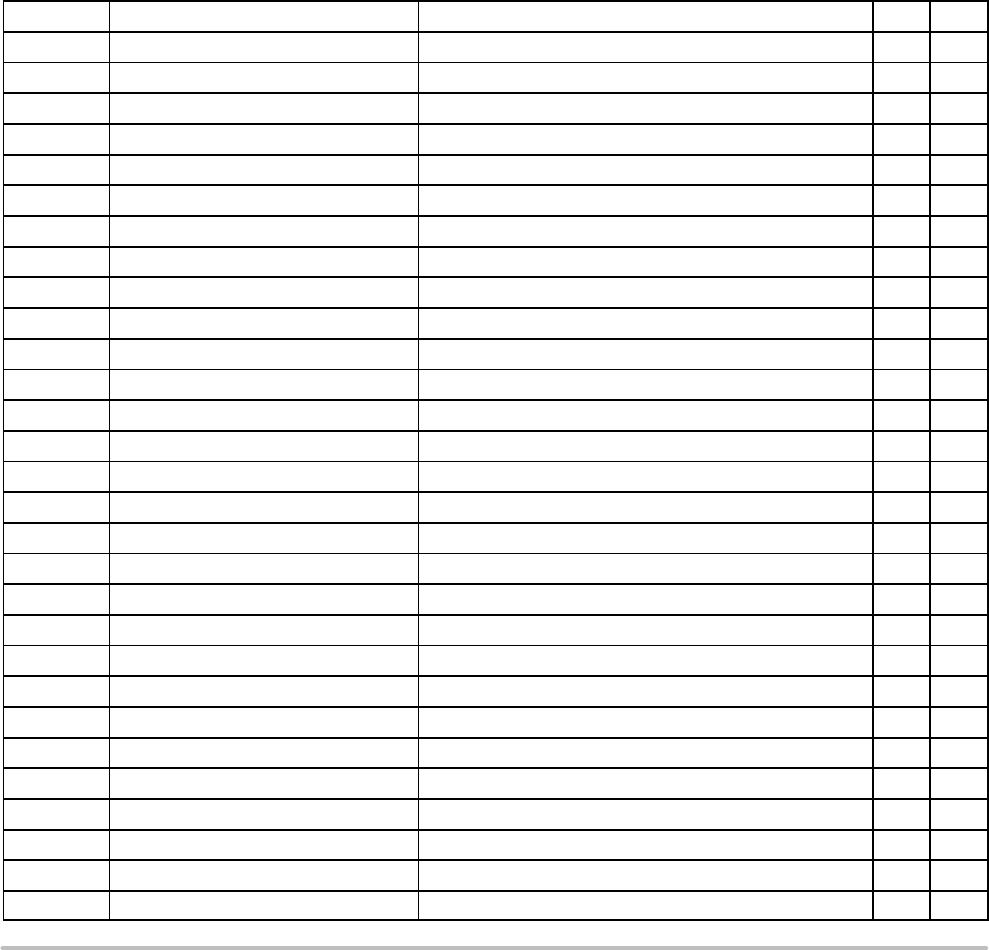

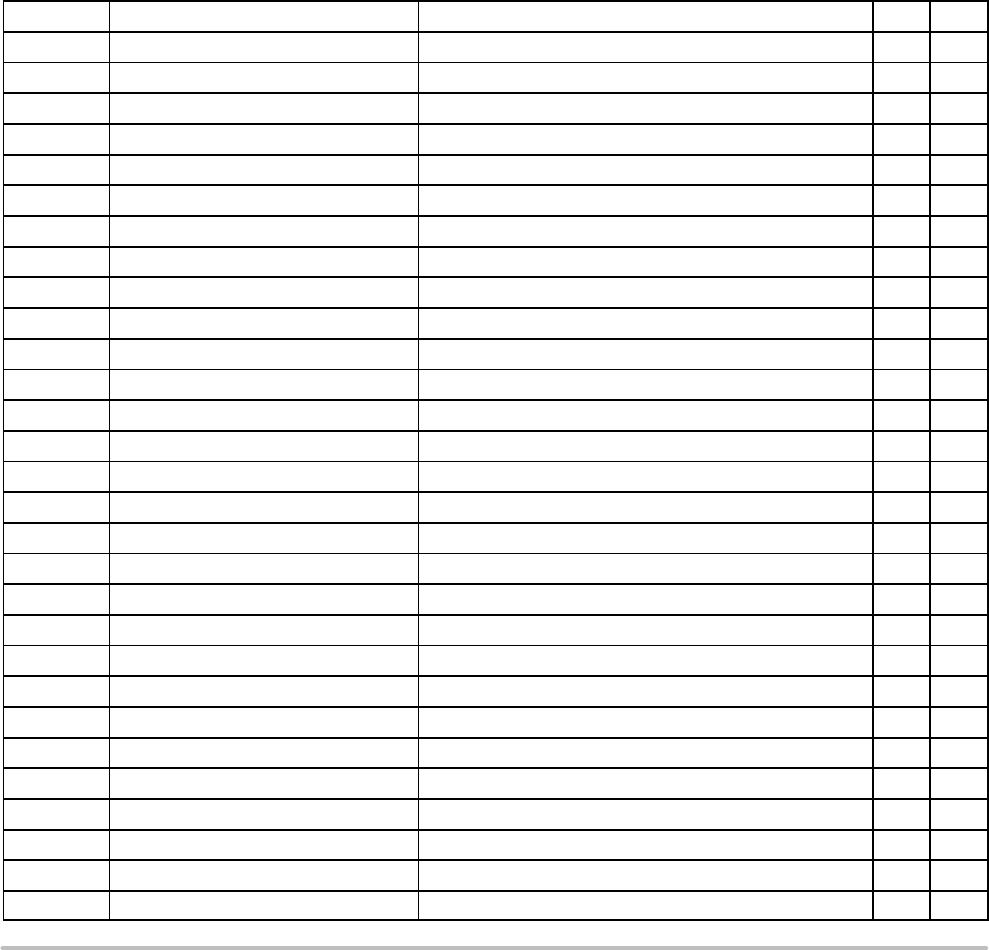

A total of 51 active pins are present on the BELASIGNA 250 7 x 7 mm LFBGA package option. This package contains a

total of 64 balls, organized in an 8−by−8 array. A description of these pins is given in Table 3.

Table 3. LFBGA PIN DESCRIPTIONS

Pad Index BELASIGNA 250 Pin Name Description I/O A/D

F2 VBAT Power supply I A

B3, E2 AGND Analog ground N/A A

E4 RCVRBAT Digital output power supply I A

H4 RCVRGND Digital output ground N/A A

D6 VDDC Digital core power supply O D

F7 GNDC Digital core ground N/A D

H6, C5 VDDO Digital pads power supply I D

A6, F6 GNDO Digital pads ground N/A D

E1 VREG Microphone power supply O A

A1 VDBL Doubled voltage output O A

B2 CAP0 Charge pump capacitor connection N/A A

A2 CAP1 Charge pump capacitor connection N/A A

B1 AI0 Microphone input I A

C1 AI1/LOUT Microphone input / direct audio input I A

C2 AI2 Microphone input I A

D1 AI3 Microphone input I A

F1 AI_RC Remote control input I A

D3 AIR Audio input reference N/A A

G3 RCVR0+ Digital output 0 positive output O A

H3 RCVR0− Digital output 0 negative output O A

H2 AO0/RCVR1+ Analog output 0 / digital output 1 positive output O A

H1 AO1/RCVR1− Analog output 1 / digital output 1 negative output O A

F3 AOR Analog output reference N/A A

H8 DEBUG_RX RS−232 serial input I D

G8 DEBUG_TX RS−232 serial output O D

H7 EXT_CLK External clock input / output I/O D

C3 SPI_CLK SPI clock O D

A3 SPI_CS SPI chip select O D

B4 SPI_SERO SPI serial output O D