Si4734/35-C40

12 Rev. 1.0

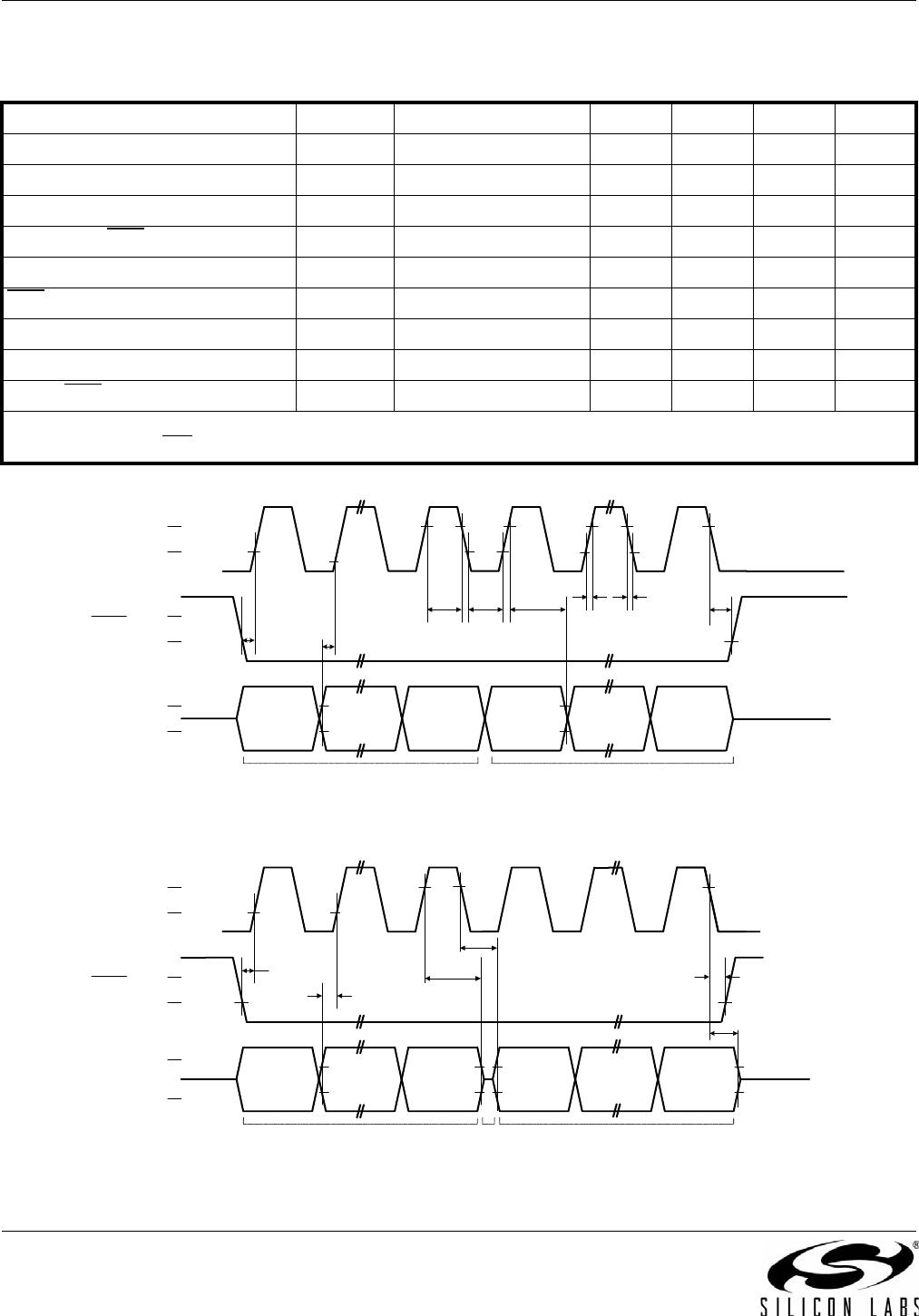

Table 9. FM Receiver Characteristics

1,2

(V

DD

= 2.7 to 5.5 V, V

IO

= 1.85 to 3.6 V, T

A

= –20 to 85 °C)

Parameter Symbol Test Condition Min Typ Max Unit

Input Frequency f

RF

76 — 108 MHz

Sensitivity with Headphone

Network

3,4,5

(S+N)/N = 26 dB — 2.2 3.5 µV EMF

Sensitivity with 50 Network

3,4,5,6

(S+N)/N = 26 dB — 1.1 — µV EMF

RDS Sensitivity

6

f = 2 kHz,

RDS BLER < 5%

—15—µV EMF

LNA Input Resistance

6,7

345k

LNA Input Capacitance

6,7

456pF

Input IP3

6,8

100 105 — dBµV EMF

AM Suppression

3,4,6,7

m = 0.3 40 50 — dB

Adjacent Channel Selectivity

±200 kHz 35 50 — dB

Alternate Channel Selectivity

±400 kHz 60 70 — dB

Spurious Response Rejection

6

In-band 35 — — dB

Audio Output Voltage

3,4,7

72 80 90 mV

RMS

Audio Output L/R Imbalance

3,7,9

—— 1 dB

Audio Frequency Response Low

6

–3 dB — — 30 Hz

Audio Frequency Response High

6

–3 dB 15 — — kHz

Audio Stereo Separation

7,9

32 42 — dB

Audio Mono S/N

3,4,5,7,10

55 63 — dB

Audio Stereo S/N

4,5,6,7,10,11

—58— dB

Audio THD

3,7,9

—0.10.5 %

De-emphasis Time Constant

6

FM_DEEMPHASIS = 2 70 75 80 µs

FM_DEEMPHASIS = 1 45 50 54 µs

Notes:

1. Additional testing information is available in “AN388: Si470x/1x/2x/3x/4x Evaluation Board Test Procedure.”

Volume = maximum for all tests. Tested at RF = 98.1 MHz.

2. To ensure proper operation and receiver performance, follow the guidelines in “AN383: Si47xx Antenna, Schematic,

Layout, and Design Guidelines.” Silicon Laboratories will evaluate schematics and layouts for qualified customers.

3. F

MOD

=1kHz, 75µs de-emphasis, MONO = enabled, and L = R unless noted otherwise.

4. f = 22.5 kHz.

5. B

AF

= 300 Hz to 15 kHz, A-weighted.

6. Guaranteed by characterization.

7. V

EMF

=1 mV.

8. |f

2

– f

1

| > 2 MHz, f

0

=2xf

1

– f

2

. AGC is disabled.

9. f = 75 kHz.

10. At L

OUT

and R

OUT

pins.

11. Analog audio output mode.

12. Blocker Amplitude = 100 dBµV

13. Sensitivity measured at (S+N)/N = 26 dB.

14. At temperature (25°C).