Si4734/35-C40

Rev. 1.0 37

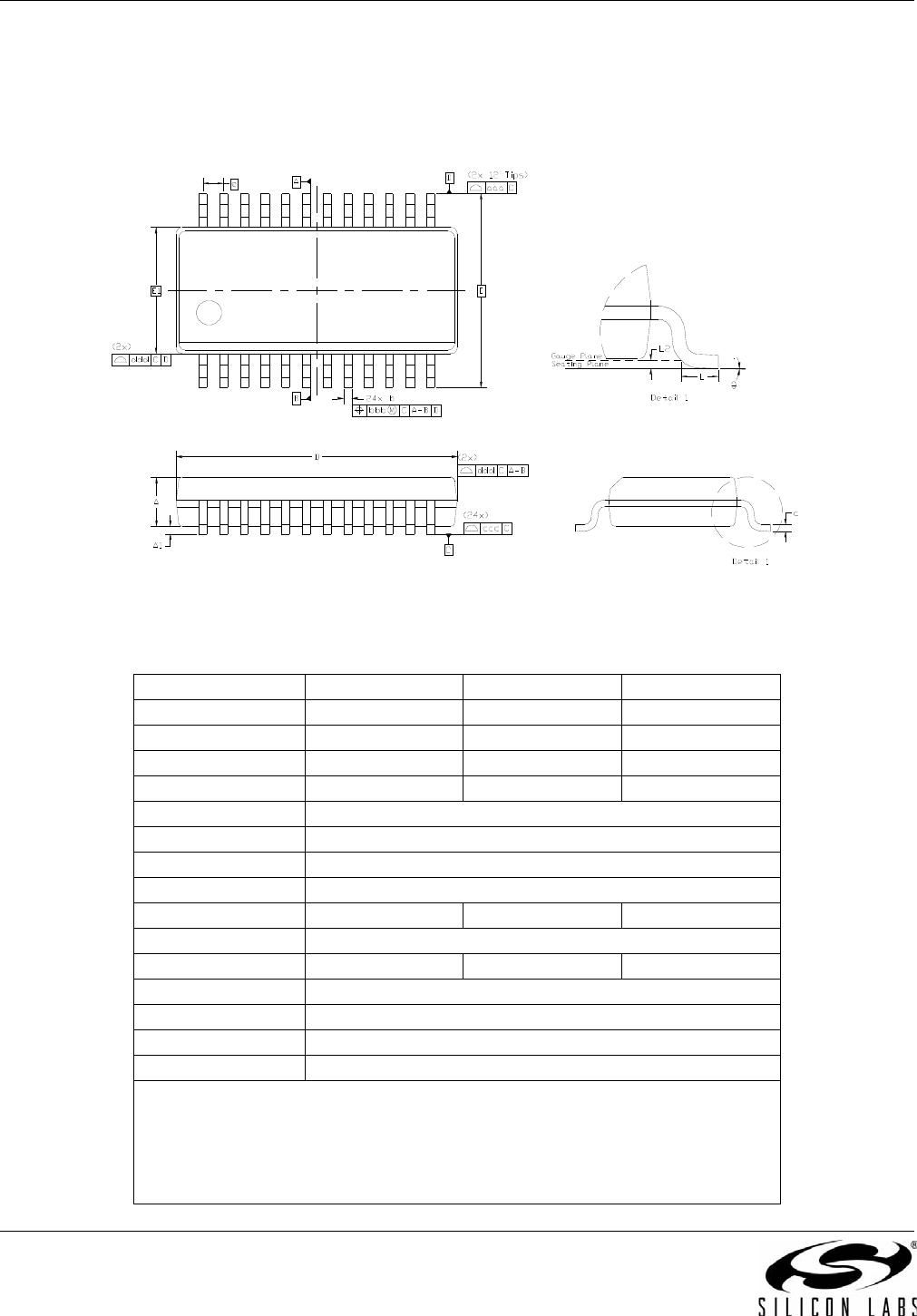

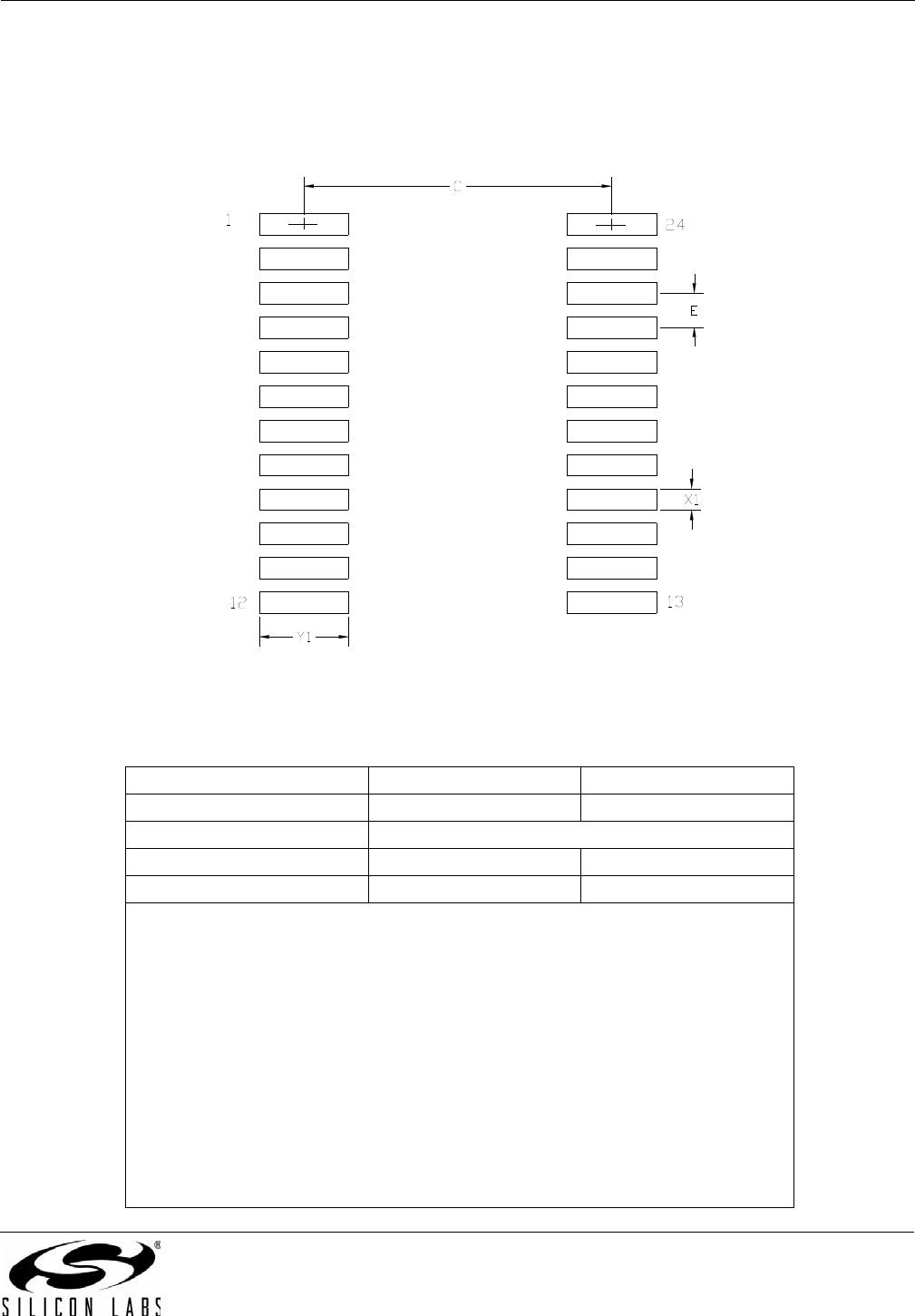

Table 17. PCB Land Pattern Dimensions

Symbol Millimeters Symbol Millimeters

Min Max Min Max

D 2.71 REF GE 2.10 —

D2 1.60 1.80 W — 0.34

e 0.50 BSC X — 0.28

E 2.71 REF Y 0.61 REF

E2 1.60 1.80 ZE — 3.31

f 2.53 BSC ZD — 3.31

GD 2.10 —

Notes: General

1.

All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

3. This Land Pattern Design is based on IPC-SM-782 guidelines.

4. All dimensions shown are at Maximum Material Condition (MMC). Least Material

Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

Notes: Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the

solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

Notes: Stencil Design

1.

A stainless steel, laser-cut, and electro-polished stencil with trapezoidal walls should

be used to assure good solder paste release.

2. The stencil thickness should be 0.125 mm (5 mils).

3. The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

4. A 1.45 x 1.45 mm square aperture should be used for the center pad. This provides

approximately 70% solder paste coverage on the pad, which is optimum to assure

correct component stand-off.

Notes: Card Assembly

1.

A No-Clean, Type-3 solder paste is recommended.

2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification

for Small Body Components.