Data Sheet ADV202

Rev. D | Page 9 of 40

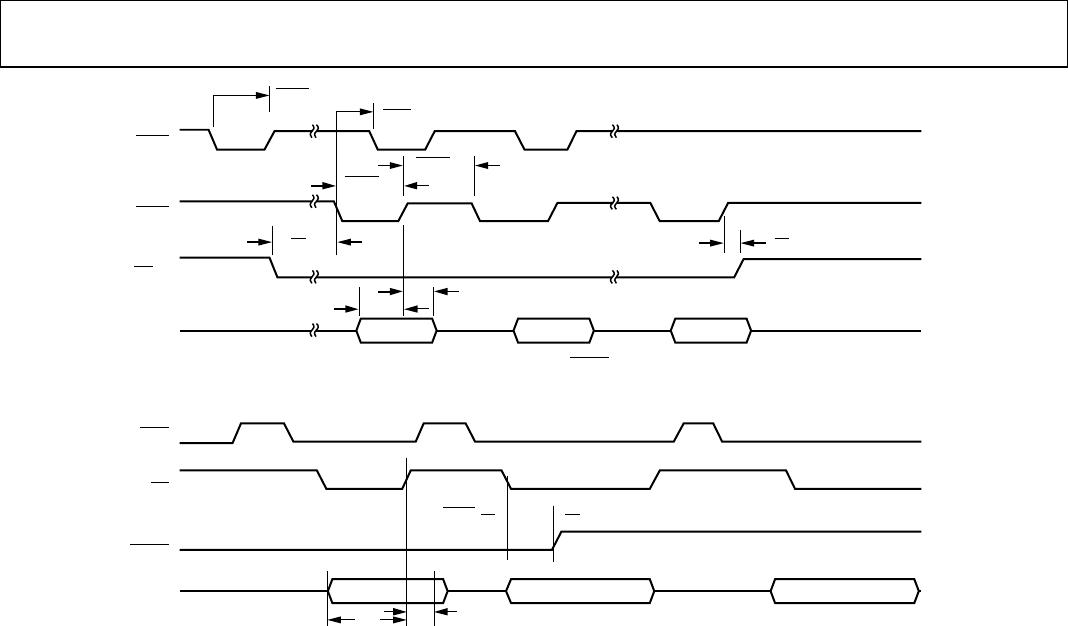

DREQ

/

DACK

DMA MODE—SINGLE FIFO WRITE OPERATION

Table 6.

Parameter Description Min Typ Max Unit

DREQ

PULSE

1

DREQ

Pulse Width 1 15 JCLK cycles

2

t

DREQ

DACK

Assert to Subsequent

DREQ

Delay 2.5 3.5 × JCLK + 7.5 ns JCLK cycles

t

WE

SU

WE

to

DACK

Setup 0 ns

t

SU

Data to

DACK

Deassert Setup 2 ns

t

HD

Data to

DACK

Deassert Hold 2 ns

DACK

LO

DACK

Assert Pulse Width 2 JCLK cycles

DACK

HI

DACK

Deassert Pulse Width 2 JCLK cycles

t

WE

HD

WE

Hold After

DACK

Deassert 0 ns

W

FSRQ

WE

Assert to

FSRQ

Deassert (FIFO Full) 1.5 2.5 × JCLK + 7.5 ns JCLK cycles

t

DREQ

RTN

DACK

to

DREQ

Deassert (DR × PULS = 0) 2.5 3.5 × JCLK + 7.5 ns JCLK cycles

1

Applies to assigned DMA channel, if EDMOD0 or EDMOD1[14:11] is programmed to a value that is not 0. Pulse width depends on the value programmed

2

For a definition of JCLK, see the PLL section.

04723-013

WE

DACK

DREQ

HDATA

3210

DREQ

PULSE

t

DREQ

DACK

HI

DACK

LO

t

WESU

t

SU

t

HD

t

WEHD

Figure 5. Single Write for

DREQ

/

DACK

DMA Mode for Assigned DMA Channel

(EDMOD0/EDMOD1[14:11] NOT Programmed to a Value of 0000)

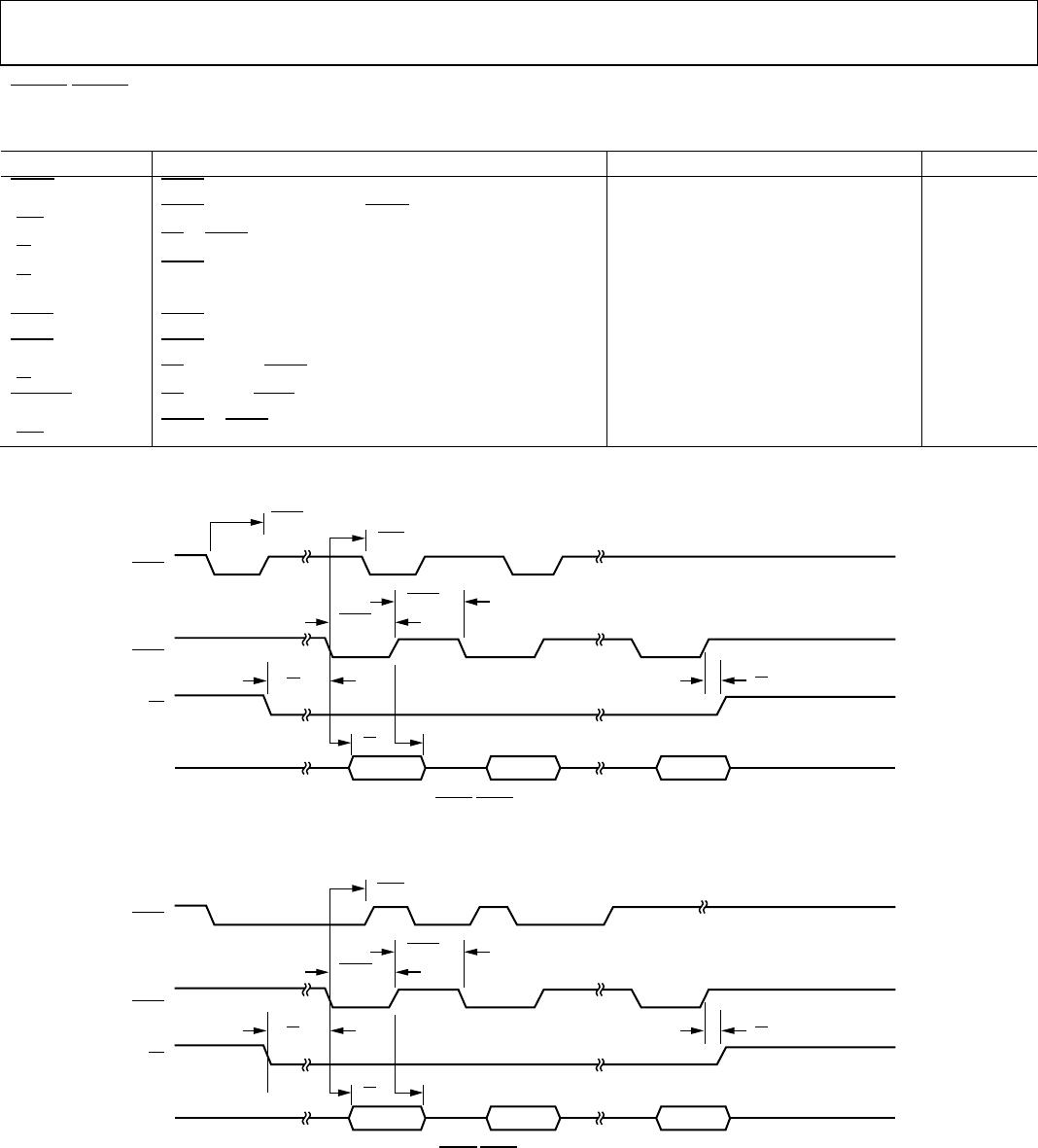

04723-014

WE

DACK

DREQ

HDATA

0

1 2

t

DREQRTN

DACK

HI

DACK

LO

t

WESU

t

SU

t

HD

t

WEHD

Figure 6. Single Write for

DREQ

/

DACK

DMA Mode for Assigned DMA Channel

(EDMOD0/EDMOD1[14:11] Programmed to a Value of 0000)