ADV202 Data Sheet

Rev. D | Page 34 of 40

APPLICATIONS

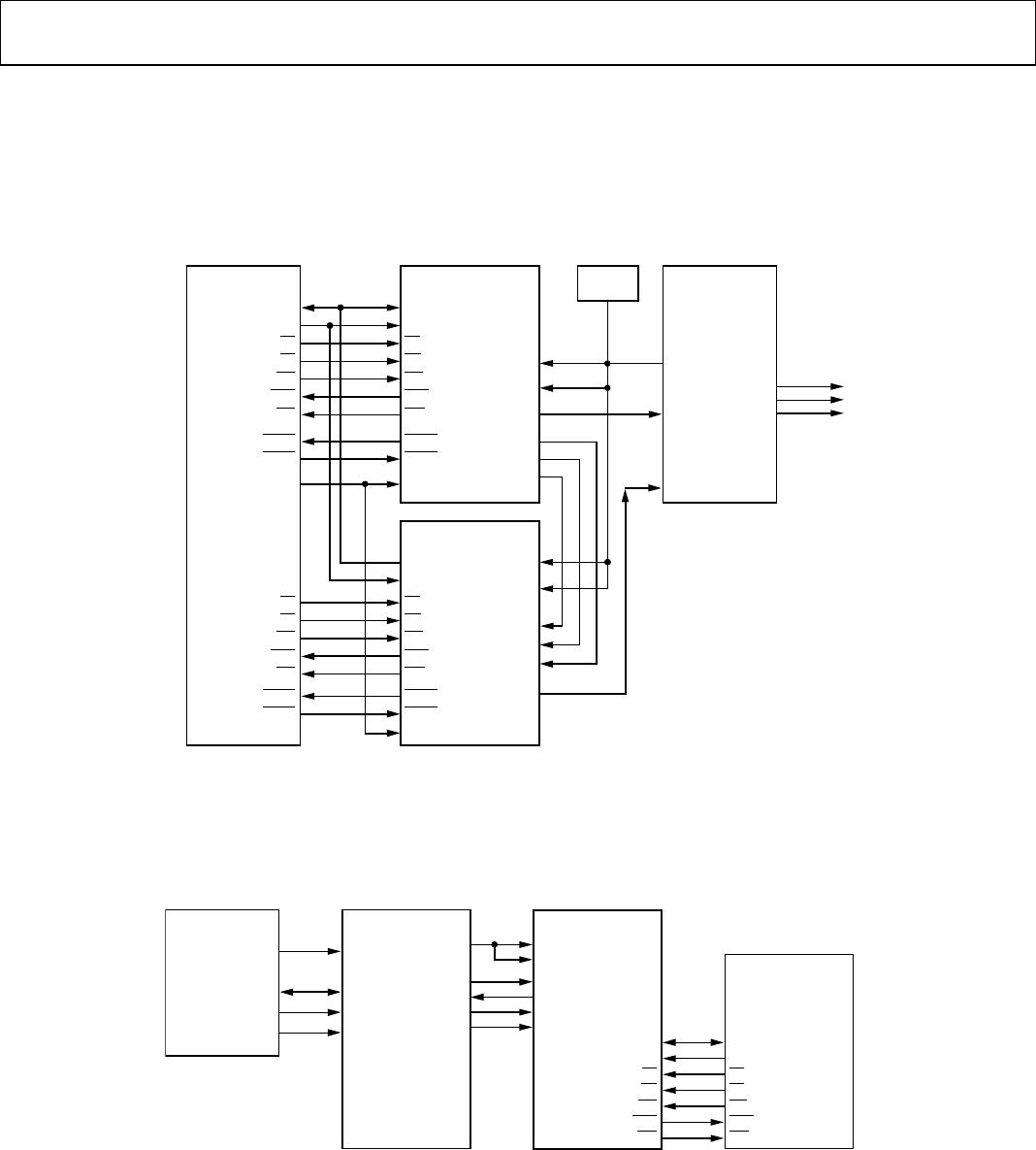

This section describes typical video applications for the

ADV202 JPEG2000 video processor.

ENCODE—MULTICHIP MODE

Due to the data input rate limitation (see Table 24), an 1080i

application requires at least two ADV202s to encode or decode

full-resolution 1080i video. In encode mode, the ADV202

accepts Y and CbCr data on separate buses. The input data must

be in EAV/SAV format. An encode example is shown in Figure 24.

In decode mode, a master/slave configuration (as shown in

Figure 25) or a slave/slave configuration can be used to

synchronize the outputs of the two ADV202s. See AN-796

ADV202 Multichip Application application note for details on

how to configure the ADV202s in a multichip application.

Applications that have two separate VDATA outputs sent to an

FPGA or buffer before they are sent to an encoder do not

require synchronization at the ADV202 outputs

04723-002

DATA[31:0] HDATA[31:0]

ADDR[3:0] ADDR[3:0]

CS CS

RD RD

WR WE

ACK ACK

IRQ

CS

RD

WR

ACK

IRQ

DREQ

DACK

IRQ

DREQ DREQ

FIELD

VSYNC

HSYNC

DACK DACK

G I/O SCOMM[5]

VCLK

1080i

VIDEO IN

MCLK

VDATA[11:2]

32-BIT HOST CPU

10-BIT SD/HD

VIDEO

DECODER

ADV202

_1_SLAVE

SCOMM[5]

HDATA[31:0]

ADDR[3:0]

CS

RD

WE

ACK

IRQ

FIELD

VSYNC

HSYNC

DREQ

DACK

VCLK

MCLK

VDATA[11:2]

ADV202

_2_SLAVE

LLC

Y[9:0]

C[9:0]

CbCr

CbCr

Y

Figure 24. Encode—Multichip Application