Data Sheet ADV202

Rev. D | Page 17 of 40

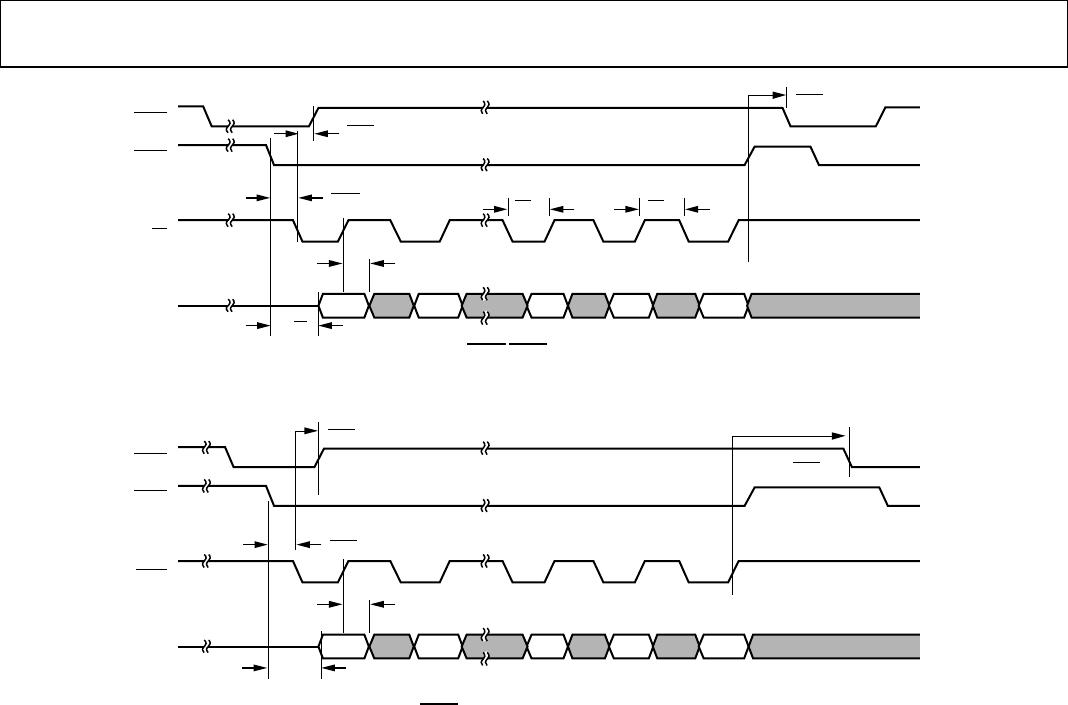

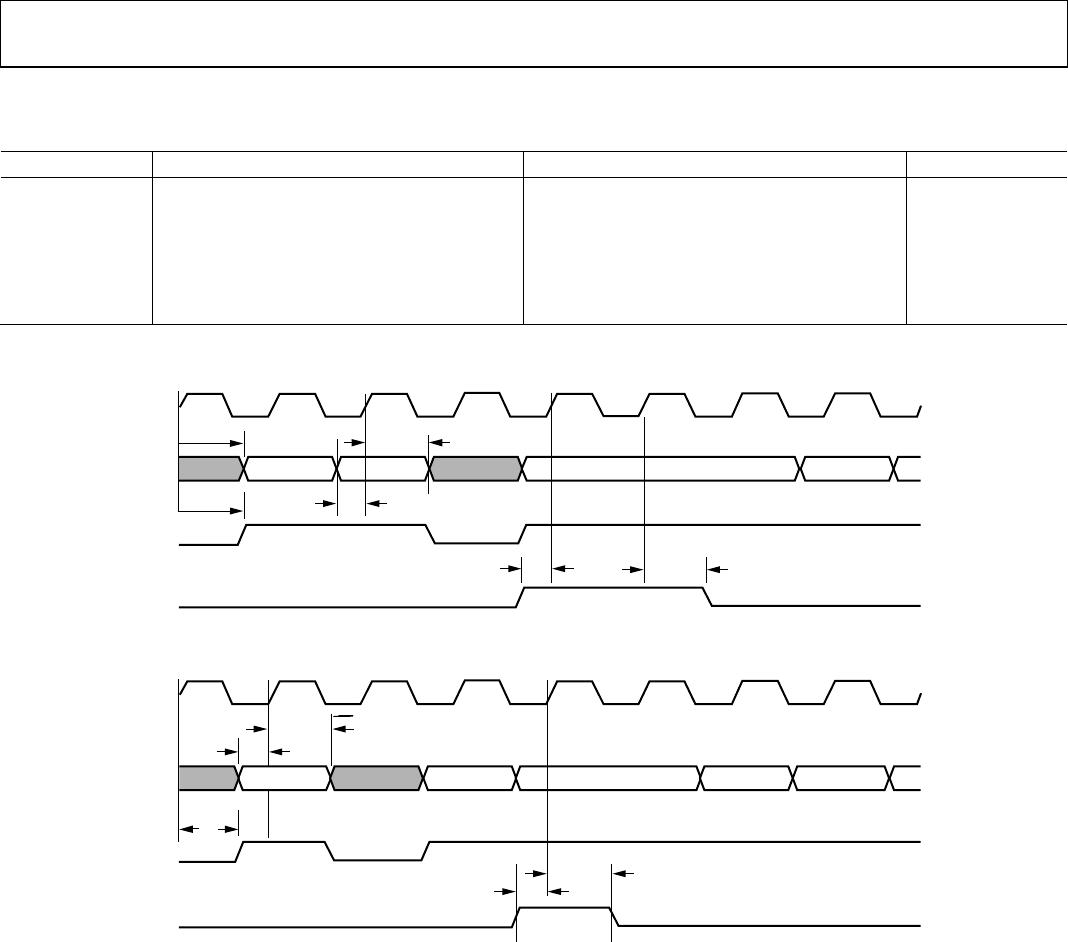

VDATA MODE TIMING

Table 11.

Parameter Description Min Typ Max Unit

VDATA

TD

VCLK to VDATA Valid Delay (VDATA Output) 12 ns

VDATA

SU

VDATA Setup to Rising VCLK (VDATA Input) 4 ns

VDATA

HD

VDATA Hold from Rising VCLK (VDATA Input) 4 ns

HSYNC

SU

HSYNC Setup to Rising VCLK 3 ns

HSYNC

HSYNC Hold from Rising VCLK 4 ns

HSYNC

TD

VCLK to HSYNC Valid Delay 12 ns

VSYNC

SU

VSYNC Setup to Rising VCLK 3 ns

VSYNC

HD

VSYNC Hold from Rising VCLK 4 ns

VSYNC

TD

VCLK to VSYNC Valid Delay 12 ns

FIELD

SU

FIELD Setup to Rising VCLK 4 ns

FIELD

FIELD Hold from Rising VCLK 3 ns

FIELD

TD

VCLK to FIELD Valid 12 ns

SYNC DELAY Decode Data Sync Delay for HD Input with EAV/SAV Codes 7 VCLK cycles

Decode Data Sync Delay for SD Input with EAV/SAV Codes 9 VCLK cycles

Decode Data Sync Delay for HVF Input (from First Rising VCLK after HSYNC Low to

First Data Sample)

10 VCLK cycles

04723-030

Cr Y

Cb Y FF

EAV

FF SAV

Cb Y

Cr

VDATA

HD

VDATA

SU

VCLK

VDATA(IN)

ENCODE CCIR-656 LINE

VDATA

TD

VCLK

VDATA(OUT)

VDATA(OUT)

Cr Y Cb Y

FF EAV

FF SAV

Cb Y

Cr

DECODE MASTER CCIR-656 LINE

VCLK

VDATA(OUT)

VDATA

TD

SYNC DELAY

CrY Y

Cb Y FF EAV

FF SAV

Cb Y

*HSYNC AND VSYNC DO NOT HAVE TO BE APPLIED SIMULTANEOUSLY

VCLK

VDATA(IN)

HSYNC

VSYNC

CrY Y Cb

Y Cr Y Cb Y

YCrYCb

Cb

HSYNC

SU

ENCODE HVF MODE

DECODE SLAVE CCIR-656 LINE

HSYNC

HD

VSYNC

SU

VSYNC

HD

Cb Y Cr Y Cb

CbY

VCLK

HSYNC

VSYNC

DECODE SLAVE HVF MODE

HSYNC

HD

*

VDATA

TD

SYNC DELAY

VSYNC

HD

*

Cb Y Cr Y

Figure 21. Video Mode Timing