DATASHEET

5P1103 REVISION D 07/13/15 1 ©2015 Integrated Device Technology, Inc.

Programmable Fanout Buffer 5P1103

Description

The 5P1103 is a programmable fanout buffer intended for

high performance consumer, networking, industrial,

computing, and data-communications applications.

Configurations may be stored in on-chip One-Time

Programmable (OTP) memory or changed using I

2

C

interface.

The outputs are generated from a single reference clock. The

input reference can be crystal, external single-ended or

differential clock. The reference clock can come from one of

the two redundant clock inputs and is selected by CLKSEL

pin. A glitchless manual switchover function allows one of the

redundant clocks to be selected during normal operation. See

reference clock input section for details.

Two select pins allow up to 4 different configurations to be

programmed and accessible using processor GPIOs or

bootstrapping. The different selections may be used for

different operating modes (full function, partial function, partial

power-down), regional standards (US, Japan, Europe) or

system production margin testing.

The device may be configured to use one of two I

2

C

addresses to allow multiple devices to be used in a system.

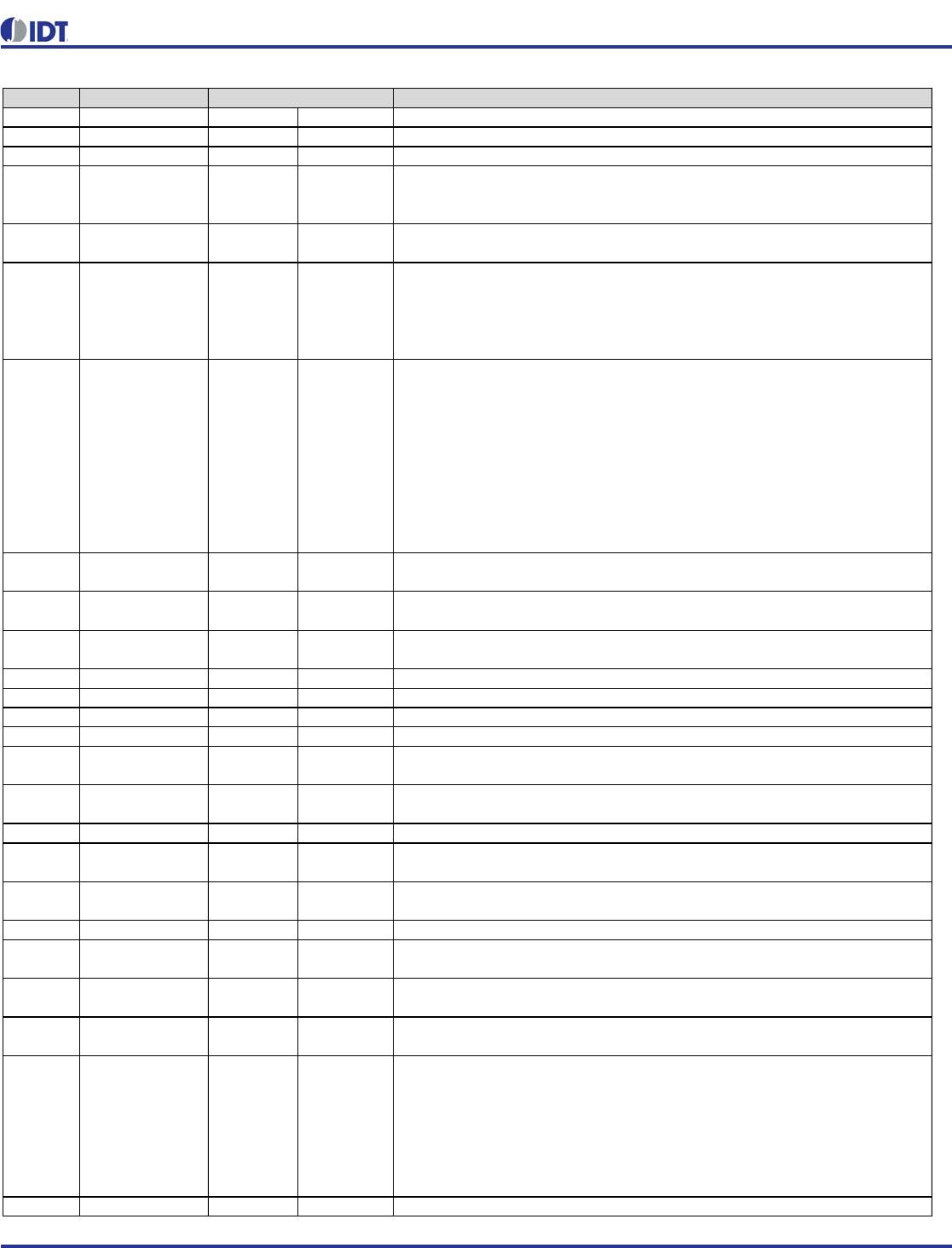

Pin Assignment

Features

• Up to two high performance universal differential output

pairs

– Low RMS additive phase jitter: 0.2ps

• Four banks of internal non-volatile in-system

programmable or factory programmable OTP memory

• I

2

C serial programming interface

• One additional LVCMOS output clock

• Two universal output pairs:

– Each configurable as one differential output pair or two

LVCMOS outputs

• I/O Standards:

– Single-ended I/Os: 1.8V to 3.3V LVCMOS

– Differential I/Os - LVPECL, LVDS and HCSL

• Input frequency ranges:

– LVCMOS Reference Clock Input (XIN/REF) – 1MHz to

200MHz

– LVDS, LVPECL, HCSL Differential Clock Input (CLKIN,

CLKINB) – 1MHz to 350MHz

– Crystal frequency range: 8MHz to 40MHz

• Individually selectable output voltage (1.8V, 2.5V, 3.3V) for

each output pair

• Redundant clock inputs with manual switchover

• Programmable crystal load capacitance

• Individual output enable/disable

• Power-down mode

• 1.8V, 2.5V or 3.3V core V

DDD

, V

DDA

• Available in 24-pin VFQFPN 4mm x 4mm package

• -40° to +85°C industrial temperature operation

1

7

24-pin VFQFPN

19

13

XOUT

XIN/REF

V

DDA

CLKIN

NC

OUT2

CLKINB

CLKSEL

NC

OUT2B

V

DDO

2

V

DDA

SD/OE

SEL1/SDA

SEL0/SCL

V

DDA

NC

NC

OUT1B

OUT1

V

DDO

1

V

DDD

V

DDO

0

OUT0_SEL_I2CB

EPAD

2

3

4

5

6

8

9

10 11

12

14

15

16

17

18

2021222324