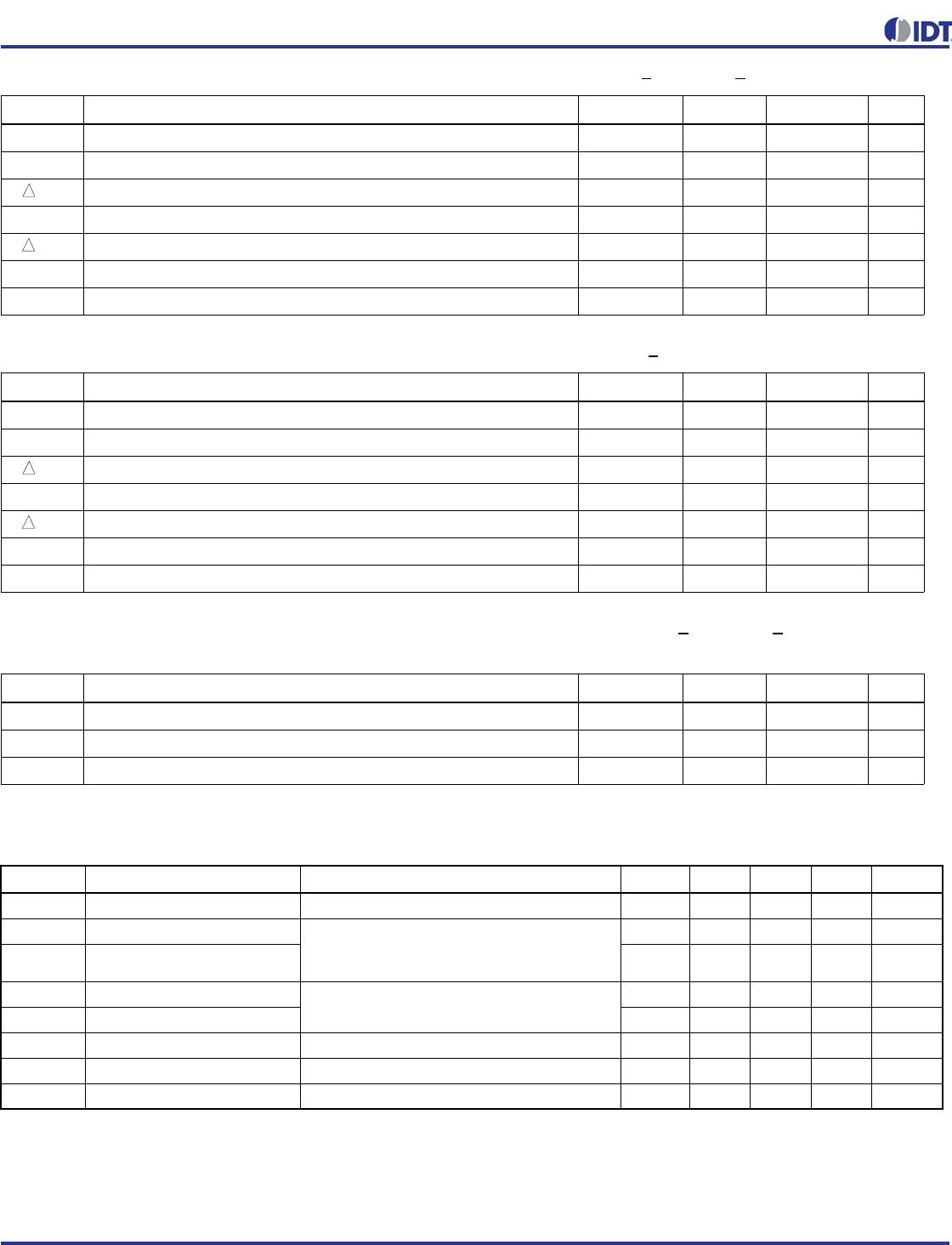

Symbol

Parameter Test Conditions

Min. Typ. Max. Units

Input frequency limit (XIN)

840MHz

Input frequency limit (REF)

1200MHz

Input frequency limit (CLKIN, CLKINB)

1350MHz

Single ended clock output limit (LVCMOS)

1200

Differential cock output limit (LVPECL/ LVDS/HCSL)

1350

t2 Input Duty Cycle

Duty Cycle

45 50 55 %

LVPECL Output Duty Cycle Distortion -5 5 %

LVPECL Output Duty Cycle Distortion -5 5 %

HCSL Output Duty Cycle Distortion -5 5 %

LVCMOS Output Duty Cycle Distortion @ 2.5V and 3.3V -5 5 %

LVCMOS Output Duty Cycle Distortion @ 1.8 V, f <100MHz -5 5 %

LVCMOS Output Duty Cycle Distortion @ 1.8 V, f >=100MHz -10 10 %

Slew Rate, SLEW[1:0] = 11

Single-ended 3.3V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

1.7 2.7 4.1 V/ns

Slew Rate, SLEW[1:0] = 10

Single-ended 3.3V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

1.4 2.4 3.8 V/ns

Slew Rate, SLEW[1:0] = 01

Single-ended 3.3V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

1.3 2.3 3.7 V/ns

Slew Rate, SLEW[1:0] = 00

Single-ended 3.3V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

1.1 2.1 3.6 V/ns

Slew Rate, SLEW[1:0] = 11

Single-ended 2.5V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

0.9 1.7 2.6 V/ns

Slew Rate, SLEW[1:0] = 10

Single-ended 2.5V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

0.6 1.4 2.3 V/ns

Slew Rate, SLEW[1:0] = 01

Single-ended 2.5V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

0.6 1.3 2.2 V/ns

Slew Rate, SLEW[1:0] = 00

Single-ended 2.5V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

0.6 1.2 2.1 V/ns

Slew Rate, SLEW[1:0] = 11

Single-ended 1.8V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

0.7 1.2 2.1 V/ns

Slew Rate, SLEW[1:0] = 10

Single-ended 1.8V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

0.4 0.9 1.7 V/ns

Slew Rate, SLEW[1:0] = 01

Single-ended 1.8V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

0.4 0.8 1.6 V/ns

Slew Rate, SLEW[1:0] = 00

Single-ended 1.8V LVCMOS output clock rise and fall time, @ 125MHz

25% to 75% of VDDO (Output Load = 5 pF)

0.3 0.7 1.4 V/ns

Rise Times

LVDS, 20% to 80%, single-ended

300

Fall Times

LVDS, 80% to 20%, single-ended

300

Rise Times

LVPECL, 20% to 80%, single-ended

400

Fall Times

LVPECL, 80% to 20%, single-ended

400

t6