MAX1710/MAX1711

High-Speed, Digitally Adjusted

Step-Down Controllers for Notebook CPUs

14 ______________________________________________________________________________________

voltage rises approximately 1% (up to 1/2 the peak

amplitude of the ripple waveform as a limit) when under

light loads.

Integrators have both beneficial and detrimental char-

acteristics. While they do correct for drops due to DC

bus resistance and tighten the DC output voltage toler-

ance limits by averaging the peak-to-peak output

ripple, they can interfere with achieving the fastest pos-

sible load-transient response. The fastest transient

response is achieved when all three integrators are dis-

abled. This works very well when the MAX1710/

MAX1711/MAX1712 circuit can be placed very close to

the CPU.

There is often a connector, or at least many milliohms of

PC board trace resistance, between the DC-DC convert-

er and the CPU. In these cases, the best strategy is to

place most of the bulk bypass capacitors close to the

CPU, with just one capacitor on the other side of the con-

nector near the MAX1710/MAX1711/MAX1712 to control

ripple if the CPU card is unplugged. In this situation, the

remote-sense lines and integrators provide a real benefit.

When FBS is connected to V

CC

so that all three integra-

tors are disabled, CC can be left unconnected, which

eliminates a component.

Automatic Pulse-Skipping Switchover

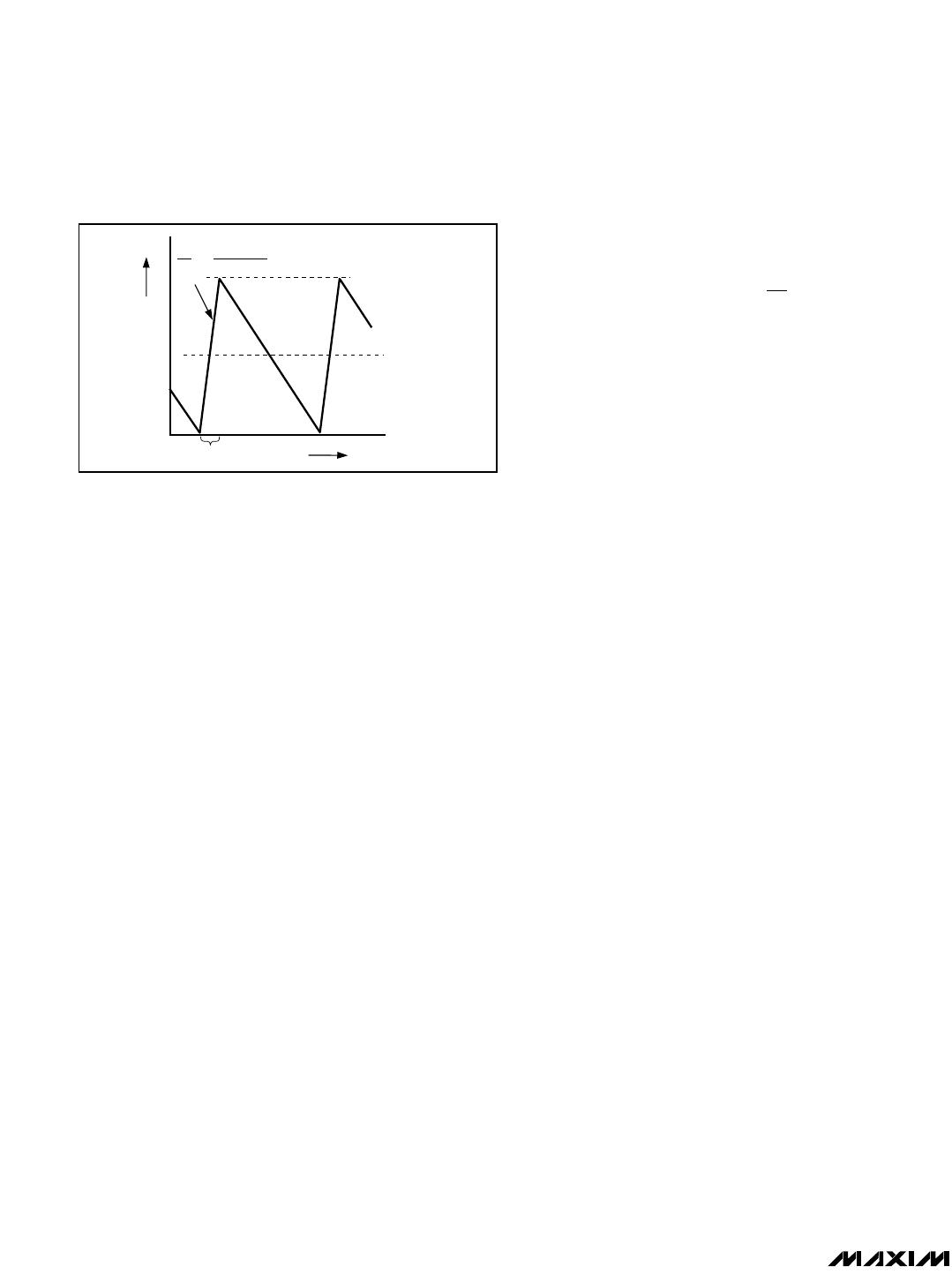

At light loads, an inherent automatic switchover to PFM

takes place. This switchover is effected by a comparator

that truncates the low-side switch on-time at the inductor

current’s zero crossing. This mechanism causes the

threshold between pulse-skipping PFM and nonskipping

PWM operation to coincide with the boundary between

continuous and discontinuous inductor-current operation

(also known as the “critical conduction” point;

see Continuous to Discontinuous Inductor Current Point

vs. Input Voltage graph in the Typical Operating

Characteristics). For a battery range of 7V to 24V, this

threshold is relatively constant, with only a minor depen-

dence on battery voltage.

where K is the On-Time Scale factor (Table 6). The load-

current level at which PFM/PWM crossover occurs,

I

LOAD(SKIP)

, is equal to 1/2 the peak-to-peak ripple cur-

rent, which is a function of the inductor value (Figure 3).

For example, in the standard application circuit with t

ON

= 300ns at 24V, V

OUT

= 2V, and L = 2µH, switchover to

pulse-skipping operation occurs at I

LOAD

= 1.65A or

about 1/4 full load. The crossover point occurs at an

even lower value if a swinging (soft-saturation) inductor

is used.

The switching waveforms may appear noisy and asyn-

chronous when light loading causes pulse-skipping

operation, but this is a normal operating condition that

results in high light-load efficiency. Trade-offs in PFM

noise vs. light-load efficiency can be made by varying

the inductor value. Generally, low inductor values pro-

duce a broader efficiency vs. load curve, while higher

values result in higher full-load efficiency (assuming that

the coil resistance remains fixed) and less output voltage

ripple. Penalties for using higher inductor values include

larger physical size and degraded load-transient

response (especially at low input voltage levels).

Forced-PWM Mode (

SSKKIIPP

= High)

The low-noise, forced-PWM mode (SKIP driven high) dis-

ables the zero-crossing comparator, which controls the

low-side switch on-time. This causes the low-side gate-

drive waveform to become the complement of the high-

side gate-drive waveform. This in turn causes the

inductor current to reverse at light loads, as the PWM

loop strives to maintain a duty ratio of V

OUT

/V

IN

. The

benefit of forced-PWM mode is to keep the switching fre-

quency fairly constant, but it comes at a cost: the no-

load battery current can be as high as 40mA or more.

Forced-PWM mode is most useful for reducing audio-fre-

quency noise, improving load-transient response, pro-

viding sink-current capability for dynamic output voltage

adjustment, and improving the cross-regulation of multi-

ple-output applications that use a flyback transformer or

coupled inductor.

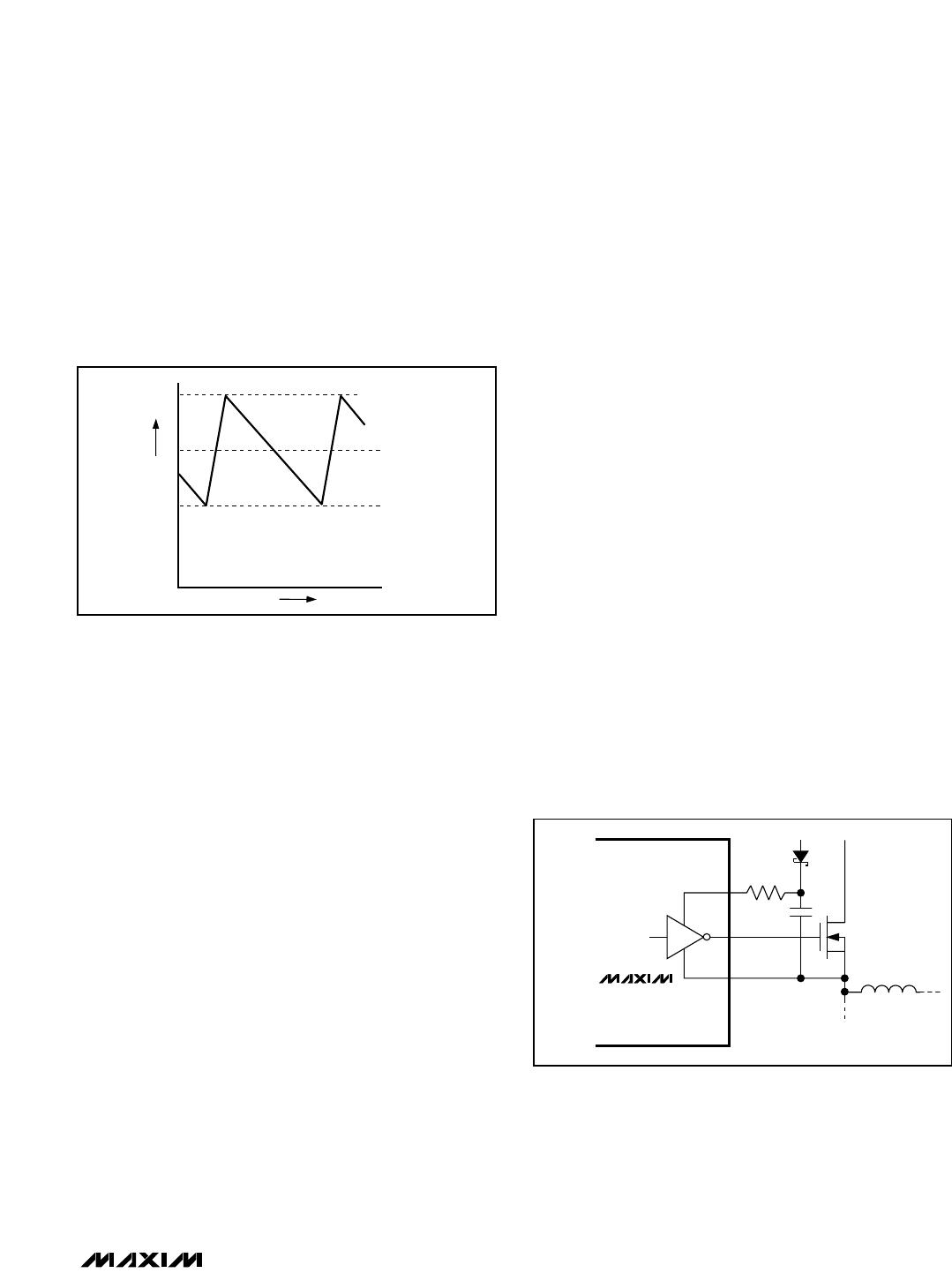

Current-Limit Circuit (ILIM)

The current-limit circuit employs a unique “valley” cur-

rent-sensing algorithm that uses the on-state resistance

of the low-side MOSFET as a current-sensing element. If

the current-sense signal is above the current-limit

threshold, the PWM is not allowed to initiate a new cycle

(Figure 4). The actual peak current is greater than the

current-limit threshold by an amount equal to the induc-