MAX1710/MAX1711/MAX1712

High-Speed, Digitally Adjusted

Step-Down Controllers for Notebook CPUs

minimize the energy transferred from inductor to capaci-

tor during load-step recovery. Even so, the amount of

overshoot is high enough (80mV) that for the MAX1710,

it’s wise to disable OVP or use the MAX1711/MAX1712

with their fixed 2.25V overvoltage protection threshold to

avoid tripping the fault latch (see the overshoot equation

in the Output Capacitor Selection section). The efficiency

penalty for operating at 550kHz is about 2% to 3%,

depending on the input voltage.

Two optional 1kΩ resistors are placed in series with FB

and FBS. These resistors prevent the negative output

voltage spike (that results from tripping OVP) from

pulling SHDN low via its internal ESD diode, which tends

to clear the fault latch, causing “hiccup” restarts.

Setting V

OUT

with a Resistor-Divider

The output voltage can be adjusted with a resistor-

divider rather than the DAC if desired (Figure 8). The

drawback of this practice is that the on-time doesn’t

automatically receive correct compensation for changing

output voltage levels. This can result in variable switch-

ing frequency as the resistor ratio is changed and/or

excessive switching frequency. The equation for adjust-

ing the output voltage is:

where V

FB

is the currently selected DAC value. When

using external resistors, FBS remote sensing is not rec-

ommended, but GNDS remote sensing is still possible.

Connect FBS to FB and GNDS to remote ground loca-

tion. In resistor-adjusted circuits, the DAC code should

be set as close as possible to the actual output voltage

so that the switching frequency doesn’t become exces-

sive. For highest accuracy, use the MAX1710 when

adjusting V

OUT

with external resistors. The MAX1710 FB

node has very high impedance, while the MAX1711/

MAX1712 have a 180kΩ ±35% FB impedance, which

degrades V

OUT

accuracy.

Adjusting V

OUT

Above 2V

The feed-forward circuit that makes the on-time depen-

dent on battery voltage maintains a nearly constant

switching frequency as V

IN

, I

LOAD

, and the DAC code

are changed. This works extremely well as long as FB is

connected directly to the output.

When the output is adjusted higher than 2V with a resis-

tor-divider, the switching frequency can be increased to

relatively unreasonable levels as the actual off-time

decreases and isn’t compensated for by a change in on-

time; 3.3V is about the maximum limit to the practical

adjustment range. Even at the slowest TON setting and

with the DAC set to 2V, the switching rate will exceed

600kHz.

The trip threshold for output overvoltage protection

scales with the nominal output voltage setting.

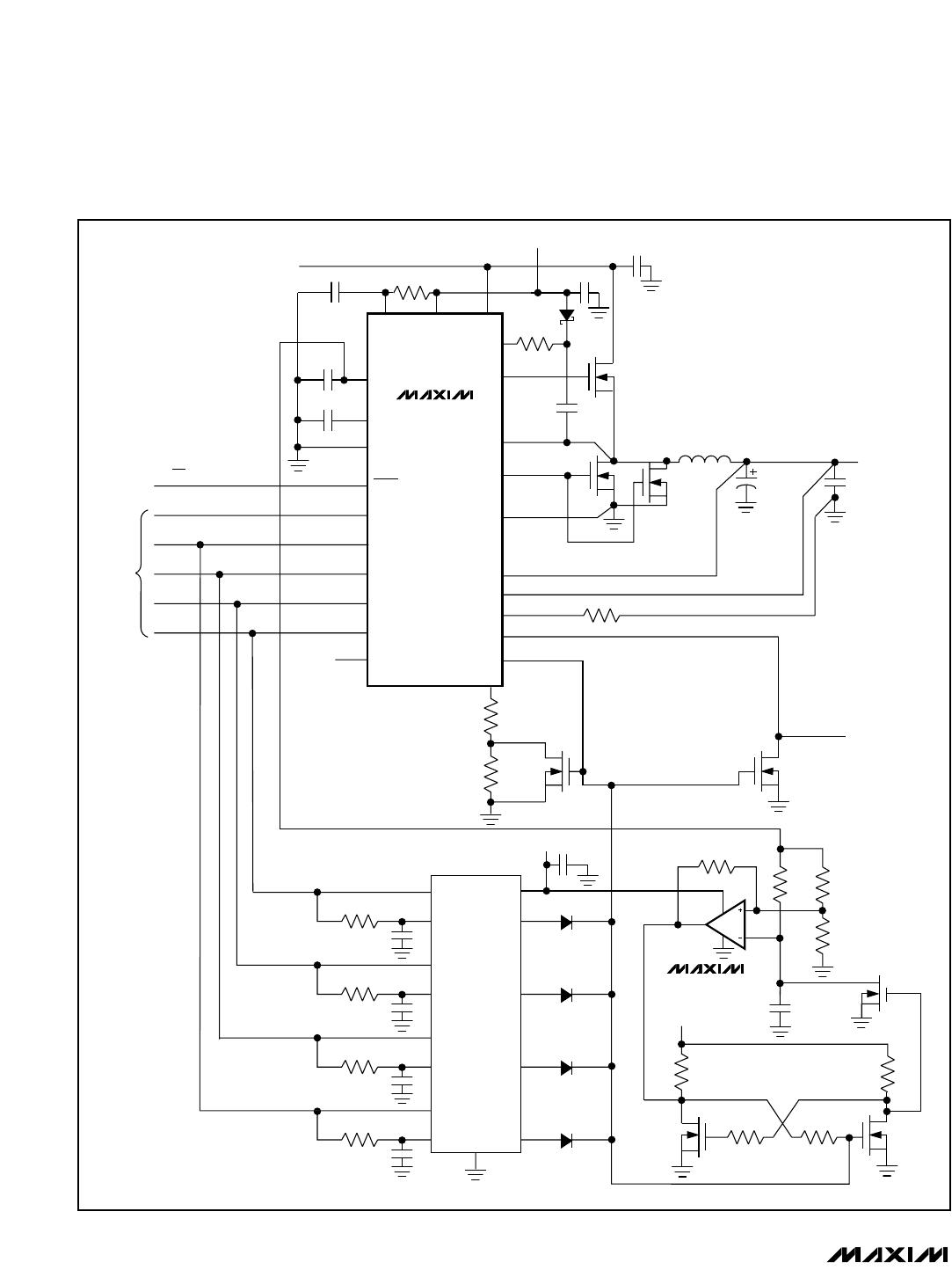

2-Stage (5V-Powered) Notebook CPU

Buck Regulator

The most efficient and overall cost-effective solution for

stepping down a high-voltage battery to very low output

voltage is to use a single-stage buck regulator that’s

powered directly from the battery. However, there may

be situations where the battery bus can’t be routed near

the CPU, or where space constraints dictate the smallest

possible local DC-DC converter. In such cases, the 5V-

powered circuit of Figure 9 may be appropriate. The

reduced input voltage allows a higher switching frequen-

cy and a much smaller inductor value.

Dynamic DAC Code Changes

(MAX1711/MAX1712)

Changing the output voltage dynamically by switching

DAC codes “on-the-fly” can be used to help make

power-savings/performance trade-offs in the host sys-

tem. Several important design issues arise from this

practice.

First, know that attempting to slew the output upward

quickly causes large current surges at the battery as the

IC goes into output current limiting during the transition.

Surge currents can be controlled either by counting the

DAC code slowly (50kHz or slower rate suggested), or

by modulating the I

LIM

current-limit threshold.

The DAC inputs must be driven quickly to the new value

so the device doesn’t wrongly interpret a disallowed