AD1953

–10–

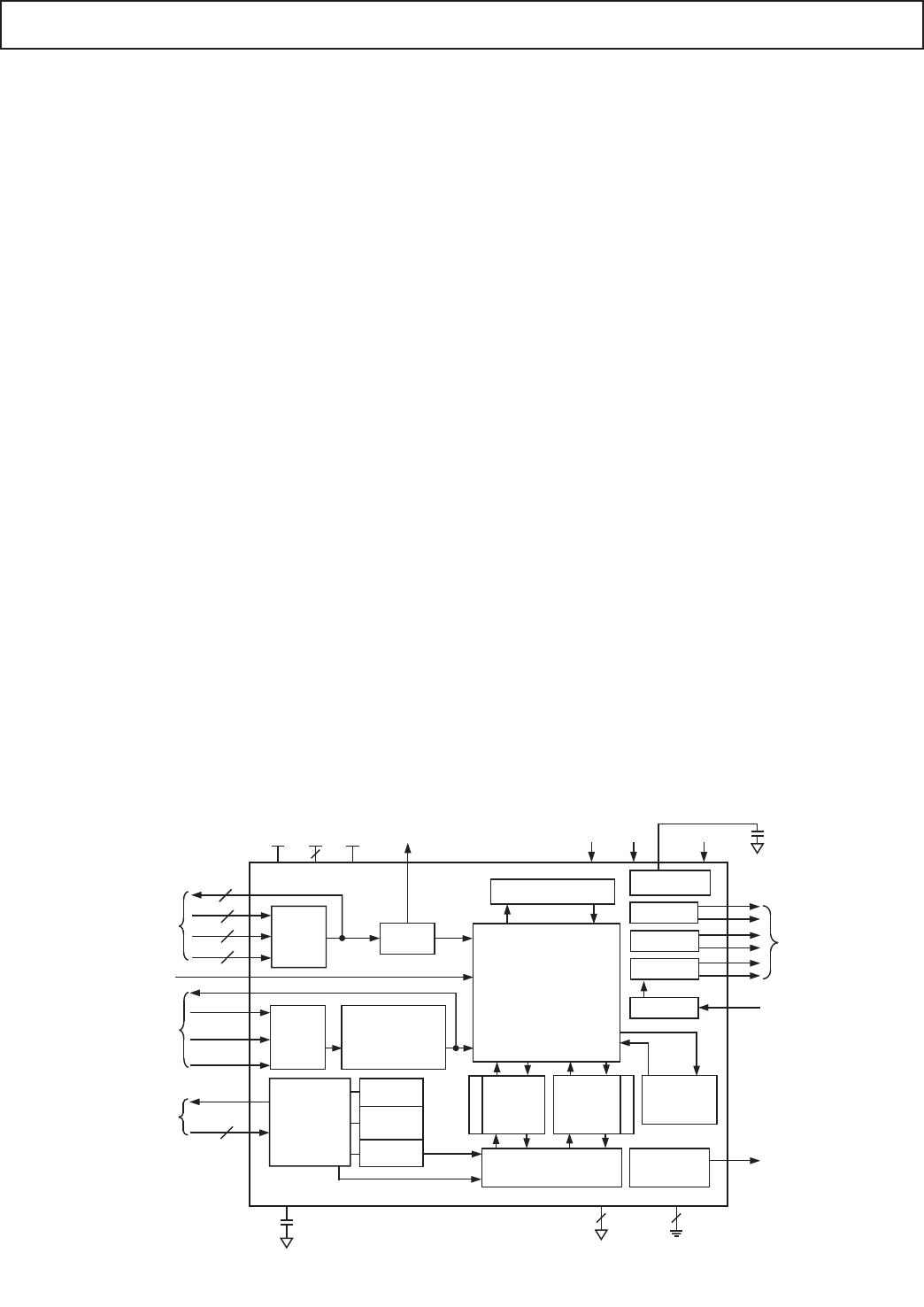

Pin Functions

All input pins have a logic threshold compatible with TTL input

levels, and may therefore be used in systems with 3.3 V logic.

All digital output levels are controlled by the ODVDD pin,

which may range from 2.7 V to 5.5 V, for compatibility with a

wide range of external devices. (See Pin Function Descriptions.)

SDATA0, 1, 2—Serial Data Inputs.

One of these three inputs is selected by an internal MUX, set by

writing to Bits <7:6> in Control Register 2. Default is 00, which

selects SDATA0. The serial format is selected by writing to Bits

<3:0> of Control Register 0. See SPI Read/Write Data Formats

section for recommendations on how to change input sources

without causing a click or pop noise.

LRCLK0, 1, 2—Left/Right Clocks for Framing the Input Data.

The active LRCLK input is selected by writing to Bits <7:6>

in Control Register 2. Default is 00, which selects LRCLK0.

The interpretation of the LRCLK changes according to the serial

mode, set by writing to Control Register 0.

BCLK0, 1, 2—Serial Bit Clocks for Clocking in the Serial Data.

The active BCLK input is selected by writing to Bits <7:6> in

Control Register 2. Default is 00, which selects BCLK0. The

interpretation of BCLK changes according to the serial mode,

which is set by writing to Control Register 0.

DMUXO/TDMO, LRMUXO/TDMFS, BMUXO/TDMBC

Dual-function pins:

•

Function 1: Outputs of 3:1 MUX that selects one of the

three serial input groups.

•

Function 2: Used for 6-channel data capture outputs in

TDM Data Capture Mode.

These three pins operate as MUX outputs when Bit <8> of

Control Register 2 is a 1 and Bits <13:12> of Control Register 1

are 00. These pins may be used to send the selected serial input

signals to other external devices. The default is OFF.

In TDM mode, TDMBC provides a 256

×

f

S

clock signal,

TDMFS provides a frame sync signal, and TDMO provides the

TDM data for an external multichannel DAC or CODEC, such

as the AD1833 or AD1836 respectively. These output pins are

enabled by writing a 01 to Bits <13:12> of Control Register 1.

The default mode is 00, or OFF.

In TDM mode, the internal signals that are captured are con-

trolled by writing Program Counter Trap numbers to SPI

addresses 268 to 273. When the internal Program Counter

contents are equal to the Trap values written to the SPI port, the

selected DSP register is transferred to parallel-to-serial registers

and shifted out of the TDMO pin.

MCLK0, 1, 2—Master Clock Inputs.

Active input selected by writing to Bits <5:4> of Control Regis-

ter 2. The default is 00, which selects MCLK0. The master clock

frequency must be either 256 × f

S

or 512 × f

S

, where f

S

is the input

sampling rate. The master clock frequency is programmed by

writing to Bit <2> of Control Register 2. The default is 0, (512

× f

S

). See Initialization section for recommendations concerning

how to change clock sources without causing an audio click or

pop. Note that since the default MCLK source pin is MCLK0,

there must be a clock signal present on this pin on power-up so

that the AD1953 can complete its initialization routine.

MCLKO—Master Clock Output.

The master clock output pin may be programmed to produce

either 256 × f

S

, 512 × f

S

, or a copy of the selected MCLK input

pin. This pin is programmed by writing to Bits <1:0> of Control

Register 2. The default is 00, which disables the MCLKO pin.

CDATA—Serial Data In for the SPI Control Port.

See SPI Port section for more information on SPI port timing.

COUT—Serial Data Output.

This is used for reading back registers and memory locations. It

is three-stated when an SPI read is not active. See SPI Port

section for more information on SPI port timing.

CCLK—SPI Bit Rate Clock.

This pin either may run continuously or be gated off between

SPI transactions. See SPI Port section for more information on

SPI port timing.

CLATCH—SPI Latch Signal.

This pin must go LOW at the beginning of an SPI transaction,

and HIGH at the end of a transaction. Each SPI transaction

may take a different number of CCLKs to complete, depending

on the address and read/write bit that are sent at the beginning

of the SPI transaction. Detailed SPI timing information is given

in the SPI Port section.

RESETB—Active-Low Reset Signal.

After RESETB goes HIGH, the AD1953 goes through an ini-

tialization sequence where the program and parameter RAMs

are initialized with the contents of the on-board boot ROMs. All

SPI registers are set to 0, and the data RAMs are also zeroed.

The initialization is complete after 1024 MCLK cycles. Since

the MCLK IN FREQ SELECT (Bit <2> in Control Register 2)

defaults to 512 × f

S

at power-up, this initialization will proceed

at the external MCLK rate and will take 1024 MCLK cycles to

complete, regardless of the absolute frequency of the external

MCLK. New values should not be written to the SPI port until

the initialization is complete.

ZEROFLAG—Zero-Input Indicator.

This pin will go HIGH if both serial inputs have been inactive

(zero data) for 1024 LRCLK cycles. This pin may be used to

drive an external mute FET for reduced noise during digital

silence. This pin also functions as a test out pin, controlled by

the test register at SPI address 511. While most test modes are

not useful to the end user, one may be of some use. If the test

register is programmed with the number 7 (decimal), the

ZEROFLAG output will be switched to the output of the inter-

nal pseudo-random noise generator. This noise generator

operates at a bit rate of 128 × f

S

, and has a repeat time of once

per 2

24

cycles. This mode may be used to generate white noise

(or, with appropriate filtering, pink noise) to be used as a test

signal for measuring speakers or room acoustics.

DCSOUT—Data Capture Serial Out.

This pin will output the DSP’s internal signals, which can be

used by external DACs or other signal-processing devices. The

signals that are captured and output on the DCSOUT pin are

controlled by writing Program Counter Trap numbers to SPI

addresses 263 (for the left output) and 264 (for the right output).

When the internal Program Counter contents are equal to the

Trap values written to the SPI port, the selected DSP register is

transferred to the DCSOUT parallel-to-serial registers and

REV. A