AD1953

–18–

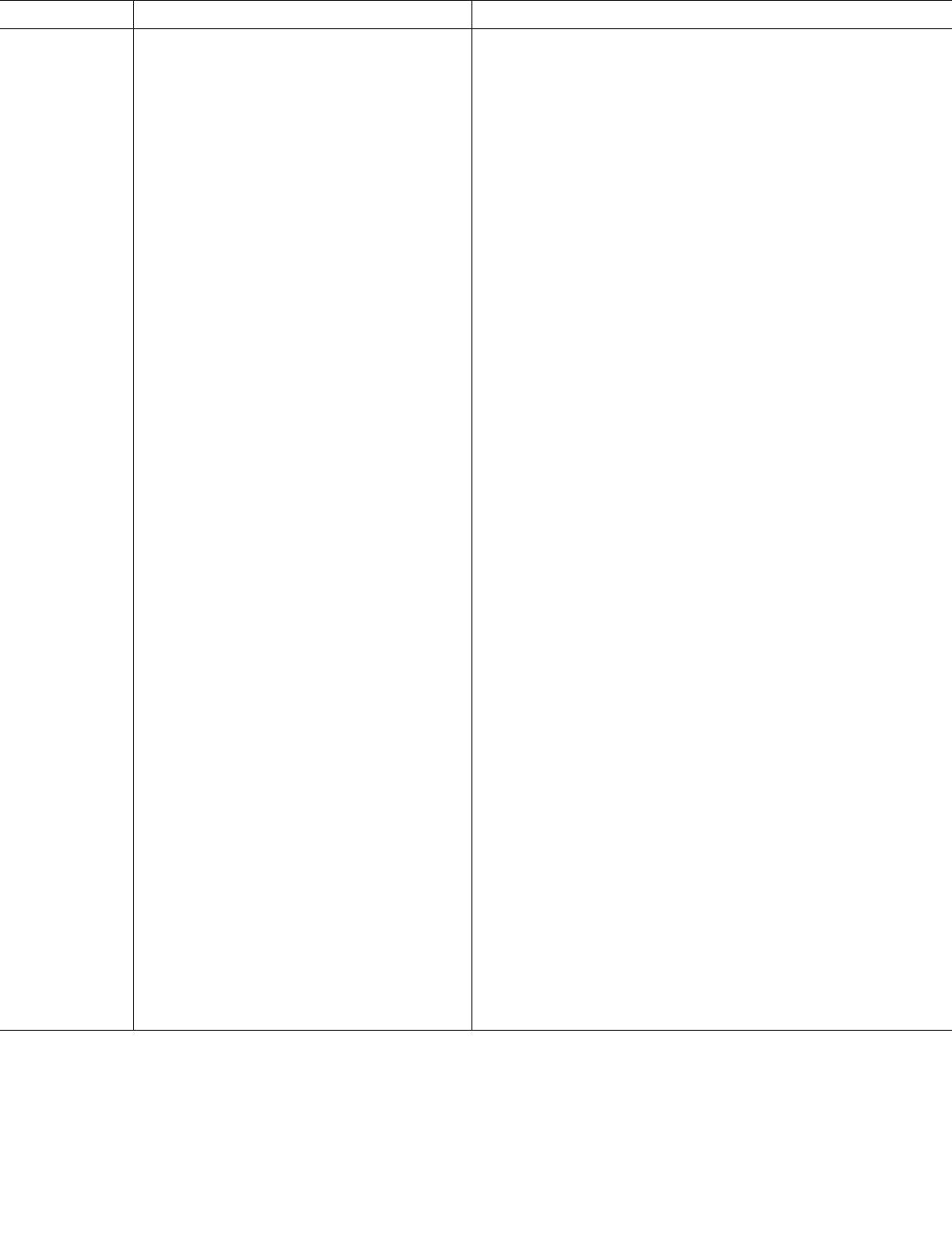

was not so sensitive to overload, then the compressor would be

too pessimistic and the volume of the woofer would be reduced.

If, on the other hand, the biquad filter were designed to follow

the woofer excursion curve of the speaker, then the volume of

the woofer could be maximized under all conditions. This is

illustrated in Figure 15.

20Hz 200Hz

FREQ

WOOFER EXCURSION

BIQUAD RESPONSE

20Hz 200Hz

FREQ

Figure 15. Optimizing Woofer Loudness Using the

Subwoofer RMS Biquad Filter

When using a filter in front of the detector, a confusing side-

effect occurs. If one measures the frequency response by using a

swept sine wave with an amplitude large enough to be above the

compressor threshold, the resulting frequency response will not

look flat. However, this is not real in the sense that, as the sine

wave is swept through the system, the gain is being slowly

modulated up and down according to the response of the biquad

filter in front of the detector. If one measures the response using a

pink-noise generator, the result will look much better, as the

detector will settle on only one gain value. The perceptual effect

of the swept-sine-wave test is not at all what would be pre-

dicted by simply looking at the frequency response curve; it is

only the signal-path filters that will affect the perception of fre-

quency response, not the detector-path filters.

De-emphasis Filtering

The standard for encoding CDs allows the use of a pre-emphasis

curve during encoding, which must be compensated for by a

de-emphasis curve during playback. The de-emphasis curve is

defined as a first-order shelving filter with a single pole at

(1/(2 × π × 50 μs)) followed by a single zero at (1/(2 × π × 15 μs)).

This curve may be accurately modeled using a first-order digital

filter. This filter is included in the AD1953; it is not part of the

bank of biquad filters, and so does not take away from the num-

ber of available filters.

Since the specification of the de-emphasis filter is based on an

analog filter, the response of the filter should not depend on the

incoming sampling rate. However, when the de-emphasis filter is

implemented digitally, the response will scale with the sampling rate

unless the filter coefficients are altered to suit each possible input

sampling rate. For this reason, the AD1953 includes three separate

de-emphasis curves; one each for sampling rates of 32 kHz, 44.1 kHz,

and 48 kHz. These curves are selected by writing to Bits <5:4> of

Control Register 1 over the SPI port.

Using the Sub Reinjection Paths for Systems with No Subwoofer

Many systems will not use a subwoofer, but would still benefit

from 2-band compression/limiting. This can be accommodated

by using sub reinjection paths in the program flow. These

parameters are programmed by entering two numbers (in 2.20

format) into the parameter RAM. Note that if the biquad filters

are not properly designed, the frequency response at the cross-

over point may not be flat. Many crossover filters are designed to

be flat in the sense of adding the powers together, but nonflat if

the sum is done in voltage mode. The user must take care to

design an appropriate set of crossover filters.

Interpolation Filters

The left and right channels have a 128:1 interpolation filter

with 70 dB stop-band attenuation that precedes the digital Σ-Δ

modulator. This filter has a group delay of approximately 24.185/f

S

,

where f

S

is the sampling rate. The sub channel does not use an

interpolation filter. The reason for this (besides saving valuable

MIPS) is that it is expected that the bandwidth of the sub output

will be limited to less than 1 kHz. With no interpolation filter, the

first “image” will therefore be at 43.1 kHz (which is f

S

– 1 kHz,

for CD audio). The standard external filter used for both the

main and sub channels is a third-order, single op amp filter. If

the cutoff frequency of the external subwoofer filter is 2 kHz,

then there are more than four octaves between 2 kHz and the

first image at 43.1 kHz. A third-order filter will roll off by

approximately 18 dB/oct × 4 octaves = 72 dB attenuation. This is

approximately the same as the digital attenuation used in the main

channel filters, so no internal interpolation filter is required to remove

the out-of-band images.

Note that by having interpolation filters in the main channels but

not the subwoofer channel, there is a potential time-delay mis-

match between the main and sub channels. The group delay of

the digital interpolation filters used in the main left/right channels

is about 0.5 ms. This must be compared to the group delay of

the external analog filter used in the subwoofer path. If the

group delay mismatch causes a frequency response error (when the

two signals are “acoustically added”), the programmable delay

feature can be used to put extra delay in either the subwoofer path

or the main left/right path.

SPI PORT

Overview

The AD1953 has many different control options. Most signal-

processing parameters are controlled by writing new values to

the parameter RAM using the SPI port. Other functions such as

volume and de-emphasis filtering are programmed by writing to

SPI control registers.

The SPI port uses a 4-wire interface, consisting of CLATCH,

CCLK, CDATA, and COUT signals. The CLATCH signal

goes LOW at the beginning of a transaction and HIGH at the

end of a transaction. The CCLK signal latches the serial input

data on a low-to-high transition. The CDATA signal carries the

serial input data, and the COUT signal is the serial output data.

The COUT signal remains three-stated until a read operation is

requested. This allows other SPI compatible peripherals to

share the same readback line.

The SPI port is capable of full read/write operation for all of the

memories (parameter and program) and some of the SPI registers

(Control Register 1 and data capture registers). The memories

may be accessed in both a single-address mode or in burst mode.

All SPI transactions follow the same basic format, shown in Table I.

The Wb/R bit is low for a write, and high for a read operation.

The 10-bit address word is decoded into a location in one of the

two memories (parameter or program) or one of the SPI regis-

ters. The number of data bytes varies according to the register

or memory being accessed. In burst-write mode (available for

loading the RAMs only), an initial address is given followed by a

continuous sequence of data for consecutive RAM locations.

REV. A