XRD98L23

19

Rev. 1.00

Area or Linear CCD Applications

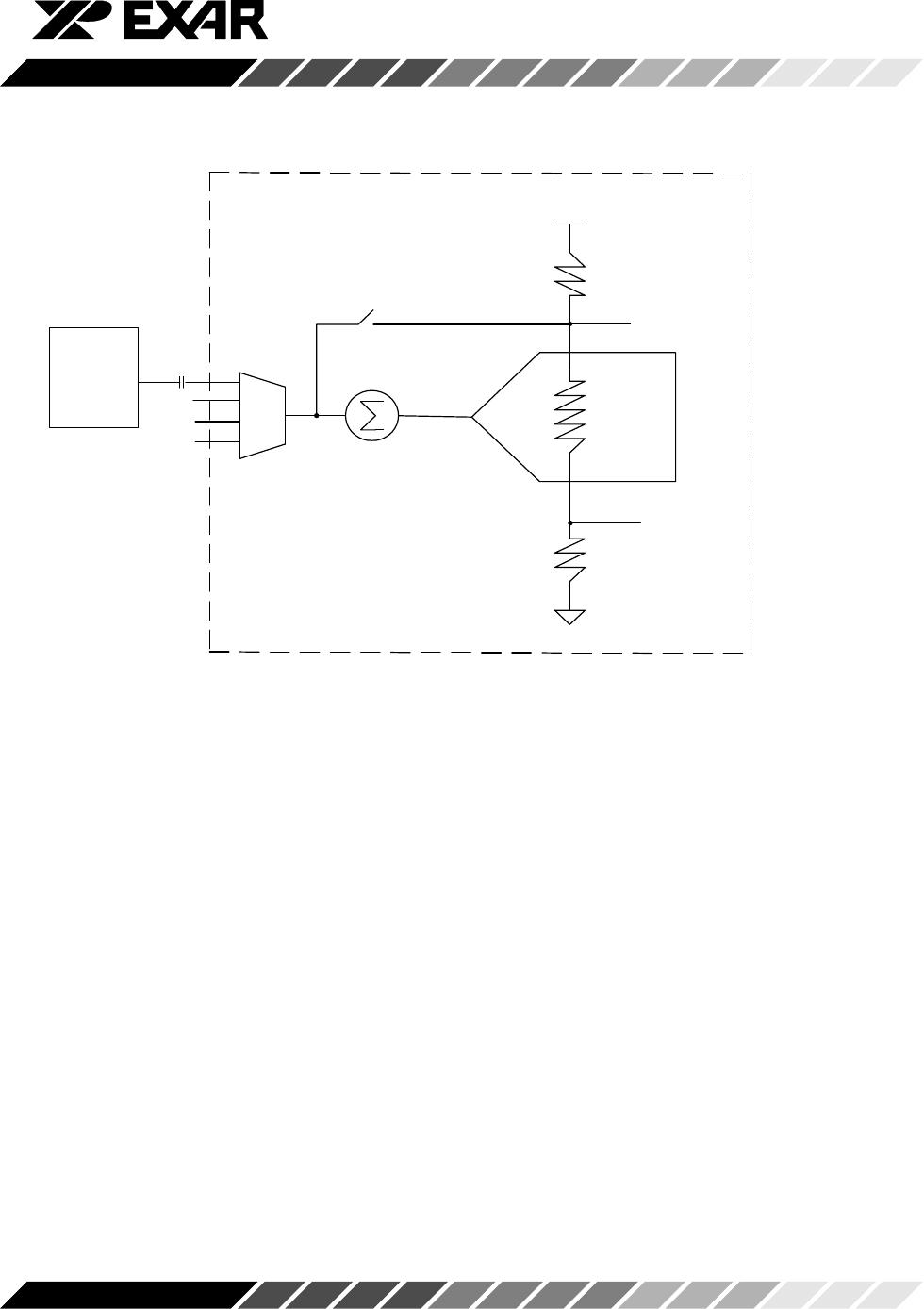

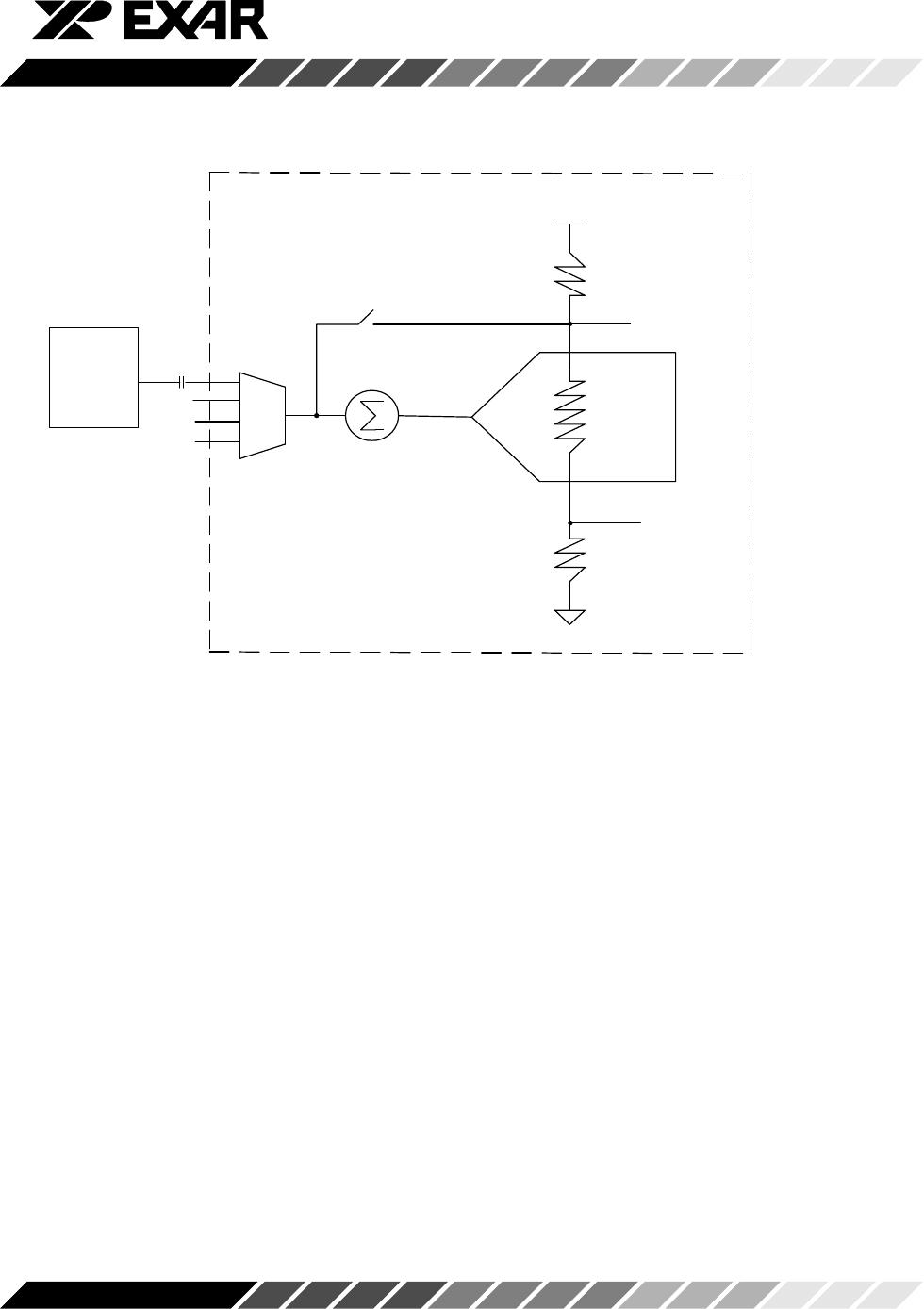

Figure 13, is a block diagram for applications with Area

or Linear CCDs (The timing for Area CCDs and B/W

CCDs is the same). For Area or Linear CCD applica-

tions, a global offset is loaded into the serial port at the

beginning of a line. The gain is set to adjust for the

highest color intensity of the CCD output. Once the

pixel values have been sampled, the gain and offset are

adjusted at the beginning of the next line. For example,

if there is a line-to-line variation between the black

reference pixels, the offset is adjusted. The gain is

always adjusted for the highest color intensity.

Figure 13. CCD AC Coupled Application

RL

VRT

VRB

VDD

RED

XRD98L23

CLAMP

M

U

X

AREA

or

LINEAR

CCD

N/C

N/C

N/C