PCA85134 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2014. All rights reserved.

Product data sheet Rev. 2 — 6 May 2014 17 of 53

NXP Semiconductors

PCA85134

Automotive 60 x 4 LCD segment driver for low multiplex rates

7.9 Backplane outputs

The LCD drive section includes four backplane outputs BP0 to BP3 which must be

connected directly to the LCD. The backplane output signals are generated in accordance

with the selected LCD drive mode.

• In 1:4 multiplex drive mode: BP0 to BP3 must be connected directly to the LCD.

If less than four backplane outputs are required, the unused outputs can be left

open-circuit.

• In 1:3 multiplex drive mode, BP3 carries the same signal as BP1, therefore these two

adjacent outputs can be tied together to give enhanced drive capabilities.

• In 1:2 multiplex drive mode, BP0 and BP2, respectively, BP1 and BP3 carry the same

signals and can also be paired to increase the drive capabilities.

• In static drive mode, the same signal is carried by all four backplane outputs and they

can be connected in parallel for very high drive requirements.

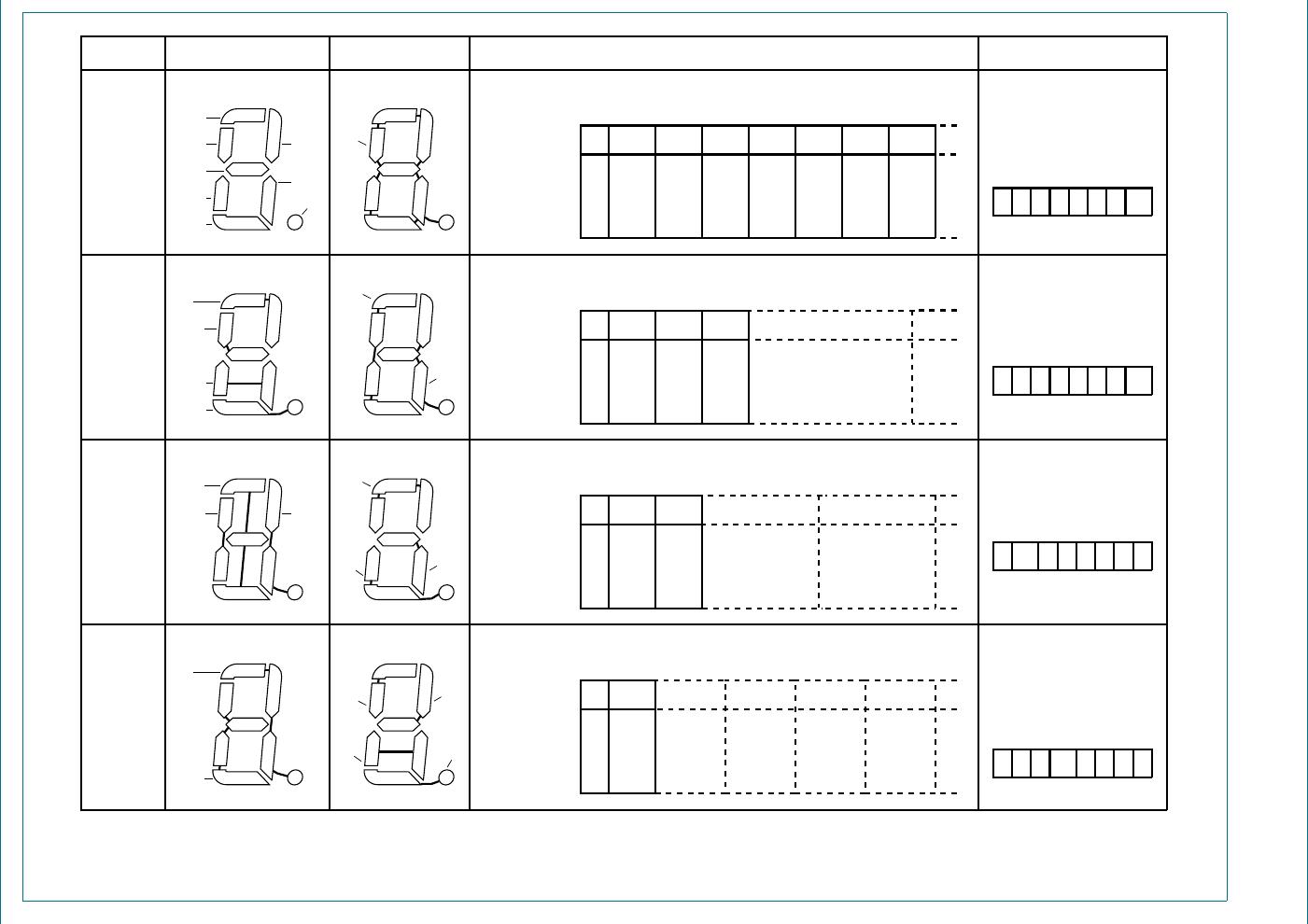

7.10 Display RAM

The display RAM is a static 60 4-bit RAM which stores LCD data. A logic 1 in the RAM

bit map indicates the on-state (V

on(RMS)

) of the corresponding LCD element. Similarly, a

logic 0 indicates the off-state (V

off(RMS)

). For more information on V

on(RMS)

and V

off(RMS)

,

see Section 7.3

.

There is a one-to-one correspondence between

• the bits in the RAM bitmap and the LCD elements

• the RAM columns and the segment outputs

• the RAM rows and the backplane outputs.

The display RAM bit map, Figure 11

, shows row 0 to row 3 which correspond with the

backplane outputs BP0 to BP3, and column 0 to column 59 which correspond with the

segment outputs S0 to S59. In multiplexed LCD applications, the data of each row of the

display RAM is time-multiplexed with the corresponding backplane (row 0 with BP0, row 1

with BP1, and so on).

The display RAM bit map shows the direct relationship between the display RAM addresses and

the segment outputs and between the bits in a RAM word and the backplane outputs.

Fig 11. Display RAM bit map

GLVSOD\5$0DGGUHVVHVVHJPHQWRXWSXWV6

GLVSOD\5$0URZV

EDFNSODQHRXWSXWV

%3

DDD

FROXPQV

URZV