TDA8920C_2 © NXP B.V. 2009. All rights reserved.

Product data sheet Rev. 02 — 11 June 2009 18 of 39

NXP Semiconductors

TDA8920C

2 × 110 W class-D power amplifier

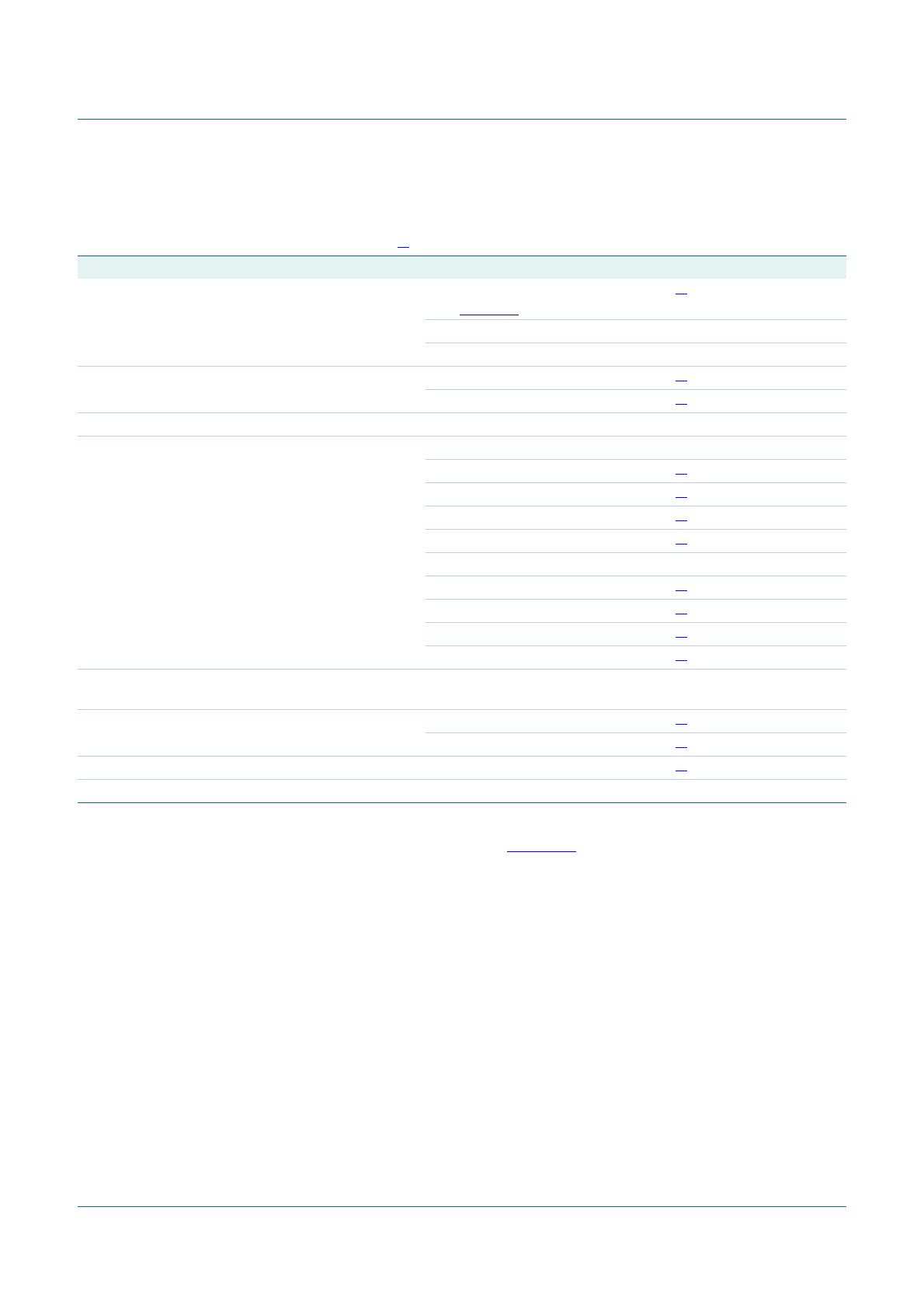

13.3.2 Bridge-Tied Load (BTL)

Maximum output power:

(3)

Maximum output current internally limited to 9.2 A:

(4)

Where:

• P

o(0.5 %)

: output power at the onset of clipping

• R

L

: load impedance

• R

DSon(hs)

: high-side R

DSon

of power stage output DMOS (temperature dependent)

• R

DSon(ls)

: low-side R

DSson

of power stage output DMOS (temperature dependent)

• R

sL

: series impedance of the filter coil

• V

P

: single-sided supply voltage or 0.5 × (V

DD

+ |V

SS

|)

• t

w(min)

: minimum pulse width (typical 150 ns, temperature dependent)

• f

osc

: oscillator frequency

Remark: Note that I

o(peak)

should be less than 9.2 A; see Section 8.3.2.I

o(peak)

is the sum

of the current through the load and the ripple current. The value of the ripple current is

dependent on the coil inductance and the voltage drop across the coil.

13.4 External clock

To ensure duty cycle-independent operation, the external clock frequency is divided by

two internally. The external clock frequency is therefore twice the internal clock frequency

(typically 2 × 350 kHz = 700 kHz).

If several class-D amplifiers are used in a single application, it is recommended that all the

devices run at the same switching frequency. This can be achieved by connecting the

OSC pins together and feeding them from an external oscillator. When using an external

oscillator, it is necessary to force pin OSC to a DC level above SGND. This disables the

internal oscillator and causes the PWM to switch at half the external clock frequency.

The internal oscillator requires an external resistor R

OSC

, connected between pin OSC

and pin VSSA. R

OSC

must be removed when using an external oscillator.

The noise generated by the internal oscillator is supply voltage dependent. An external

low-noise oscillator is recommended for low-noise applications running at high supply

voltages.

P

o 0.5%()

R

L

R

L

R

DSon hs()

R

DSon ls()

++

-------------------------------------------------------------------

2V

P

1t

wmin()

0.5 f

osc

×–()××

2

2R

L

-----------------------------------------------------------------------------------------------------------------------------------------------------------

=

I

opeak()

2V

P

1t

w min()

0.5 f

osc

×–()×

R

L

R

DSon hs()

R

DSon ls()

+()2R

sL

++

-------------------------------------------------------------------------------------------

=