Si3453

14 Rev. 1.3

4.4. Disconnect Detection

The port current is continuously monitored by the Si3453. The Si3453 can dynamically change the measurement

scale to achieve accuracy over a wide range of currents.

As defined in the IEEE 802.3 PoE standard, the PSE should disconnect if the port current is less than a nominal

7.5 mA for more than 350 ms.

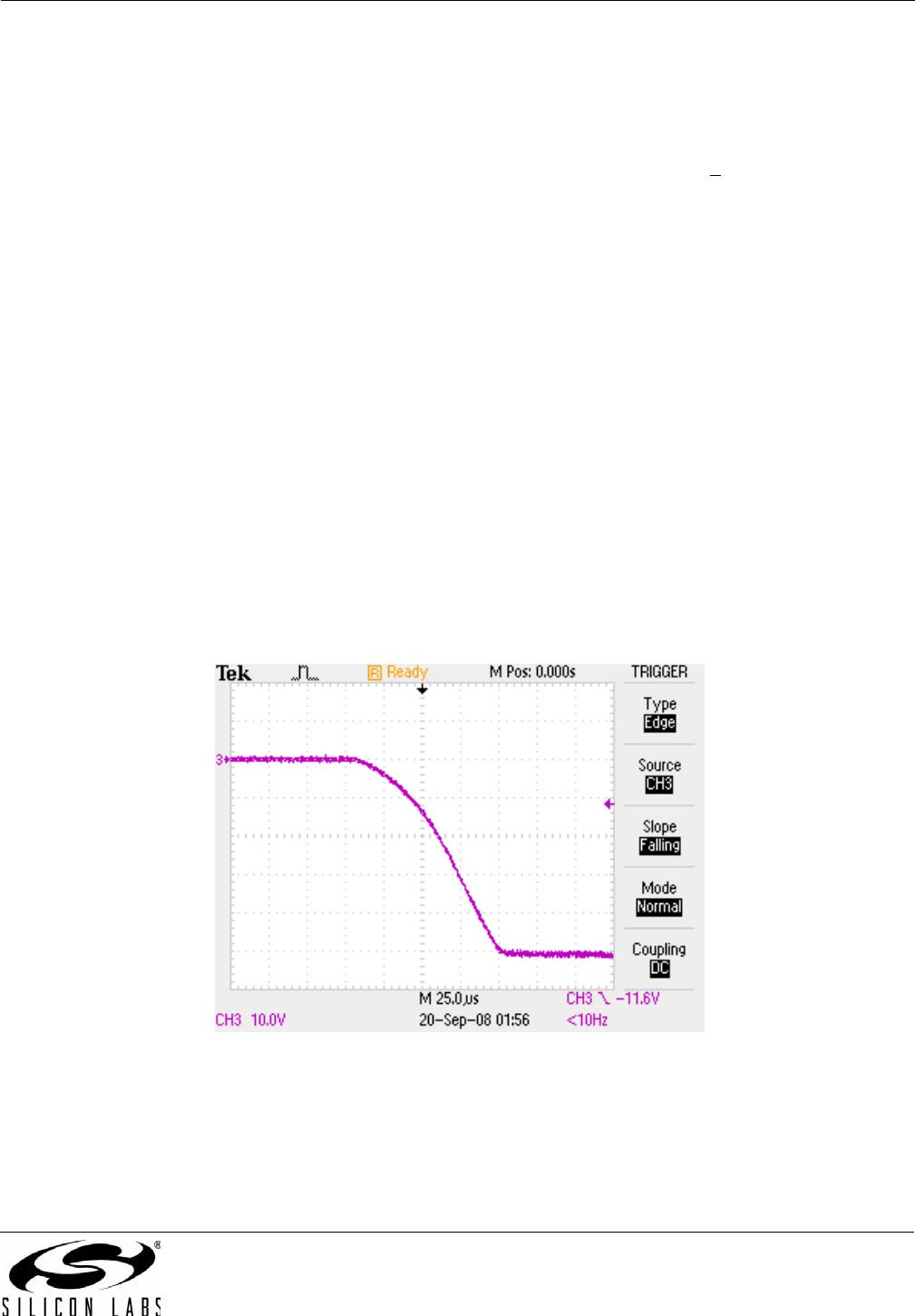

4.5. Transient Voltage Surge Suppression

The Si3453 features robust on-chip surge protectors on each port; this is an industry first. This unique protection

circuitry acts as an active device that can withstand lightning-induced transients as well as large ESD transient

events. When the port voltage exceeds its protection limit and the current reaches a triggering threshold, current is

shunted from the port to the ground pins.

Internal circuitry is provided to protect the line outputs from externally-coupled fault currents. These are transient

currents of up to 5 A peak.

The operation of the protection circuits depends on the operating mode of the channel switch and the direction of

the fault current. The clamping operation is performed on the detect pin.

The switch itself will also be protected by the current limit. If the transient lasts long enough to heat up the die, then

the temperature sense circuit will shut off the switch, and all the fault current will flow through the clamp diode.

4.6. Temperature Sense

A temperature sense signal is used in conjunction with the current limit status signals from the gate drive blocks.

Any channel that is generating excess heat is assumed to be operating in current limit mode, with both high voltage

drop and high current.

If the port is in PoE mode, an overload will generally not result in thermal shutdown before the 60 ms I

CUT

period. If

the port is in PoE+ mode, an overload may cause the port to shut down prior to the 60 ms I

CUT

period. In either

case, the event is reported as I

CUT

. The faster shutdown in PoE+ mode is consistent with and specifically allowed

by the 802.3at draft and provides much more robust overload protection than is possible with external FETs.

In addition, there is a thermal shutdown if the package temperature exceeds 120 °C. If this threshold is reached, all

output drivers are turned off and detection modes are disabled. This secondary threshold limit guards against the

possibility that the overheating is not caused by a driver operating in current limit.

4.7. Port Measurement and Monitoring

VEE monitoring in conjunction with port current monitoring allows measurement of port power. Port power

monitoring, dynamic power allocation via LLDP*, and port power policing allow efficient power supply sizing.

The Si3453 is factory-calibrated and temperature-compensated for the following measurements:

Port current measurement. These measurements are auto-ranged and scaled to a 16 bit number at 100 µA per

bit. Port current accuracy is ±4% ± 2 mA.

V

EE

is measured with a scale of 64 V. The measurement is reported as a 16-bit number scaled at 1 mV per bit.

V

EE

measurement accuracy is ±4% over the valid V

EE

range.

*Note: LLDP = Link Layer Discovery Protocol. Refer to IEEE 802.3at (draft) and IEEE 802.1AB for more information.