Si3453

4 Rev. 1.3

1. Electrical Specifications

Unless noted otherwise, specifications apply over the operating temperature range with VDD = +3.3 V and

VEE = –48 V relative to GND.

VDD pins should be electrically shorted. AGND pins, DGND, GND12, and GND34 should be electrically shorted

(“GND”). VEE, VEE1, VEE2, VEE3, and VEE4 should be electrically shorted (“VEE”).

VPort for any port is measured from GND to the respective VOUTn.

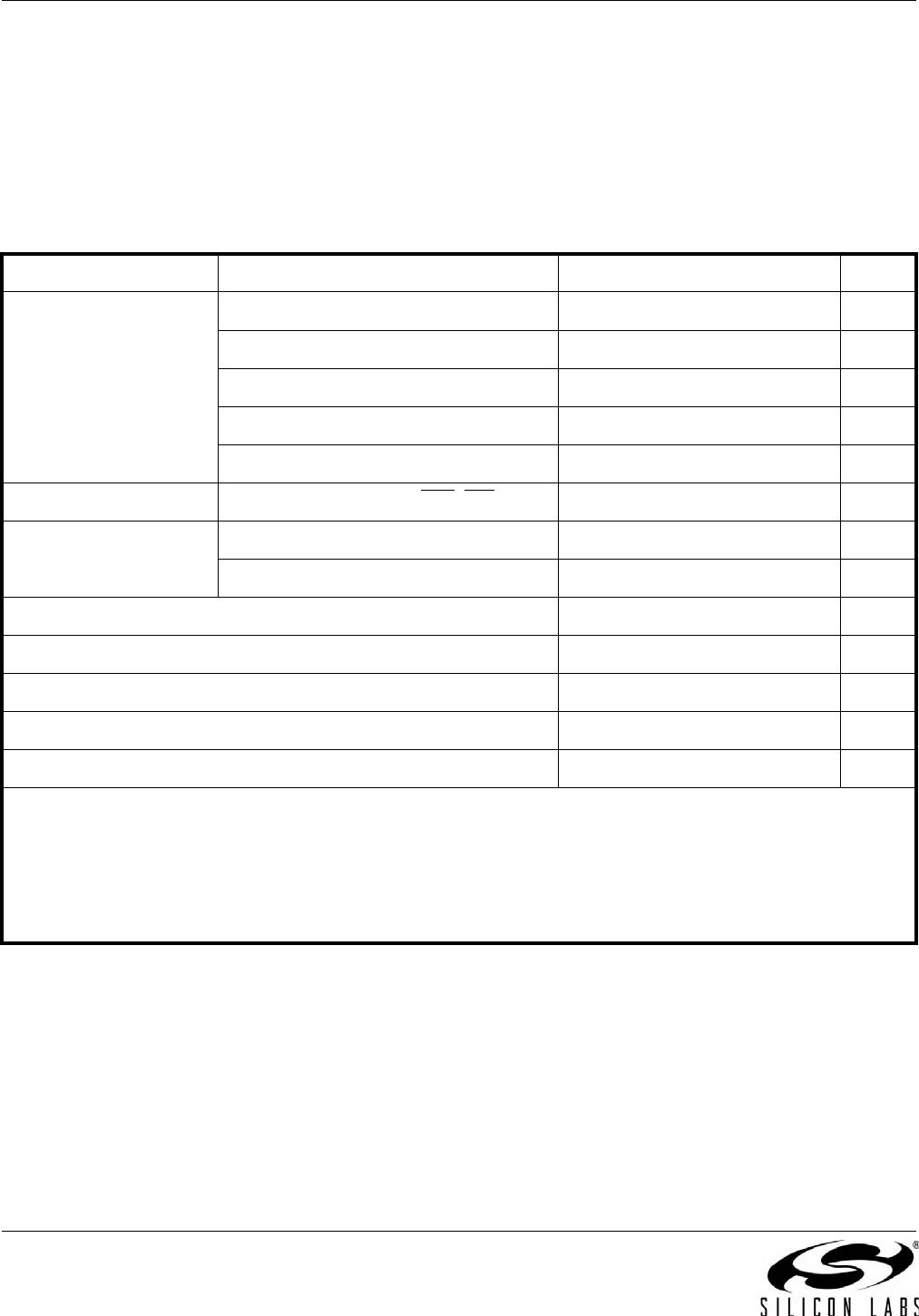

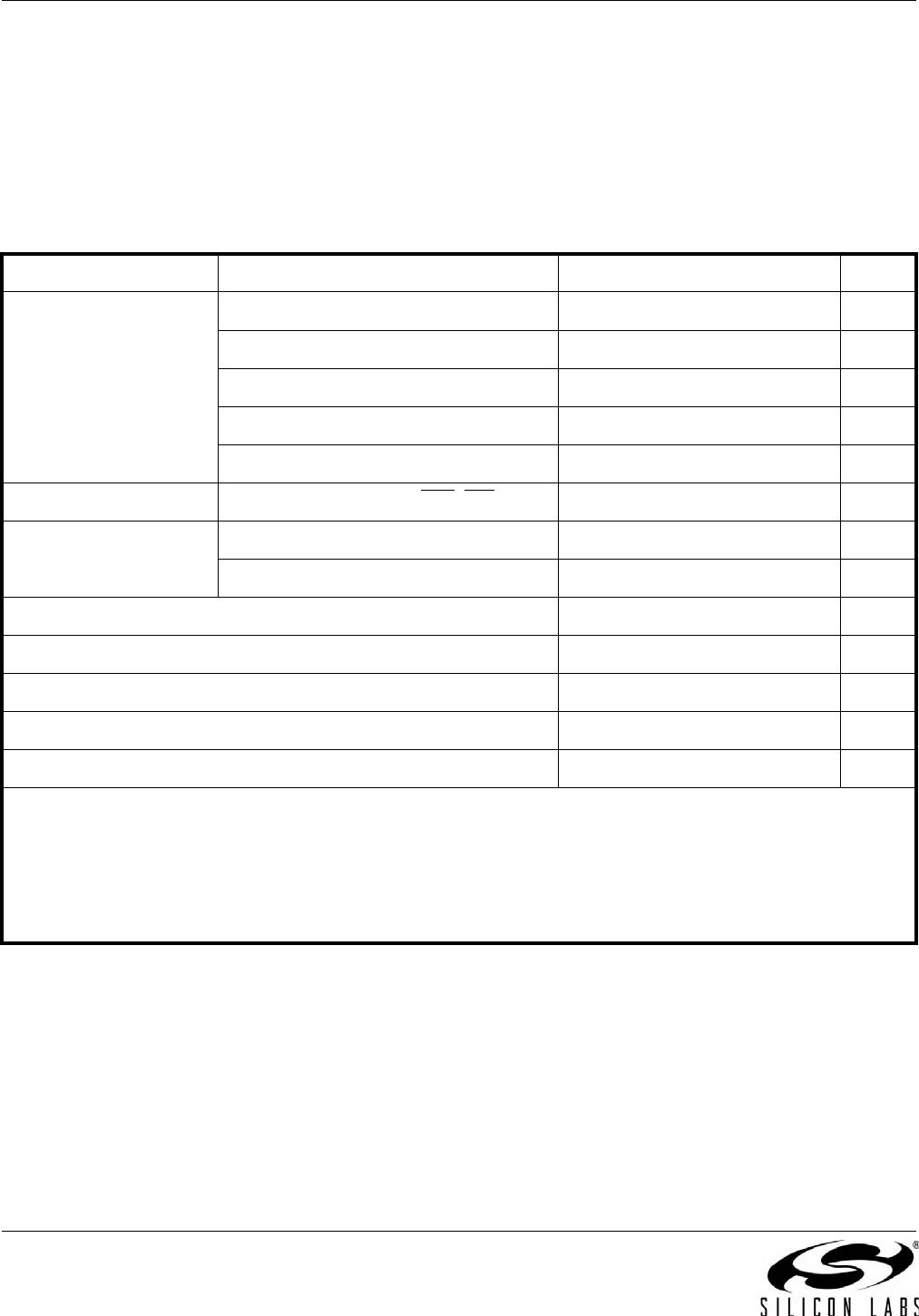

Table 1. Absolute Maximum Ratings

1

Type Description Rating Unit

Supply Voltages

VEE to GND –62 to +0.3 V

VDD to GND –0.3 to +3.6 V

VDD1 to VDD2 –0.3 to +0.3 V

Any VEE to any other VEE –0.3 to +0.3 V

Any GND to any other GND –0.3 to +0.3 V

Voltage on Digital Pins

SDA, SCL, ADn, RST

, INT (GND – 0.3) to (VDD + 0.3) V

Voltage on Analog Pins

VREF, AIN, AOUT, RBIAS, OSC (GND – 0.3) to (VDD + 0.3) V

VOUTn, DETn (VEE – 0.3) to (GND + 0.3) V

DETn Peak Currents During Surge Events

2

±5 A

Maximum Continuous Power Dissipation

3

1.2 W

Maximum Junction Temperature

125 °C

Ambient Storage Temperature

–55 to 150 °C

Lead Temperature (Soldering, 10 seconds Maximum)

260 °C

Notes:

1. Functional operation should be restricted to those conditions specified in Table 2. Functional operation or specification

compliance is not implied at these conditions. Stresses beyond those listed in absolute maximum ratings may cause

permanent damage to the device.

2. See IEEE Std 802.3-2005, clause 33.4, for a description of surge events.

3. If all ports are on with 600 mA load, the power dissipation is <1.2 W. At 85 °C ambient with the expected 32 °C/W

thermal impedance, the junction temperature would be 123.4 °C, which is within the 125 °C maximum rating.