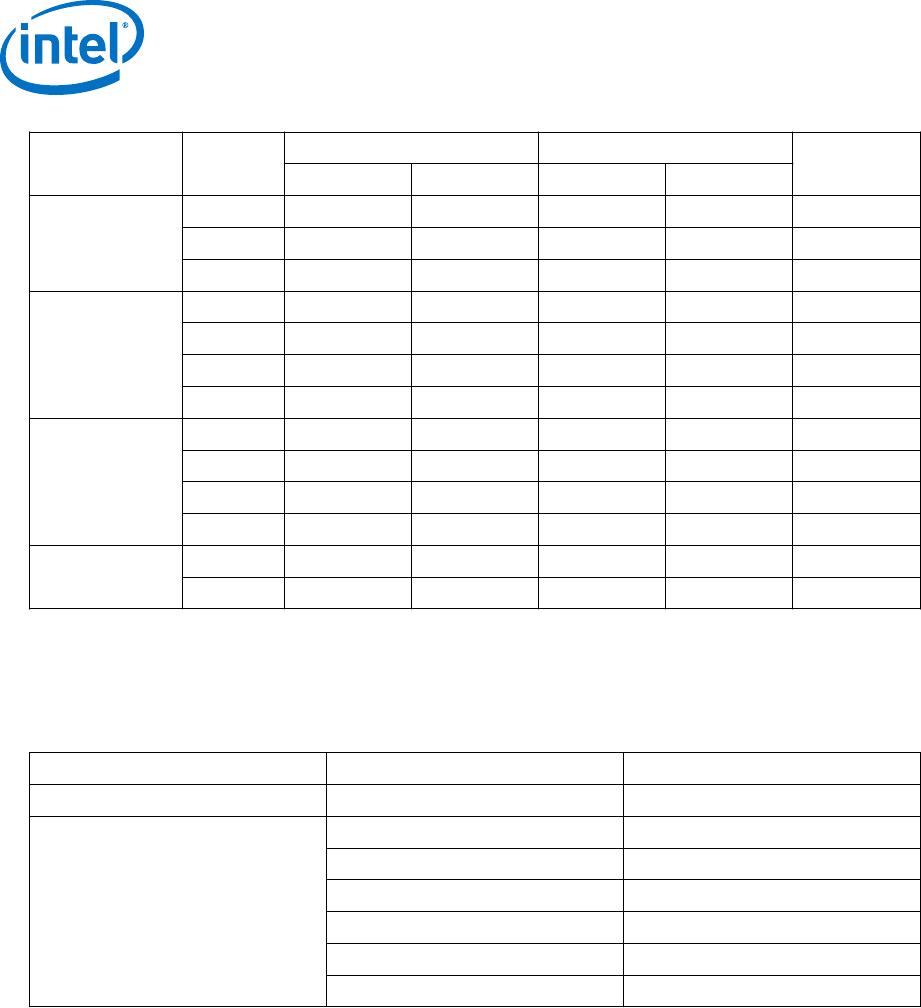

Variant

Member

Code

M10K MLAB

Total RAM Bit

(Kb)Block RAM Bit (Kb) Block RAM Bit (Kb)

Cyclone V GT D5 446 4,460 679 424 4,884

D7 686 6,860 1338 836 7,696

D9 1,220 12,200 2748 1,717 13,917

Cyclone V SE A2 140 1,400 221 138 1,538

A4 270 2,700 370 231 2,460

A5 397 3,970 768 480 4,450

A6 553 5,530 994 621 6,151

Cyclone V SX C2 140 1,400 221 138 1,538

C4 270 2,700 370 231 2,460

C5 397 3,970 768 480 4,450

C6 553 5,530 994 621 6,151

Cyclone V ST D5 397 3,970 768 480 4,450

D6 553 5,530 994 621 6,151

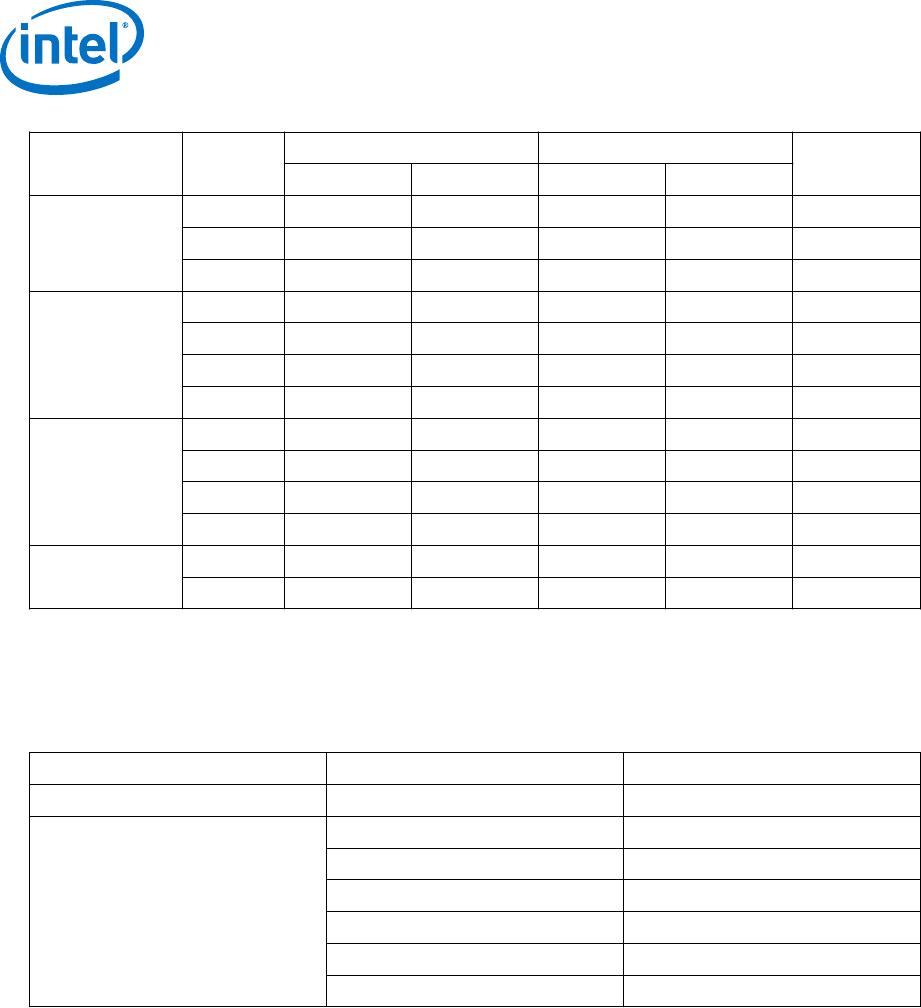

Embedded Memory Configurations

Table 19. Supported Embedded Memory Block Configurations for Cyclone V Devices

This table lists the maximum configurations supported for the embedded memory blocks. The information is

applicable only to the single-port RAM and ROM modes.

Memory Block

Depth (bits) Programmable Width

MLAB 32 x16, x18, or x20

M10K 256 x40 or x32

512 x20 or x16

1K x10 or x8

2K x5 or x4

4K x2

8K x1

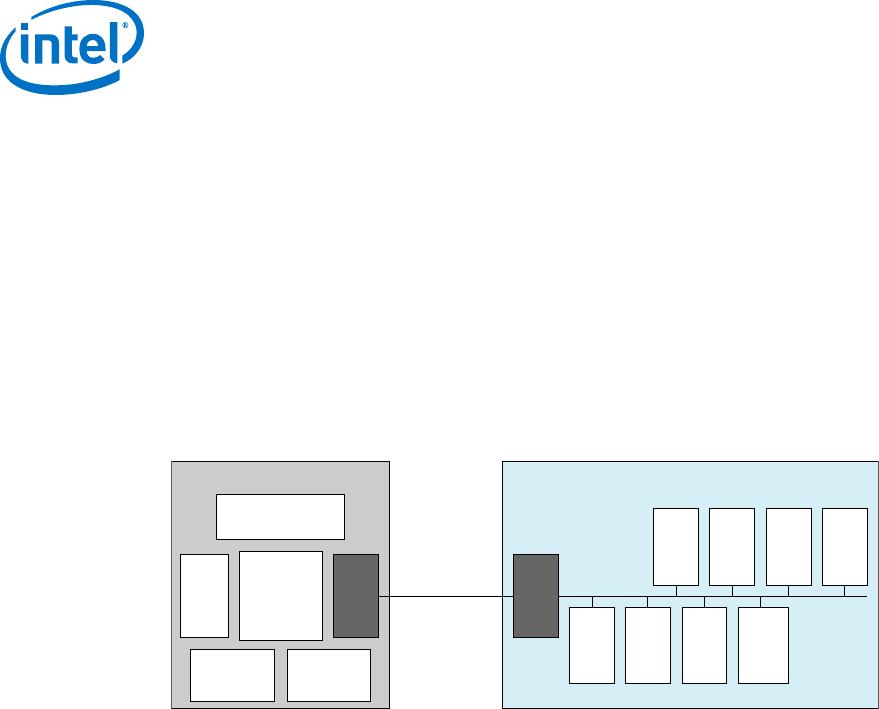

Clock Networks and PLL Clock Sources

550 MHz Cyclone V devices have 16 global clock networks capable of up to operation.

The clock network architecture is based on Intel's global, quadrant, and peripheral

clock structure. This clock structure is supported by dedicated clock input pins and

fractional PLLs.

Note: To reduce power consumption, the Intel Quartus Prime software identifies all unused

sections of the clock network and powers them down.

Cyclone V Device Overview

CV-51001 | 2018.05.07

Cyclone V Device Overview

22